处理器一条指令需要几个时钟周期

编程实验

描述

时钟周期简介

时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。时钟周期是一个时间的量。时钟周期表示了SDRAM所能运行的最高频率。更小的时钟周期就意味着更高的工作频率。

时钟周期是同步电路中时钟基础频率的倒数。它以时间动作重复的最小周期来度量,度量单位采用时间单位。在单个时钟周期内(现代非嵌入式微处理器的这个时间一般都短于1纳秒),逻辑零状态与逻辑一状态来回切换。由于发热和电气规格的限制,周期里逻辑零状态的持续时间历来要长于逻辑一状态。

CPU时钟周期概述

在微程序控制器中,时序信号比较简单,一般采用节拍电位——节拍脉冲二级体制。就是说它只要一个节拍电位,在节拍电位又包含若干个节拍脉冲(时钟周期)。节拍电位表示一个CPU周期的时间,而节拍脉冲把一个CPU周期划分为几个叫较小的时间间隔。根据需要这些时间间隔可以相等,也可以不等。

指令周期是取出并执行一条指令的时间。

指令周期常常有若干个CPU周期,CPU周期也称为机器周期,由于CPU访问一次内存所花费的时间较长,因此通常用内存中读取一个指令字的最短时间来规定CPU周期。这就是说,一条指令取出阶段(通常为取指)需要一个CPU周期时间。而一个CPU周期时间又包含若干个时钟周期(通常为节拍脉冲或T周期,它是处理操作的最基本的单位)。这些时钟周期的总和则规定了一个CPU周期的时间宽度。

处理器一条指令需要几个时钟周期

对于软件工程师来说,印象流我们可能会觉得执行一条指令一个时钟周期嘛,一条指令算是一个最小的原子操作,不可能再细分了吧。

如果看看诸如《see mips run》,《arm体系架构》等书籍就会了解到,这个问题可没这么简单了,因为处理器设计中使用了流水线技术。

一条指令还是相当复杂的,处理器在一个时钟周期内肯定是完不成的,可能需要好多个时钟周期来完成执行。如果这样让处理器执行完一条指令,再去执行另一条,处理器的效率是很低的,假如一条指令是5个时钟周期完成,对于500MHZ的处理器串行运行指令,1秒内取指100000000次。

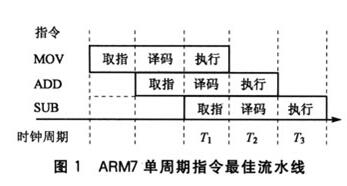

因此处理器引入了流水线技术,将一条指令划分为多个功能,由不同的功能部件来执行,并且这些功能部件可以并行工作。下面是一个arm7的三级流水线运行图。

流水线划分为取指 译码 执行,但并不是仅需3个时钟周期即执行完指令。因为执行单元模块的操作较多,可能需要多个周期,取指 译码一般是一个时钟周期,这样可以看出虽然一条指令完成需要多个时钟周期,但是总体来说看在每个时钟周期都有一条指令开始取指。如果我们的处理器是500MHZ,则1秒内取指了500000000次。

不同的处理器设计时流水线级数不一样,现在主流的有三级 五级 七级,增加流水线级数,简化流水线的各级逻辑,可以提高处理器的性能。

回答咱们开头的问题也就明白了,一条指令需要的时钟周期还真不固定,这得看处理器的流水线级数,也得看该指令的复杂度,在执行阶段需要几个时钟周期。

对于流水线各级具体工作这里就不细说了,网上文章很多,毕竟咱们是做软件的,硬件点到为止,流水线各级工作是有处理器内部逻辑单元来完成的,对于软件来说都是不可见的,软件可操作的最小原子操作就是指令。

不过呢,处理器的流水线技术在有一个事情对咱们软件造成了影响,那就是PC值。

据我了解的处理器流水线设计,前三级基本都是取指 译码 执行。处理器的PC寄存器中存储的是处理器的取指地址,根据上述流水线机制,而我们的处理器执行的指令地址是落后于要去预取的指令的地址,落后2个时钟周期。

也就是说我们在取了第一条指令后,等该指令到了执行阶段时,我们的处理器其实已经预取了往后的第二条指令了。

对于32位处理器,一条指令占据4字节。这也就是PC值 = 当前指令地址 + 8的根本原因啦。

-

STM8L执行一条语句大概需要几个时钟周期?2024-05-06 327

-

时钟周期、机器周期、指令周期介绍2025-11-17 113

-

时钟周期和指令周期的区别是什么2025-11-21 70

-

详细解读|时钟周期、机器周期、指令周期、总线周期2016-12-01 6408

-

请问有谁知道2812一条单指令究竟用了几个时钟周期?2018-06-06 8108

-

单片机 时间周期、机器周期、指令周期详解2021-01-19 8196

-

一条指令的执行需要多少个时钟周期2021-08-04 2003

-

到底一条指令的执行需要多少个时钟周期呢2021-10-28 5389

-

时钟周期/器械周期/指令周期的关系是什么2022-01-06 1211

-

多周期处理器是指什么2022-01-10 1475

-

关于ARM的指令周期请诸位指教2022-06-29 4088

-

指令周期,什么是指令周期2010-03-24 6661

-

PIC中的振荡周期、时钟周期、机器周期、指令周期2021-11-16 1574

-

单片机几个周期的区别2021-12-01 782

-

AvR单片机for循环需要几个指令周期2023-12-26 2180

全部0条评论

快来发表一下你的评论吧 !