信号调理产品电路设计与寄存器配置

描述

在高速信号电路设计中,TI的信号调理产品被广泛使用。其中retimer类产品涉及到寄存器配置,因此相比较而言,它的使用最为复杂。本文将以DS125DF1610为例,具体讲解retimer类产品的电路设计与寄存器配置。

下图是DS125DF1610产品资料中的典型应用图。

硬件电路设计可以概括为四个关键部分:

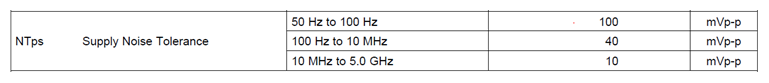

1. 电源:TI的retimer产品供电方式都非常简单,一般只需2.5V单电源,像DS125DF111还可以支持单3.3V供电。从下表可以看到,retimer对电源噪声性能要求不高,通常情况下可以采用DC/DC电源方案,在供电管脚增加适当的滤波电容即可。

另外,电源选型时还需要注意功耗问题,在芯片资料中都会给出各种功能组合下的功耗,那么我们就可以根据实际应用计算出最大的功耗,作为电源方案选择的一个参考标准。

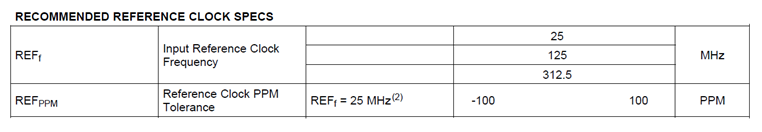

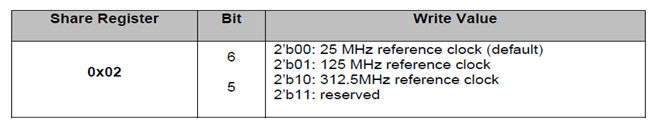

2. 时钟:外部参考时钟主要是给retimer内部VCO提供一个校准的参考,它只要求频率的精度在+/-100ppm范围之内即可,而对phase noise没有特别的要求。需要注意的是不同的retimer支持的时钟频率和电平有区别。像DS125DF1610可以支持25 MHz,125 MHz和312.5MHz的单端或差分输入,而大部分10G retimer,比如DS125DF111只支持25MHz的单端输入。设计时需要根据数据手册来进行选择。

3. AC耦合电容:高速信号传输通常需要做AC耦合,考虑到布板的方便性以及信号的完整性,TI部分retimer产品在芯片内部会集成该耦合电容,这个需要设计时从产品手册上去确认,避免遗漏或者重复添加。

4. I/O口耐压:如前面所讲,TI retimer一般都是2.5V单电源供电,因此需要注意它的I/O口耐压问题。为了方便与板上主控芯片的对接,retimer内部对I2C,RESET和INTERRUPT口做了特殊处理,都允许直接上拉到3.3V,这个可以从典型应用图上看到。而其他I/O口就需要注意不能超过电源供电电压。

高速信号电路设计还有一个非常重要的地方就是PCB layout,它直接影响信号传输中的性能。在layout时,我们需要注意:

信号、电源和地层的合理分配,信号尽可能的远离噪声源;

保持高速差分线的对称,以及阻抗控制在100Ω±5%以内;

避免差分线的剧烈弯折,使用45°或者曲线弯折;

保证不同差分线对间的skew匹配。

沿信号路径,避免参考平面的不连续而引起阻抗的变化,注意电流返回路径;

AC耦合电容最大选择0402封装,尽可能的保证走线宽度一致,尽量减少过孔数量;

选择的连接器要能满足最高速率性能要求。

在做电路设计时,只要注意到上面提到的这些地方,应该就可以保证芯片正常上电工作和传输链路上信号的性能,接下来我们需要做的是寄存器配置。需要注意,上电后系统最佳的配置顺序是先ASIC,后retimer。这是因为如果retimer先于ASIC 配置,那么这时ASIC高速I/O口发送的数据不稳定,而retimer只要检测到有信号后,就会尝试去锁定,此时自适应出来的参数就不是最优的。

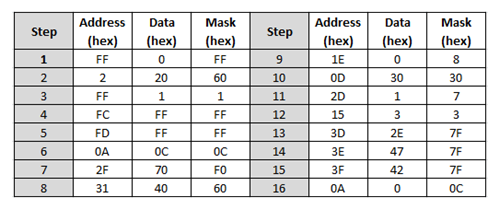

下面还是以DS125DF1610为例,假设外部采用125MHz的参考时钟,系统需要兼容12.5Gbps和6.25Gbps速率,下表就是我们常用到的配置流程。

在讲解retimer配置的具体步骤之前,需要了解什么是掩码方式写入。因为在配置寄存器时,只能对需要配置的bit位进行修改,而其他bit位要保持默认值不变。

以step 2为例,需要对寄存器0x02进行掩码为0x60的写入操作,写入值为0x20。首先,掩码0x60展开后只有bit 5和6为1,也就是说我们只能修改寄存器0x02的bit 5和6,写入的值为数据0x20相对应的bit位值,而寄存器其他bit位要保持出厂默认值不变。

下面将详细说明每步配置的作用。

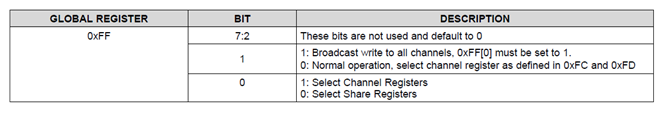

Step 1:retimer内部寄存器一般分成两类:shared寄存器和channel寄存器。像retimer的一些全局信息,比如chip ID,外部参考时钟的选择等等都在shared寄存器里。因此在配置之前,要清楚将要操作的是哪类寄存器。寄存器0xFF的bit 0就是进行选择。

Step 2:在step 1中已经选定操作的是shared寄存器,所以接下来对0x02寄存器的操作就是选择外部参考时钟,根据datasheet给出的值选中即可。

Step 3~5:一般shared寄存器需要操作的就是选择参考时钟,其它的配置都在channel寄存器中。首先Step 3选中channel寄存器,step 4和5选择哪些channel将同时被修改。如果所有channel采用相同配置,最简便的方法就是将0xFF的bit 1置为1,那么将会以广播的方式修改所有通道,而不用再去配置channel选择寄存器。

Step 6:配置channel寄存器前,将CDR置于复位状态,以保证配置没有完成之前,retimer不会尝试去锁定。

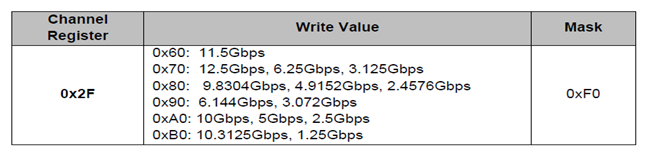

Step 7:CDR锁定速率有两种配置方式。如果系统速率是常见的标准速率,比如下表中列举的值,那么我们直接选择相应的寄存器值即可。但如果不是标准速率,比如11.3Gbps,那么我们就需要采用手动计算VCO工作频率,具体步骤可以参考DS125DF1610产品资料的8.3.2章节。

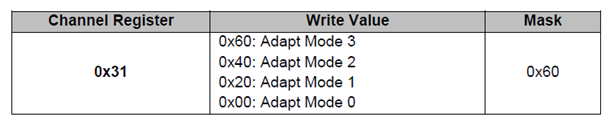

Step 8:根据CDR锁定时CTLE和DFE自适应算法的区别,通常有四种工作模式可选。如下表,可以根据调试情况,通过寄存器0x31选择其中一种。

四种模式具体区别如下:

Mode 0:手动模式,CTLE和DFE均需要手动设置;

Mode 1:CTLE自适应,而DFE需要手动设置;

Mode 2:CTLE首先自适应到一个最优的设置,然后DFE再自适应调整;

Mode 3:CTLE首先自适应到一个最低要求的水平,然后DFE自适应到最佳设置,最后CTLE再重新自适应到最佳的水平。

Step 9:根据上一步选择的工作模式确定是否需要使能DFE。

Step 10~15:高速接口都是只有接收侧参数可以自适应,发送侧参数需要手动设置。Step 10到15就是用于配置retimer发送信号幅度,加重和FIR滤波器。

Step 16:释放CDR复位。

通常情况下,完成上面的配置后,retimer就可以正常锁定工作。如果测试中链路上有误码的话,则需要根据实际情况去优化各个参数。

-

如何根据自己设计中的寄存器配置总线定义来生成一套寄存器配置模版2024-03-04 2582

-

寄存器属于时序逻辑电路吗 寄存器是什么逻辑电路2024-02-18 3773

-

寄存器是什么?怎么操作寄存器点亮LED灯?2023-07-21 5471

-

寄存器门电路原理分析2023-07-13 6279

-

配置STM32寄存器控制GPIO点亮LED2022-01-13 1142

-

GPIO寄存器2021-12-08 1401

-

IO口配置常用的8个寄存器 1.62021-11-29 2821

-

GC1064寄存器配置参考文件下载2021-05-21 1067

-

MPC860寄存器配置2011-06-08 1199

-

基于LMH6505的中频信号调理电路设计2010-05-13 897

-

MAXQ3180入门:寄存器配置2010-03-28 1416

-

寄存器,寄存器是什么意思2010-03-08 22414

-

线性移位寄存器2010-01-12 2275

-

时序电路设计串入/并出移位寄存器2009-03-13 6351

全部0条评论

快来发表一下你的评论吧 !