智多晶Tiny_SoC简介和特点

描述

Tiny_SoC简介

RISC-V 是一种基于精简指令集(RISC)原则的开源指令集架构(ISA),其开放性和灵活性使其在嵌入式系统和计算应用中得到了广泛应用。在 FPGA 上实现 RISC-V 处理器,可以充分利用 FPGA 的可编程性和高性能特点,构建定制化的微处理器设计。

智多晶Tiny_SoC是基于RISCV-I指令集设计的一款轻量化软核,集处理器核心、丰富外设与智能中断管理于一体,为开发者提供“开箱即用”的轻量化设计体验!

Tiny_SoC特点

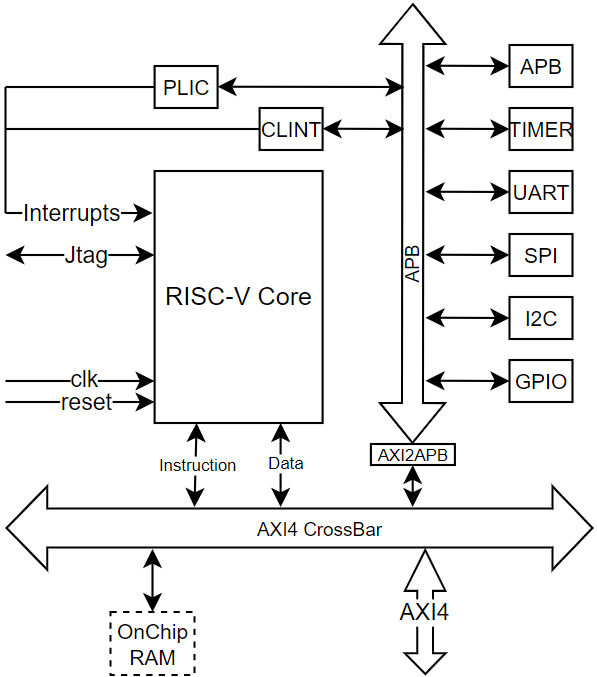

搭载32位RISC-V处理器(RV32-I指令集),5级流水线设计,主频高达120MHz,性能达0.5DMIPS/MHz,集成JTAG调试接口(兼容OpenOCD)。

(*注:根据使用资源占用情况,最高主频会有所变化)

图 1 Tiny_SoC系统框图

资源占用低至1.2K LUTs(默认配置),支持UART、SPI、I2C、GPIO、定时器等常用外设,轻松适配从智能传感器到复杂控制器的多样化场景。

同时提供3路AXI接口+5路APB接口,支持自定义外设扩展,满足个性化开发需求。

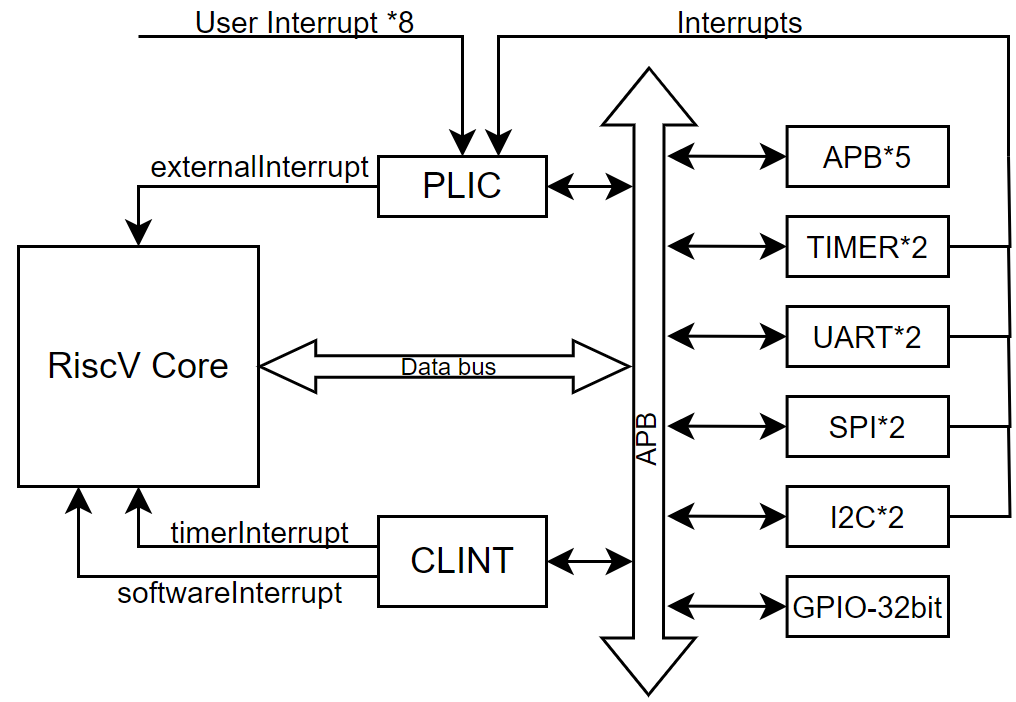

图 2 中断管理图

Tiny_SoC使用

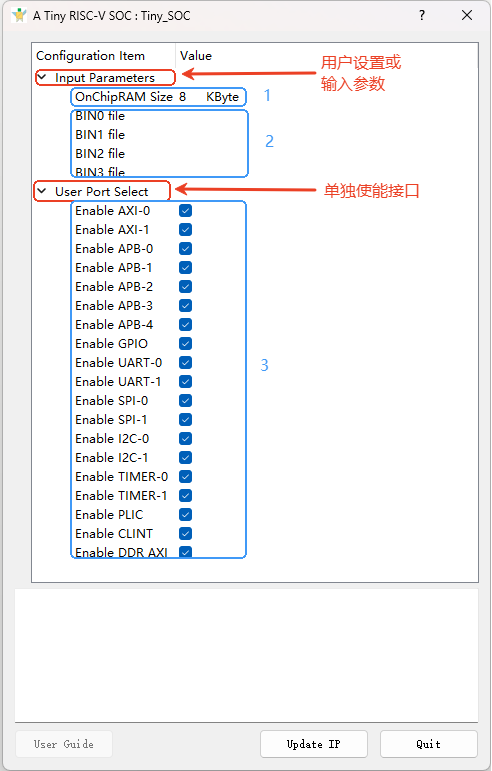

Tiny_SoC有极简的使用界面,根据不同功能分为Input Parameters与User Port Select两大类。

通过IP界面动态选择外设模块(UART/SPI/I2C等),设置片上RAM大小(4KB~512KB),导入预编译程序文件(BIN格式),5分钟完成核心配置。

图 3 IP界面配置

典型应用场景

工业控制:多中断响应+高精度定时器,实现实时电机控制与传感器数据处理。

工业相机:高速接口+软核控制器,实现高速数据处理与传感器状态监控。

原型验证:灵活配置外设与接口,实现快速搭建RISC-V开发验证平台。

获取技术文档与demo

技术文档获取:Tiny_SoC已发布,用户可以在HQFPGA IP Manage中打开Tiny_SoC界面查看用户指南,或访问智多晶官网下载Tiny_SoC用户指南。

设计参考案例获取:请联系FAE获取参考设计案例,或在公众号中与我们联系。

-

CAN协议特点简介2021-08-19 2309

-

SOC芯片供电系统简介2021-10-28 2041

-

TencentOS tiny的相关资料推荐2022-01-27 732

-

初探TencentOS-tiny系统2022-02-10 1142

-

tencentos-tiny概述2022-02-11 1678

-

中兴微电子所SOC教程2008-10-29 1077

-

Tiny Switch特性及其应用2009-07-11 1978

-

Windows CE简介、特点及应用2010-01-11 5021

-

太阳能电池板单晶好还是多晶好,都有什么特点_太阳能板单晶和多晶区别在哪里2018-01-30 334739

-

SH/Tiny电机培训套件的特点性能介绍2018-07-23 3877

-

如何使用Zynq SoC硬件加速实现改进TINY YOLO实时车辆检测的算法2020-07-06 1837

-

STM32开发,体验腾讯RTOS-tencentos-tiny2021-12-08 807

-

多晶粒SoC成趋势,UCIe标准助其一臂之力2022-12-14 1548

-

SoC 功能可见性 – Tessent 嵌入式分析简介2023-07-14 530

-

DA14535 SmartBond TINY™ SoC开发套件数据手册2024-05-21 1275

全部0条评论

快来发表一下你的评论吧 !