ICL7650S 2MHz、超级稳定斩波运算放大器应用笔记

描述

概述

ICL7650S Super Chopper-Stabilized Amplifier 提供极低的输入失调电压,并且在时间和温度方面非常稳定。它是行业标准 ICL7650 的直接替代品,具有改进的输入失调电压、更低的输入失调电压温度系数、更低的输入偏置电流和更宽的共模电压范围。所有改进在 Electrical Characteristics 部分以粗斜体突出显示。关键参数在整个商用温度范围内得到保证。Intersil 独特的 CMOS 稳定斩波放大器电路对用户透明,几乎消除了传统的斩波放大器的互调效应、斩波尖峰和超范围锁定问题。斩波放大器通过比较归零放大器中的反相和非反相输入电压来实现其低失调,由交替时钟相位归零。需要两个外部电容器来存储两个放大器归零输入上的校正电位;这些是唯一需要的外部组件。clock oscillator 和所有其他 control circuits 是完全独立的。但是, 14 lead 版本包括使用外部 clock(如果特定应用需要)的规定。此外,ICL7650S 内部还针对单位增益作进行了补偿。

数据表:*附件:ICL7650S 2MHz、超级稳定斩波运算放大器应用笔记.pdf

特性

- 在所有温度范围内保证最大输入失调电压

- 输入失调电压的长期和温度漂移低

- 保证的最大输入偏置电流 10pA

- 极宽的共模电压范围 +3.5V 至 -5V

- 降低的电源电流 2mA

- 保证的最小输出源 / 吸收电流

- 极高增益 150dB

- 极高的 CMRR 和 PSRR 140dB

- 高转换速率 2.5V/μs

- 宽带宽 2MHz

- 单位增益补偿

- 箝位电路可避免过载恢复问题并允许使用比较器

- 输入和输出端的极低斩波尖峰

- 改进的直接替代行业标准 ICL7650 和其他第二来源部件

- 提供无铅 Plus 退火(符合 RoHS 标准)

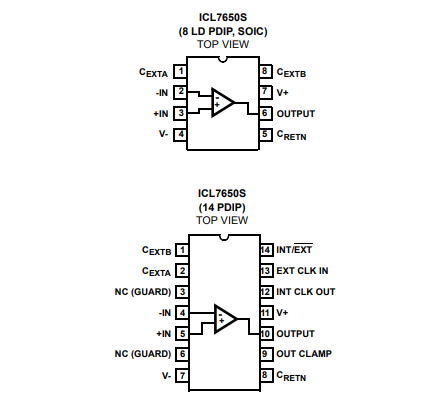

引脚功能图

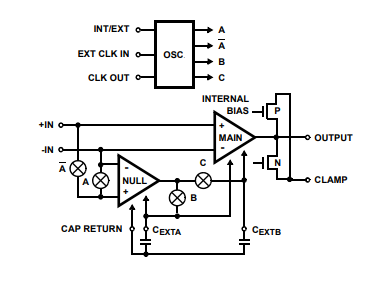

功能框图

ICL7650S 具有一个内部振荡器,提供 200Hz 的斩波频率,可在 14 引脚器件的 CLOCK OUT 引脚上使用。在这些部分还规定了使用 external clock 。INT/EXT 引脚具有内部上拉电阻,可以保持开放状态以进行正常作,但要使用外部 clock,该引脚必须连接到 V- 以禁用内部 clock。然后可以将外部 clock 信号施加到 EXT CLOCK IN 引脚。内部 2 分频提供所需的 50% 输入开关占空比。由于电容器仅在 EXT CLOCK IN 为高电平时充电,因此建议使用 50% 至 80% 的正占空比,尤其是对于较高频率。external clock 可以在 V+ 和 V- 之间摆动。逻辑阈值将低于 V+ 约 2.5V。另请注意,当 INT/EXT 为高电平或开路时,EXT CLOCK IN 引脚上将出现一个约 400 Hz、占空比为 70% 的信号。这是馈送到分频器之前的内部时钟信号。在那些提供选通信号的应用中,可以使用另一种方法来避免电容器在过载期间失衡。如果将选通信号连接到 EXT CLK IN,以便在将过载信号施加到放大器期间为低电平,则两个电容器都不会充电。由于电容器引脚处的漏电流在室温下相当低,因此典型的放大器漂移小于 10V/s,并且可以进行相对较长的测量,而偏移变化很小。

组件选择

两个必需的 capacitor CEXTA 和 CEXTB 根据 clock 或 chopping frequency 具有最佳值。对于预设的内部时钟,正确的值为 0.1F,为了保持斩波频率和归零时间常数之间的相同关系,如果使用外部时钟,该值应大致按比例缩放。高质量的薄膜型电容器(如聚酯薄膜)是首选,尽管陶瓷或其他较低等级的电容器可能适用于许多应用。为了最快地建立初始导通,应使用低介电吸收电容器(例如聚丙烯)。使用陶瓷电容器时,可能需要几秒钟才能稳定到 1V。

静电保护

所有器件引脚均采用输入二极管进行静电保护。但是,应避免强静电场和放电,因为它们会导致二极管结特性下降,从而导致输入漏电流增加。

-

运算放大器2014-04-23 5053

-

运算放大器类型总结2019-09-26 4149

-

ICL7650S pdf datasheet (2MHz,2009-01-07 1063

-

LTC1049型具有内电容低功耗斩波稳定运算放大器2008-02-27 1134

-

自动归零稳定斩波的运算放大器2009-01-15 5928

-

斩波稳定运算放大器的新应用2017-05-05 1471

-

ICL7650和ICL7653斩波稳定放大器的数据手册免费下载2019-04-08 2125

-

ICL7650S超级斩波稳定放大器的中文数据手册免费下载2019-05-22 2499

-

如何将斩波稳定运算放大器应用到各种测量应用中2021-05-28 3762

-

MT-055: 斩波稳定(自稳零)精密运算放大器2021-03-21 1755

-

AN9-新型斩波稳定运算放大器的应用考虑和电路2021-04-19 936

-

LTC1052CS-斩波稳定运算放大器(CSOA)2021-05-08 956

-

运算放大器特性术语应用笔记2023-11-28 829

-

应用笔记1604:去补偿运算放大器2024-09-29 410

全部0条评论

快来发表一下你的评论吧 !