图文并茂Layout对开关电源的重要性

描述

前言

小弟起步比较低,没有什么系统的学习,以前以为了解器件,学好原理就行,后来开始自己Layout才发现,画板对开关电源的重要性,因为小弟Layout自学为主,碰到的实际问题比较多。 如今的电源市场,拼体积、拼价格、拼性能,如何做到这3点就需要一个经验丰富的Layout工程师。

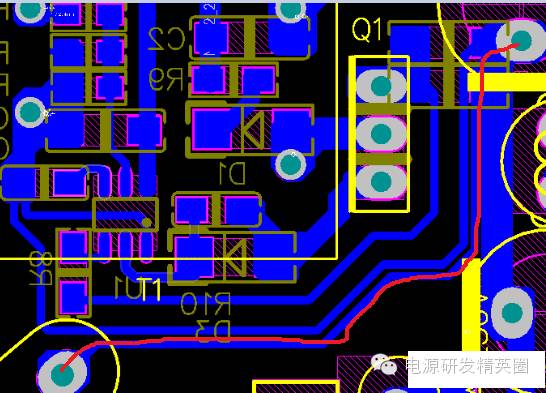

1、静电打坏IC。1.1 VCC电容跟VCC脚越近越好。如下图VCC电容与IC脚太远,静电和耐压都会打坏IC,当然这还要看芯片的抗ESD能力。

1.2单点接地,静电和耐压的回路是一样的,首先我们搞清楚它的回路基本就清晰了,主要2个部分,Y电容,变压器初次级寄生电容。所以这2个器件的地在允许的情况下尽量单点接地,防止打坏IC。

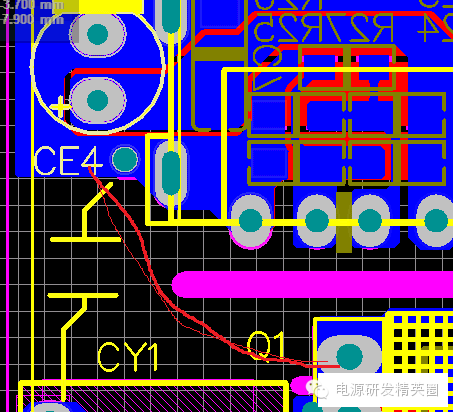

1.3 下面这个最郁闷了,10KV空气没事,15KV挂了,直接炸机,最后调到怕了。后来师傅出了个注意拉窗帘关灯在下图红色部分,Y电容的地一个欢快的小火花颠到了MOS,也就是说15KV要更远的距离,后来把开槽又拉了一部分装绝缘片隔离OK了。

1.4 放电针,不要小看了一个小小的放电针,关键的时候大作用,我有实际看过,如下图在一个黑暗的房间内,打15KV静电,两端放电拉弧产生一个火花消耗掉。要注意安规距离哦。

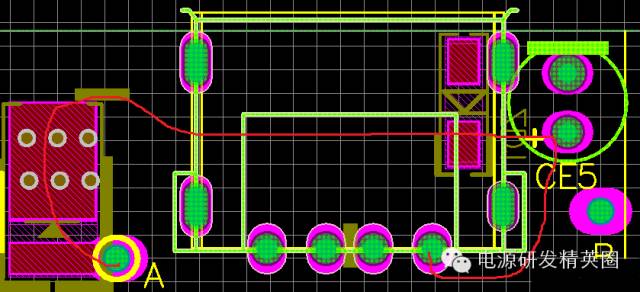

2.Layout对温度的影响。一个画板经验丰富的工程师和一个比较业余的做出来的温度相差10-20度你信嘛,我信了。2.1肖特基温度高,这么办换封装加电流改匝比换品牌,其实Layout也是可以解决的,把肖特基阳极接到母座上,利用母座散热肖特基温度可以下来10度作用。

2.2接着上面那附图,肖特基温度下来了,母座有所提高,变压器和MOS靠母座太近,也可以理解为功率器件之间距离太近,大家知道变压器MOS肖特基啊这些功率器件,在越恶化的环境中性能越差导致温度更高。如下图2者分开和靠近,肖特基和内置MOS的IC 温度相差7度。

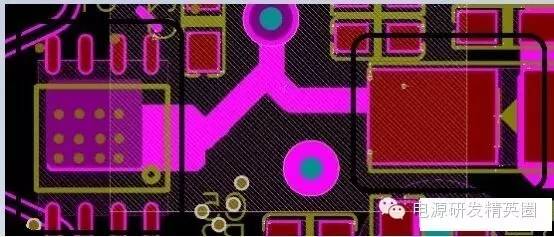

2.3利用一切可利用的散热,经常听到某IC,FAE说我们这颗IC温度100度自己实际做出来120度,这就看画板了。车充,开窗,加厚铜箔,利用负极弹片把热导出。 原本125度,上面3点加进去降低20度你信嘛我信了。Q2同步整流,开窗直接接到负极弹片,Q1开关管,U1IC原理Q1Q2。同步2OZ。

130度的图也上一下。这个板 Q1 125度 Q2 134度 IC 120度 电感120度。

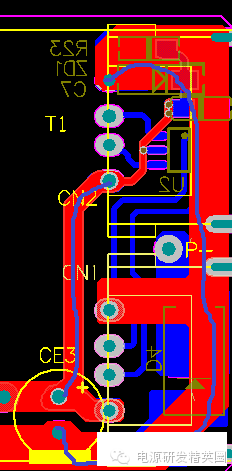

3、纹波大家都知道影响这一点的就是减小电容的ESR,加大容量,加差模电感减小纹波电流组成π滤波。上面说到,降低成本,办法总比问题多,先检查板子。,先看下面这个板子,CN1纹波90mV,CN2纹波150mV。仔细看下面蓝色线勾勒出来的地方环路面积太大,把CE3放在2个USB的中间,纹波都降到100mV,实际有困难的话,可以在CN2端再加一个小电容。

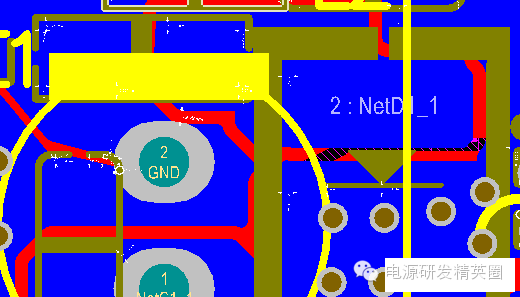

不要超捷径要按顺序走,看下图,电流的方向直接忽略的电容的地,纹波近300mV,我们试着把变压器的地接到C4地。再看电流的走向一个完整的回路,纹波降到73mV。

在必须加π滤波的时候也要注意。差模电感前面的电容要大于或者等于或者的容量,否则容易引起震荡。

整流肖特基要靠近滤波电容否则也容易产生震荡,有碰到一次严重的高压炸机。就是下面这幅图曾经把我炸的心力憔悴。

4、EMI 日常中我们调试无非就是吸收,加共模,X电容,变压器屏蔽。其实画板也可以解决很多问题。4.1 MOS与变压器太近。传导NG,这很容易分辨,平均值很多地方超峰峰值也很多地方超。把MOS和LN 拉开距离基本就解决。

4.2 变压器和LN太近。同样 传导NG,峰峰值平均值很多地方超,往往基于结构的弊端没有办法而为之。是的变压器加屏蔽可以解决,可以试着把变压器反馈和次级反着绕。一般也能解决这一成本就省下来了。

4.3Y电容的接点。如下图Y电容的地直接接大电容的地还是变压器的地2种效果或者输出的低还是正,这个没有硬指标完全看实际效果,在很多时候还是很明显的效果,这里聊一下Y电容最好还是加充电器最好还是加上可以减少纹波噪声,减少手机干扰,适配器的话就看情况了,比如机顶盒加了反而会有干扰。

4.4 车充 比较明显的一点就是,续流二极管的阳极接输入点解的地效果还是很明显的。

不要去用母座作为走线,阻抗大影响效率,有做过实验影响0.5个点。

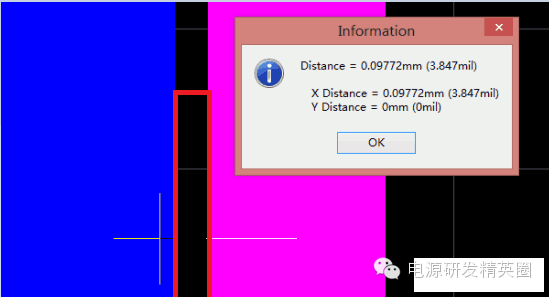

海拔5000m,目前我们做认证就是CCC碰到过着这个要求,主要区别就是空气爬电,初次级都要满足6.4mm

线要跟半边距离大于0.8mm,给大家看一张图,几乎贴板了,实物成这样了只有0.4造成过电流能力不足。

最短距离8.5左右,当时的绝缘片只包到MOS,G极。

-

ATX电源电路分析详解开关电源的原理2026-03-29 153

-

开关电源频率的重要性及频率范围分享2024-09-27 3256

-

图文并茂:详细解析无刷电机EMI整改!|深圳比创达电子科技(下)2023-07-11 2316

-

图文并茂:详细解析无刷电机EMI整改?|深圳比创达EMC(上)2023-07-10 1644

-

输入保护电路对开关电源的重要性2021-12-29 1838

-

图文并茂的学习lcd的好文章2021-10-01 3133

-

一个经验丰富的Layout工程师,该如何理解电源设计?2019-11-18 2737

-

Altium Designer 17.1.5软件安装与破解详细图文并茂教程(附网盘下载地址)2017-05-18 193526

-

图文并茂讲解三极管原理2017-02-09 18673

-

Altium Designer 17软件安装与和谐详细图文并茂教程2016-11-18 25183

-

UC3842开关电源设计技巧--电路详解(图文并茂)2016-09-13 18362

-

电脑组装教程图文并茂2016-03-24 1189

-

最全电子元器件介绍(图文并茂,初学者的福音)2013-06-06 50845

-

电源工程师亲授电源设计8大技巧(图文并茂)2012-08-15 34543

全部0条评论

快来发表一下你的评论吧 !