SDRAM控制器设计之异步FIFO的调用

描述

本案例为何需要引入FIFO

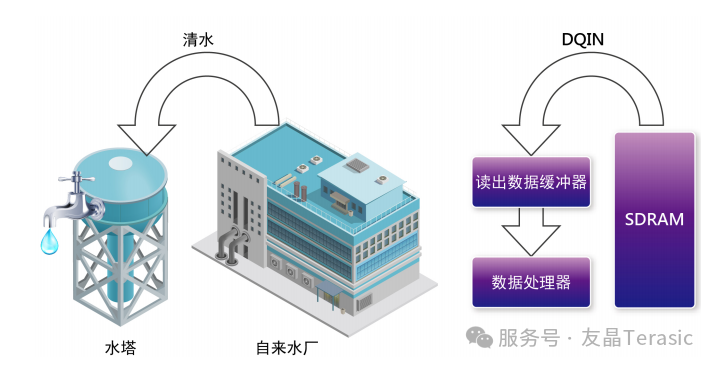

为了加深读者对 FPGA 端控制架构的印象,在数据读取的控制部分,首先我们可以将SDRAM 想作是一个自来水厂,清水得先送至用户楼上的水塔中存放,在家里转开水龙头要用水时,才能及时供应,相同的原理,要读取 SDRAM 中的数据来处理时, FPGA 端的控制架构中一定要有相当于水塔功能的“读出数据缓冲器”,在数据的处理上才会流畅。

而在使用自来水时,自来水厂会补充清水至水塔中,用户才可以连续的使用,同样保存着从 SDRAM 读出数据的缓冲器,当数据量下降到某个程度时也必须要补充,在数据的处理上才不会中断。

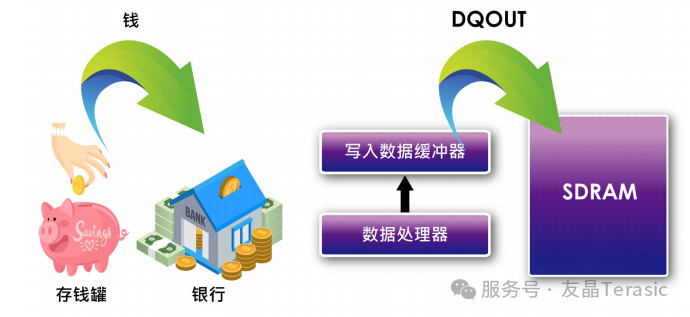

接着在数据写入的控制部分,我们可以将 SDRAM 想作是一个银行,相信当你身上有零钱时会顺手存进存钱罐,而不会费时的跑一趟银行去存钱,相同的原理,要将数据写入SDRAM 时, FPGA 端的控制架构中一定要有相当于存钱罐功能的“写入数据缓冲器”,才不会降低 SDRAM 存取的使用效率。只有在存钱罐存到一个程度时,我们才会取出钱拿去银行存放,同样保存着要写入 SDRAM 数据的缓冲器,当数据量上升到某个程度时也必须要取出放进 SDRAM,才不会造成数据的遗失。

FIFO IP核简介

FIFO 本质是RAM,其作用主要是作为缓存。

RAM和ROM的读写都是根据地址来的,而FIFO( First In First Out)读写不需要提供读地址和写地址,其数据读写按照先入先出的方式。所以FIFO的读写非常简单,但灵活性稍差,不能做到灵活读写。

FIFO分两种:同步FIFO和异步FIFO。同步FIFO读写时钟是一个。异步FIFO的读时钟和写时钟是分开的。

同步FIFO和异步FIFO常应用在同步时钟系统和异步时钟系统中。异步FIFO应用场景如多比特数据做跨时钟域处理、前后带宽不同步等。

本案例中用到的是异步FIFO。异步FIFO IP模块接口如下图:

异步FIFO IP模块信号描述如下:

*注意:FIFO复位信号是高电平有效。

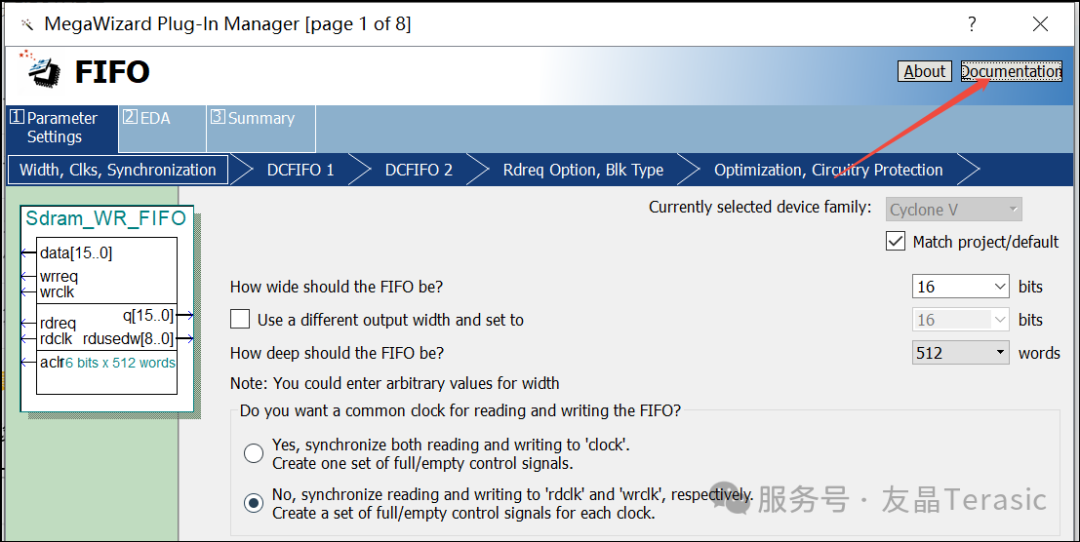

打开FIFO IP 设置界面可以找到FIFO文档链接:

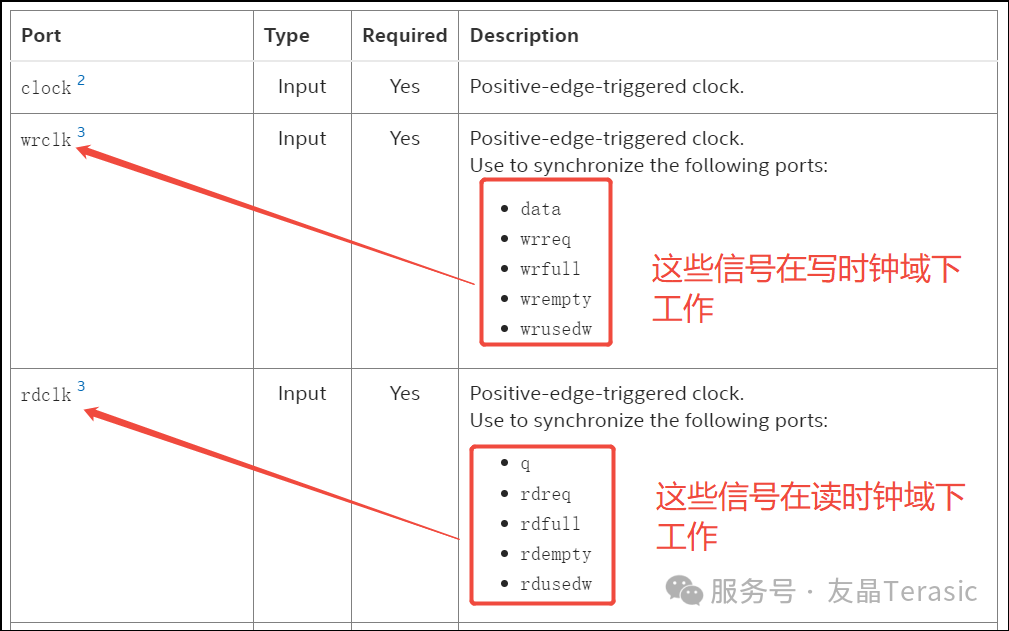

阅读FIFO文档可知异步FIFO写操作的各个信号在写时钟下进行工作,读操作的各个信号在读时钟下进行工作:

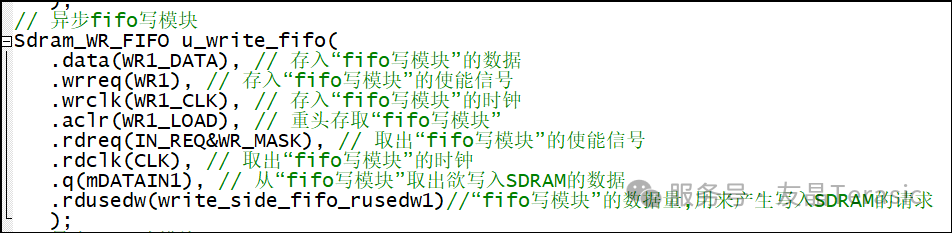

Sdram_Control.v文件里面例化了两个FIFO模块,一个是异步FIFO写模块,用于缓存要写入SDRAM器件的数据。异步FIFO写模块的数据写入在27MHz时钟下进行,数据的读出在100MHz时钟下进行。

Sdram_Control.v文件例化的另一个FIFO模块是异步FIFO读模块,用于缓存从SDRAM器件读出的数据。异步FIFO读模块的数据写入在100MHz时钟下进行,数据的读出在27MHz时钟下进行。

FIFO IP 设置

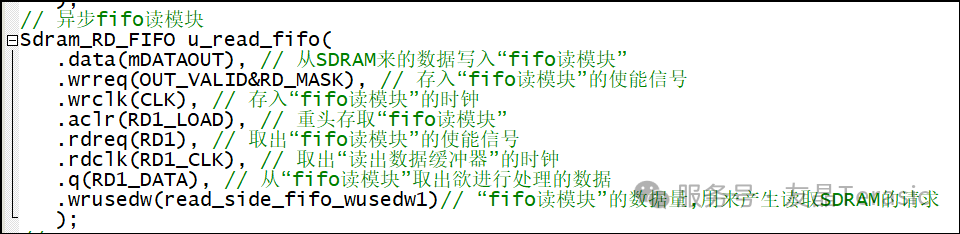

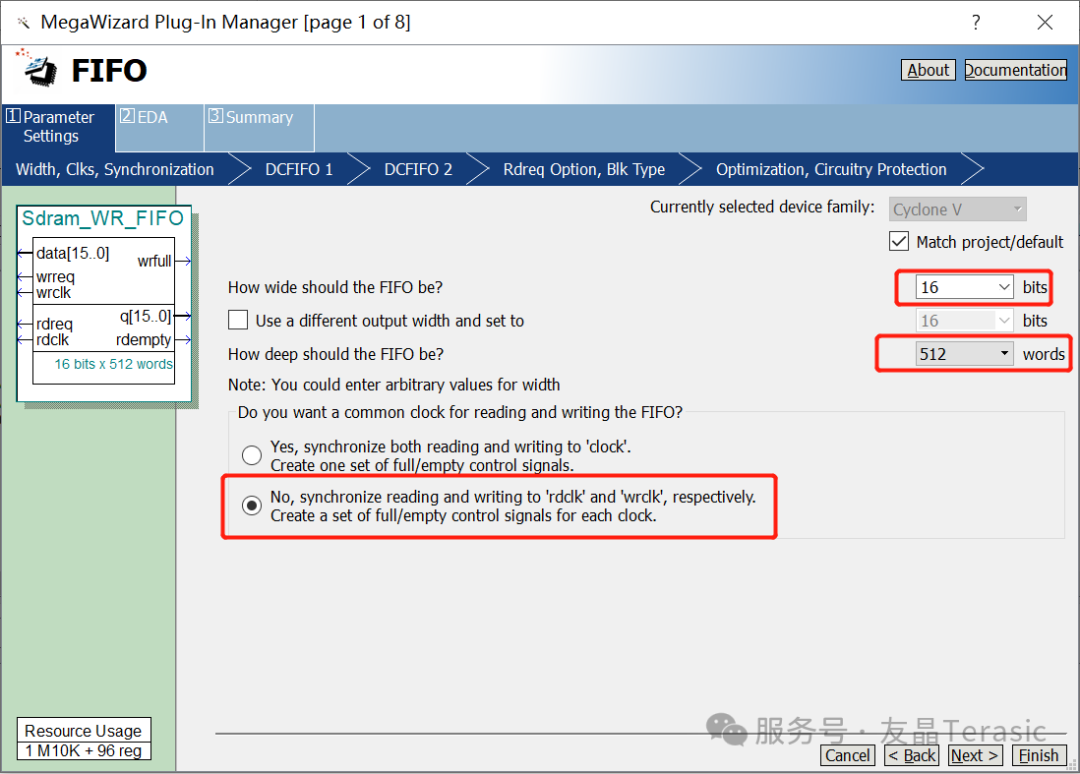

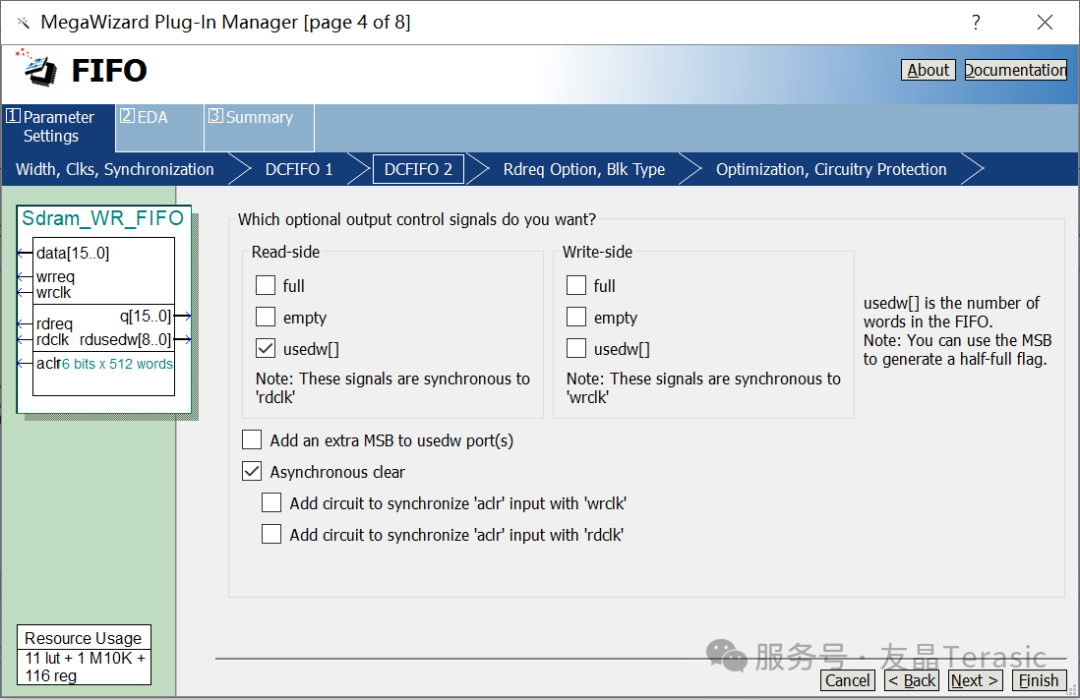

异步FIFO写模块的IP设置如下:

FIFO数据位宽是16bit,与SDRAM位宽保持一致。

FIFO存储深度设置512字,虽然实际存储255个数据,但一般深度都设置大一点。

勾选读写时钟分开的选项。

勾选读端口的rdusedw接口,用来生成写SDRAM器件的请求信号。

其他选项可以选择默认。

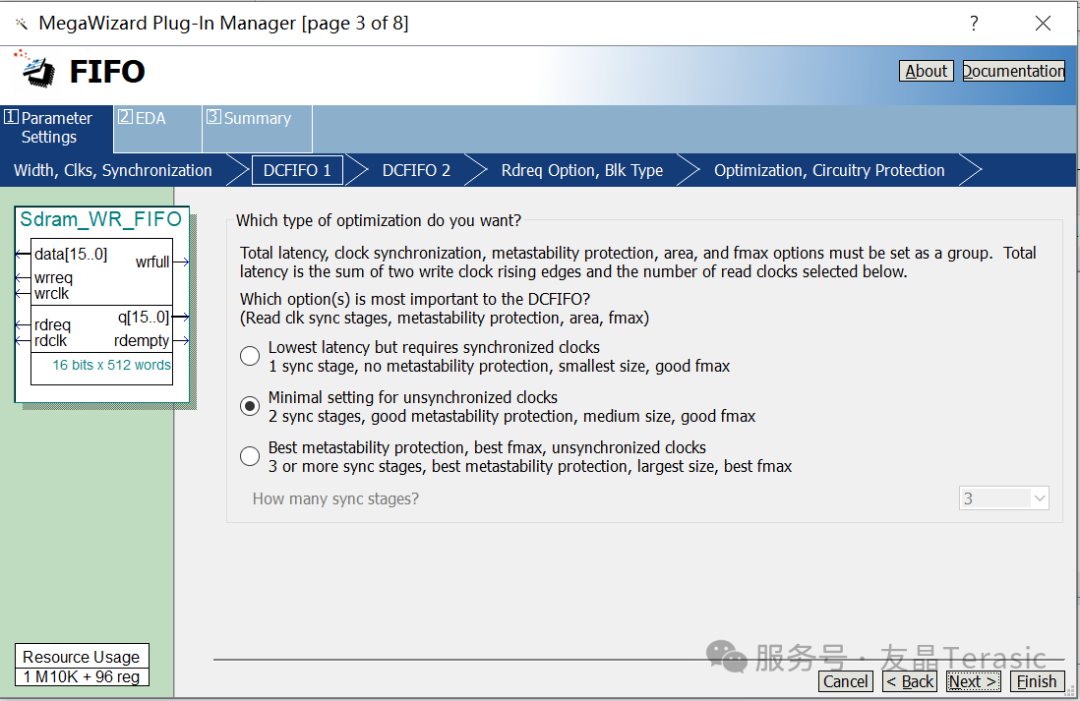

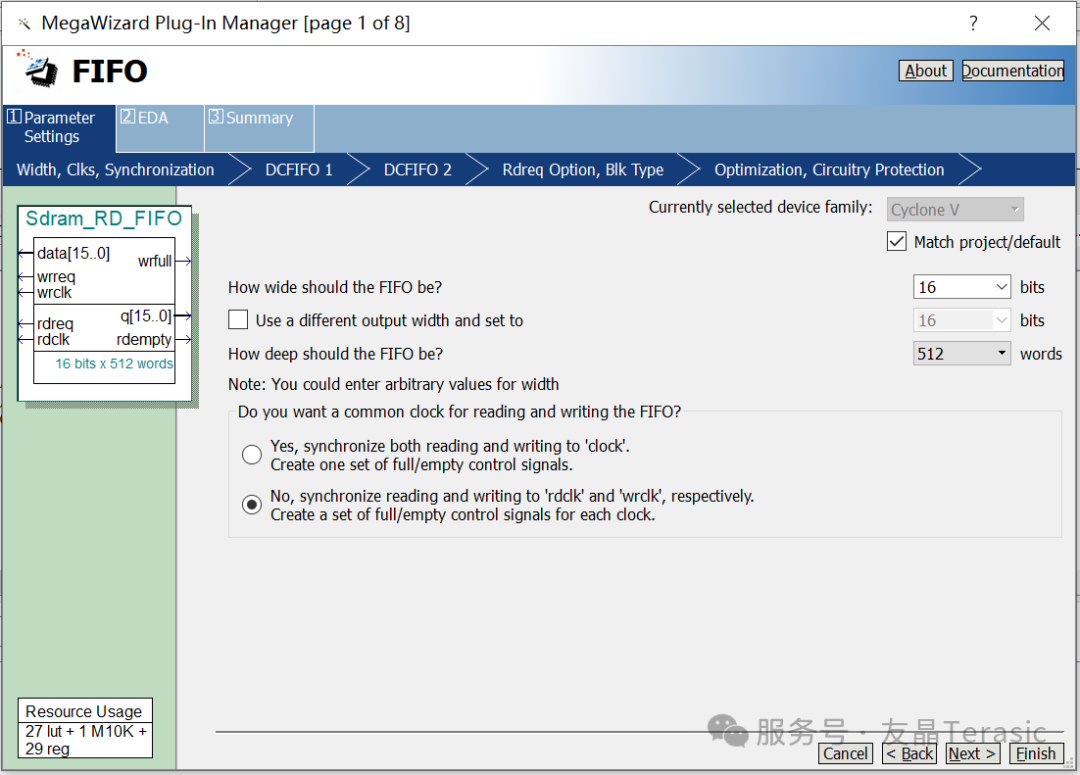

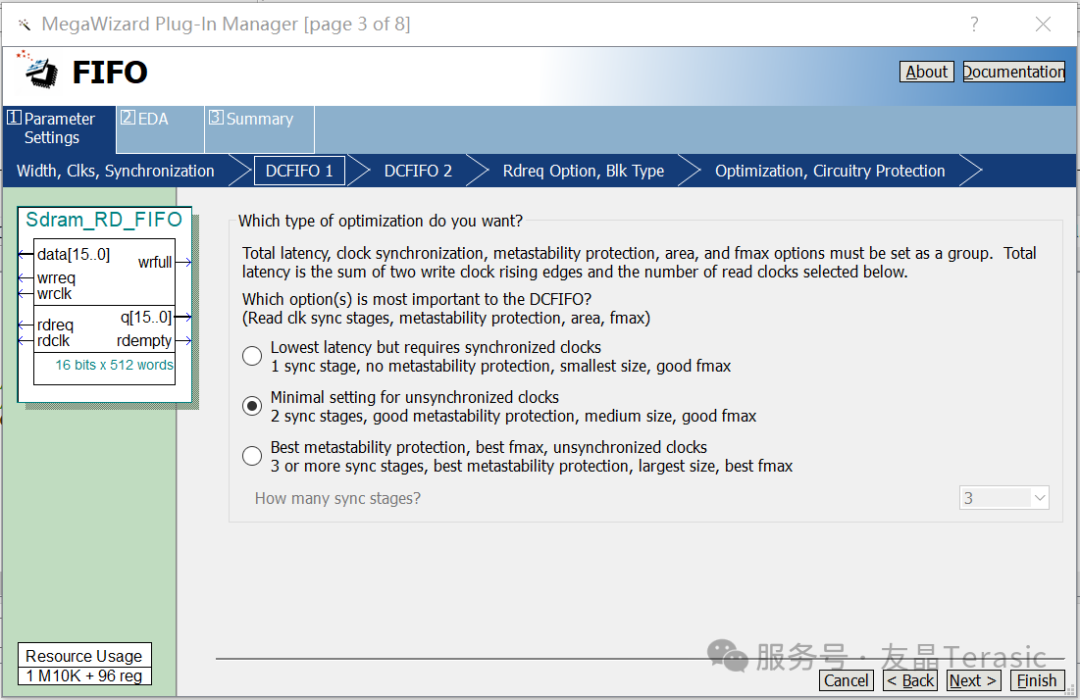

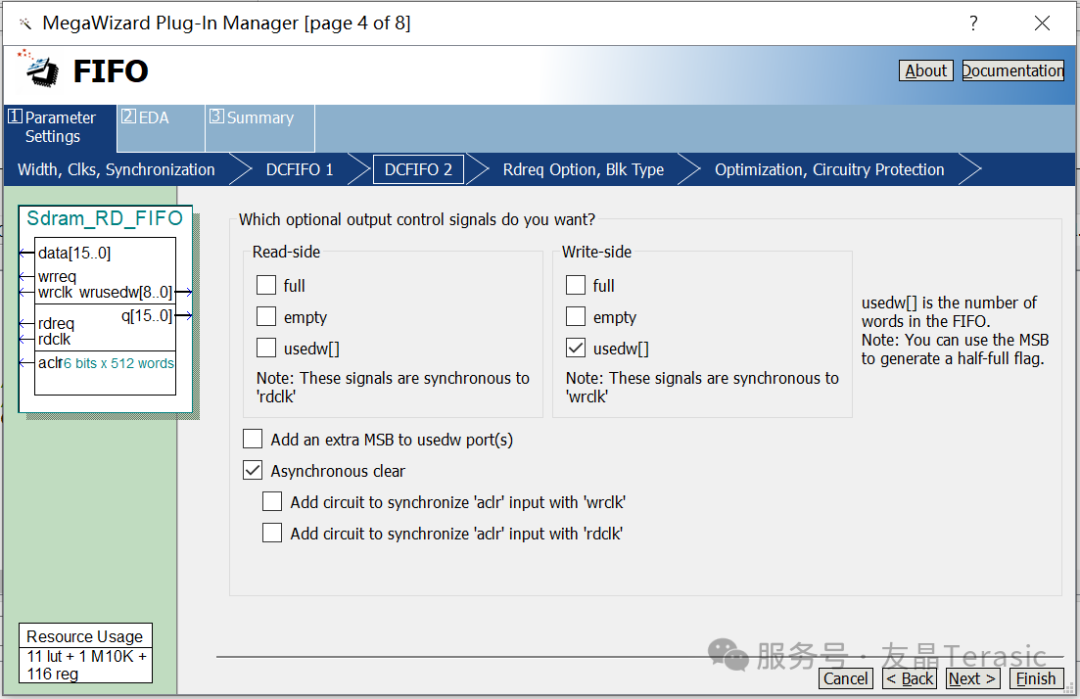

异步FIFO读模块的IP设置如下:

FIFO数据位宽是16bit,与SDRAM位宽保持一致。

FIFO存储深度设置512字,虽然实际存储127个数据,但一般深度都设置大一点。

勾选读写时钟分开的选项。

勾选写入端口的wrusedw接口,用来生成读SDRAM器件的请求信号。

其他选项可以选择默认。

-

SDRAM控制器的设计——Sdram_Control.v代码解析(异步FIFO读写模块、读写SDRAM过程)2025-03-04 2635

-

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文2018-12-25 1737

-

【开源骚客】《轻松设计SDRAM控制器》第九讲—解密读写FIFO2017-05-08 3828

-

Gowin SDRAM控制器的参考设计2022-10-08 800

-

使用Verilog实现基于FPGA的SDRAM控制器2009-06-20 2504

-

SDRAM控制器简易化设计2011-10-24 1197

-

EPM1240的SDRAM控制器的设计2017-10-31 905

-

SDRAM控制器的设计2017-11-28 1495

-

基于SDRAM控制器软核的Verilog设计2021-06-30 3667

-

利用ISE的SDRAM设计的FIFO实验2021-08-04 955

-

Gowin SDRAM控制器用户指南2022-09-15 813

-

异步FIFO之Verilog代码实现案例2022-11-01 2718

-

FIFO设计—异步FIFO2023-05-26 2349

-

PIC32系列参考手册之DDR SDRAM控制器2023-09-25 555

-

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用2023-10-18 2912

全部0条评论

快来发表一下你的评论吧 !