芯片制造中薄膜厚度量测的重要性

描述

文章来源:半导体与物理

原文作者:jjfly686

本文论述了芯片制造中薄膜厚度量测的重要性,介绍了量测纳米级薄膜的原理,并介绍了如何在制造过程中融入薄膜量测技术。

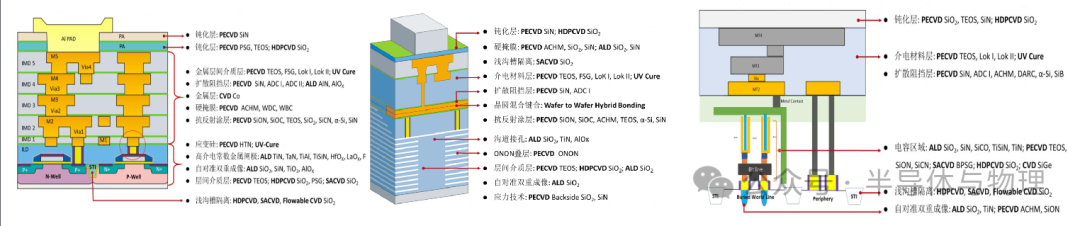

在芯片制造的数百道工序中,薄膜沉积非常重要。从晶体管栅极氧化层到金属互连的阻挡层,每一层薄膜的厚度误差都必须控制在原子尺度(埃米级,1Å=0.1nm)。薄膜厚度量测,正是确保芯片制造中的有效保证。

芯片为何需要精确量测薄膜厚度?

1.1 电学性能参数

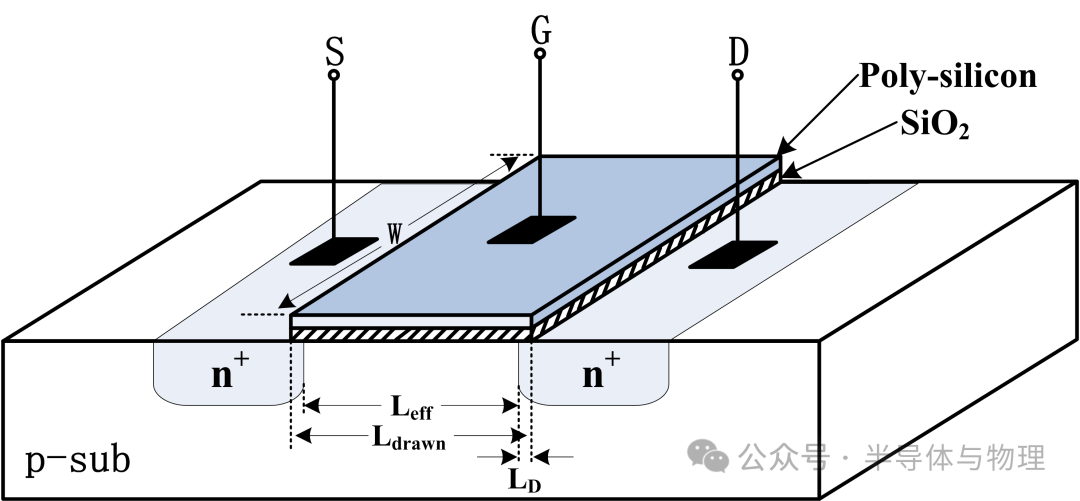

MOS晶体管:栅极氧化层(如SiO₂)厚度每减少0.1nm,漏电流可能指数级增加。例如,在7nm制程中,3Å的厚度偏差会导致晶体管阈值电压偏移超过10%。

金属互连层:铜阻挡层(如TaN)若过薄,铜原子会扩散到绝缘层引发短路;过厚则会增加线路电阻,降低芯片运行速度。

1.2 工艺控制

设备稳定性:薄膜沉积设备(如ALD、PVD)的工艺稳定性直接体现在膜厚均匀性上。

结构应力:在多层堆叠结构(如3D NAND闪存)中,每层薄膜厚度的累积误差可能导致整体结构应力失衡。

1.3 良率与成本

高价值晶圆:一片300mm晶圆价值数万美元,若因膜厚失控导致整批报废,损失可达千万级别。在线量测系统能提前拦截90%以上的膜厚异常。

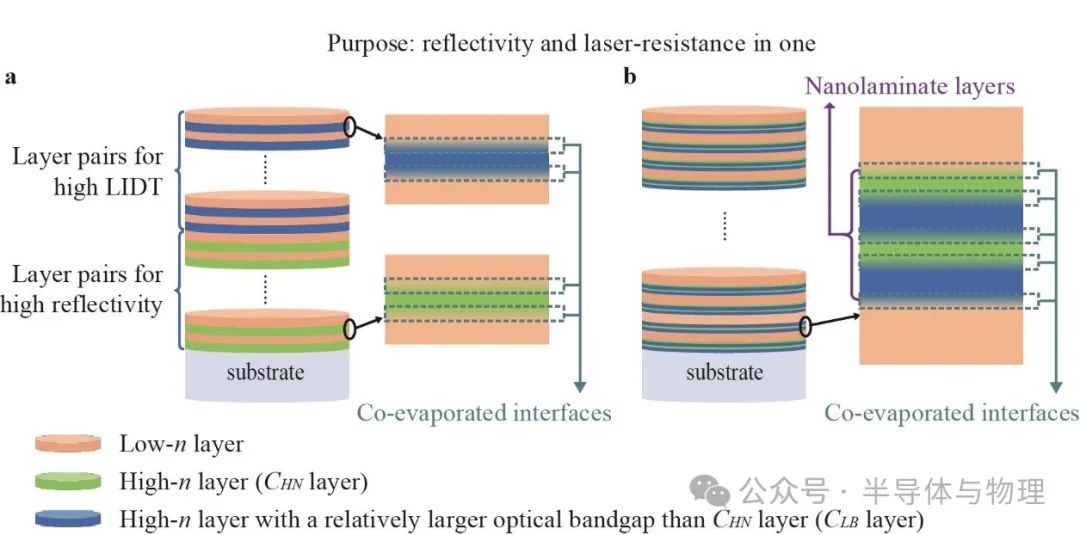

测量纳米级薄膜原理

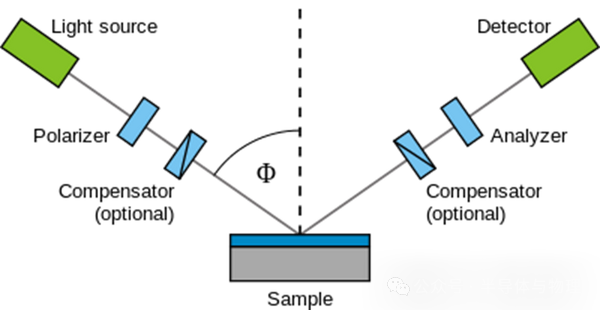

2.1 椭圆偏仪(Ellipsometry)

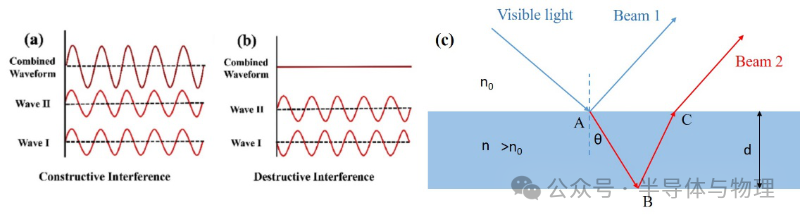

原理:利用偏振光在薄膜表面的反射相位差,通过建立光学模型反推膜厚。当光束以特定角度入射时,薄膜上下界面的反射光会发生干涉,相位差与膜厚成函数关系。

优势:非接触、可测1nm以下超薄膜,适用于透明介质(如SiO₂、SiN)。

局限:需已知材料光学常数(n、k值),对金属/高吸收材料灵敏度低。

2.2 X射线反射法(XRR)

原理:利用X射线在薄膜界面处的全反射临界角与膜厚的关联。当X射线以0.1°~1°掠入射时,反射强度曲线会出现周期性振荡,振荡周期与膜厚成反比。

案例:可测量1Å精度的超薄高k材料(如HfO₂),甚至能分辨5层以上的叠层结构。

挑战:设备昂贵,需真空环境,测量速度较慢。

2.3 光学干涉法(Optical Interferometry)

原理:通过测量薄膜表面与基底反射光的光程差计算厚度。在台阶结构处,利用白光干涉产生的彩色条纹间距推算膜厚。

应用:常用于金属膜(如铜互连层)、光刻胶厚度检测,精度可达±0.1nm。

薄膜量测如何融入制造流程

3.1 在线量测(In-line Metrology)系统

时机选择:在关键薄膜沉积/刻蚀工序后立即插入量测站,例如栅极氧化层生长后、金属阻挡层沉积前。

采样策略:每片晶圆测量9~49个点(边缘、中心、45°斜角等),绘制厚度分布热力图。对于EUV光刻胶等敏感材料,甚至需全片扫描。

3.2 量测-刻蚀协同优化

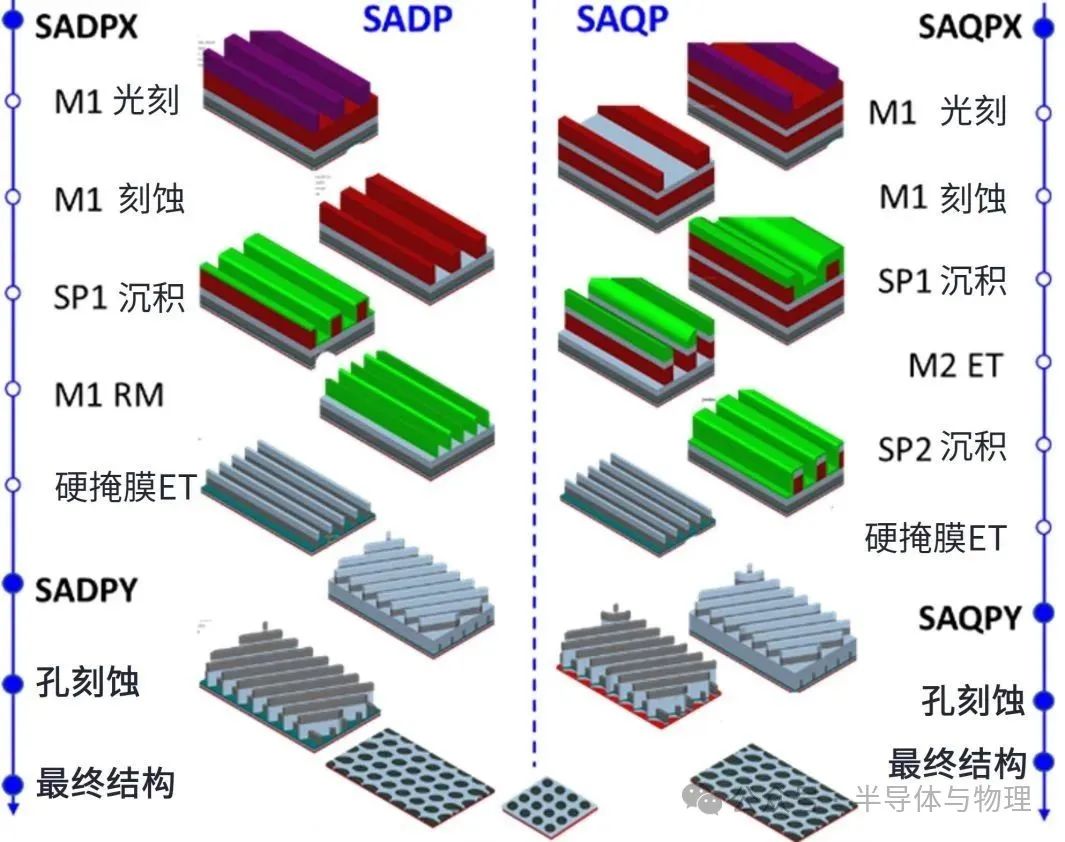

动态调整:在双重自对准工艺中,先量测硬掩模厚度,再动态调整刻蚀时间。例如,若SiN硬掩模实测厚度为42nm(设计值40nm),刻蚀机将自动延长2秒反应时间。

3.3 跨层关联分析

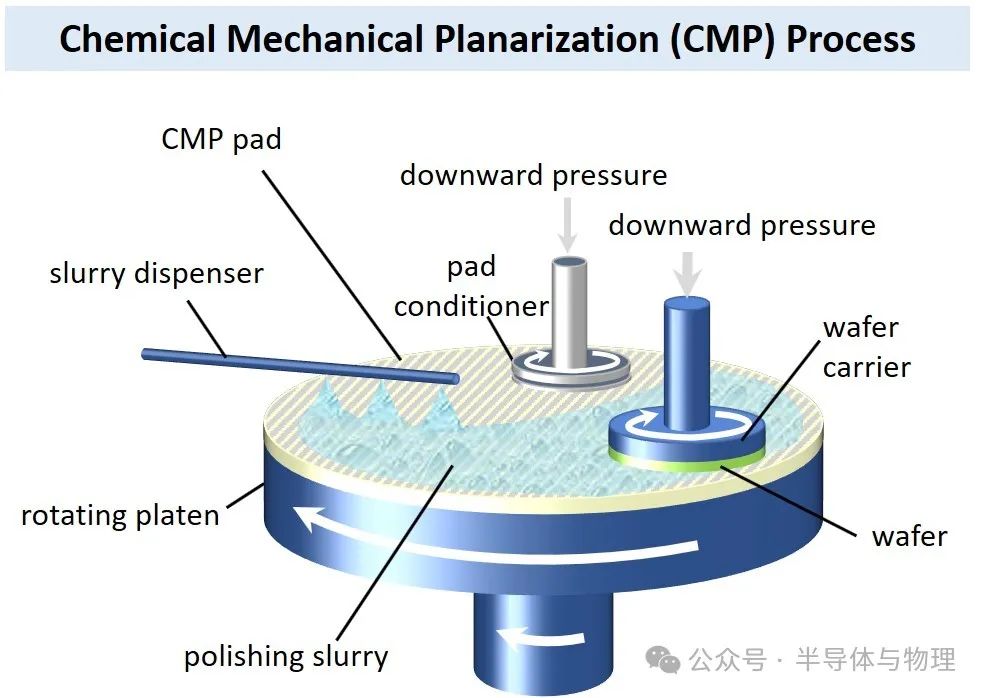

联动建模:将薄膜厚度数据与后续工艺参数(如CMP抛光速率、光刻焦深)联动建模。

-

光刻胶旋涂的重要性及厚度监测方法2025-08-22 2011

-

PCBA加工中的灵魂:揭秘芯片烧录的重要性2024-11-20 2001

-

薄膜电容的厚度2024-10-10 1869

-

sio2薄膜的厚度量测原理2024-09-27 1649

-

集成芯片的重要性和必要性2024-03-18 2605

-

请问一下在芯片制造中如何测薄膜的厚度呢?2023-08-17 1611

-

PCB制造中铜厚度的重要性2023-08-08 3136

-

射频芯片在应用中的重要性2023-07-27 2508

-

射频芯片测试的重要性及方法2023-06-29 2980

-

芯片的重要性及作用2021-12-17 29725

-

基于变量依赖关系模型的变量重要性度量综述2021-07-02 930

-

绝缘测试的重要性2020-12-23 5276

-

PCB制造中可制造性设计的重要性2020-10-19 2490

-

MEMS制造中精确测量薄膜厚度的方法研究与比较_陈莉2017-03-19 947

全部0条评论

快来发表一下你的评论吧 !