闪存冲击400层+,混合键合技术传来消息

存储技术

描述

电子发烧友网综合报道,据韩媒报道,三星近日与长江存储签署了3D NAND混合键合专利许可协议,从第10代V-NAND开始,将使用长江存储的专利技术,特别是在“混合键合”技术方面。

W2W技术是指将两片已经加工完毕的晶圆直接键合在一起。这项技术通过直接将两片晶圆贴合,省去了传统的凸点连接,从而缩短了电气路径,提高了性能和散热能力,同时优化了生产效率,是目前混合键合中最常用的技术。

据ZDNet报道,三星之前在NAND生产中使用COP(外围单元)方法,即将外围电路置于一个晶圆上,并将单元堆叠在上面。当层数超过400层时,底层外围电路的压力会显著增加,影响芯片的可靠性。

根据三星的计划,2025年下半年将量产下一代V10 NAND,预计堆叠层数将达到420至430层。因此引入W2W技术势在必行。

长江存储的混合键合技术命名为“晶栈(Xtacking)”,于四年前推出并用于3D NAND制造,同时进行了全面的专利布局。

据介绍,在晶栈Xtacking架构推出前,市场上的3D NAND主要分为传统并列式架构和CuA(CMOS under Array)架构。长江存储通过创新布局和缜密验证,经过长达9年在3D IC领域的技术积累和4年的研发验证后,终于将晶圆键合这一关键技术在3D NAND闪存上得以实现。

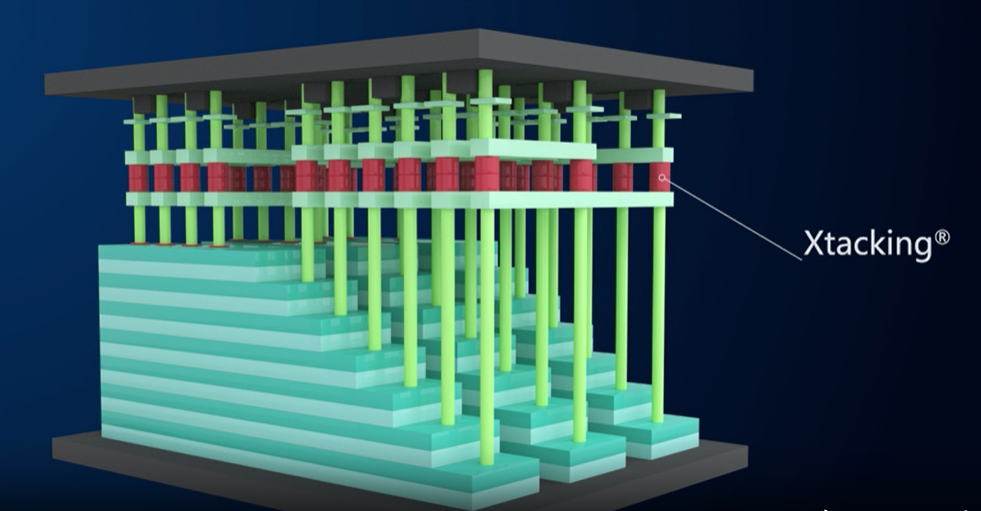

在指甲盖大小的面积上实现数十亿根金属通道的连接,合二为一成为一个整体,拥有与同一片晶圆上加工无异的优质可靠性表现,这项技术为未来3D NAND带来更多的技术优势和无限的发展可能。随着层数的不断增高,基于晶栈Xtacking所研发制造的3D NAND闪存将更具成本和创新优势。

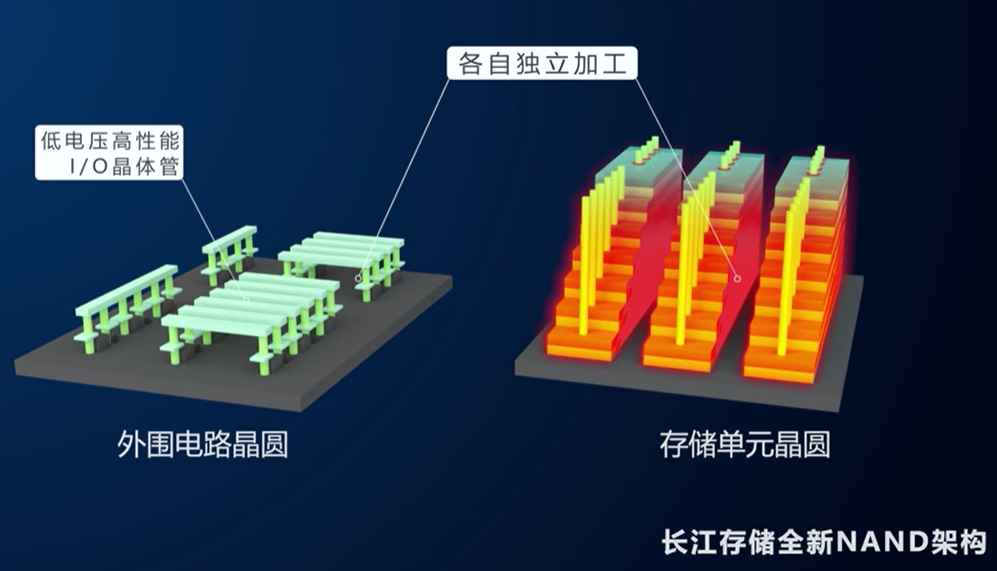

晶栈Xtacking可实现在两片独立的晶圆上加工外围电路和存储单元,这样有利于选择更先进的逻辑工艺,从而让NAND获取更高的I/O接口速度及更多的操作功能。当两片晶圆各自完工后,创新的晶栈Xtacking技术只需一个处理步骤即可通过数十亿根垂直互联通道(VIA)将两片晶圆键合,合二为一。

在传统3DNAND架构中,外围电路约占芯片面积20~30%,晶栈®Xtacking技术创新的将外围电路置于存储单元之上,从而实现比传统3D NAND更高的存储密度,芯片面积可减少约25%。

晶栈Xtacking 技术充分利用存储单元和外围电路的独立加工优势,实现了并行的、模块化的产品设计及制造,产品开发时间可缩短三个月,生产周期可缩短20%。此外,这种模块化的方式也为引入NAND外围电路的创新功能以实现NAND闪存的定制化提供了可能。

在长江存储第三代系列产品中,晶栈 Xtacking已全面升级至2.0,进一步释放3D NAND闪存潜能。晶栈 Xtacking2.0充分利用架构优势为客户带来更多价值。其中包括:进一步提升闪存吞吐速率、提升系统级存储的综合性能、开启定制化闪存全新商业模式等。

根据TechInsights技术分析,致态TiPro9000固态硬盘(ZTSS3CB08B34MC)采用了长江存储的新型Xtacking4.x芯片。它由2yy 个有源层(除漏极选择栅极SGD外,总栅极数为 294层)组成,下层拥有 150 个栅极,而上层则有 144 个栅极。其TLC NAND 的位密度增至20Gbit/mm^2以上,这在业界尚属首次。

目前掌握3D NAND混合键合关键专利的公司包括美国的Xperi、中国的长江存储和中国台湾的台积电。Xperi是一家专利授权公司,台积电是一家半导体代工企业,而长江存储的“Xtaking”技术已经稳定量产,并演进到“4.x”版本。

外媒报道称,三星要开发下一代NAND几乎不可能规避长江存储的专利。同样的,SK海力士也在开发400层以上NAND产品,一旦用到混合键合技术或将不可避免地需要与长江存储签订专利授权协议。

- 相关推荐

- 热点推荐

- 闪存

-

突破堆叠瓶颈:三星电子拟于16层HBM导入混合键合技术2025-07-24 1175

-

混合键合(Hybrid Bonding)工艺介绍2025-07-10 4136

-

混合键合市场空间巨大,这些设备有机会迎来爆发2025-06-03 3450

-

Cu-Cu混合键合的原理是什么2025-02-26 2251

-

微流控多层键合技术2024-11-19 1372

-

混合键合的基本原理和优势2024-10-30 5226

-

混合键合,成为“芯”宠2024-10-18 2190

-

混合键合技术大揭秘:优点、应用与发展一网打尽2024-02-18 5041

-

什么是混合键合?为什么要使用混合键合?2023-11-22 7043

-

混合键合的发展趋势和挑战2023-07-15 3569

-

铜混合键合的发展与应用2023-05-08 2987

-

硅-直接键合技术的应用2018-11-23 3492

-

混合电路内引线键合可靠性研究2010-05-31 765

全部0条评论

快来发表一下你的评论吧 !