ADMV4530具有集成小数N分频PLL和VCO的双模式Ka频段上变频器技术手册

描述

概述

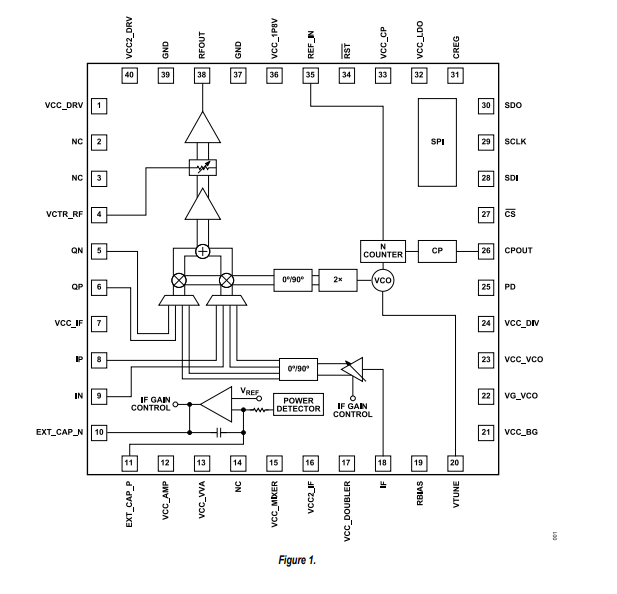

ADMV4530 是一款高度集成的上变频器,具有非常适合下一代 Ka 频段卫星通信的同相/正交 (I/Q) 混频器。

集成的低相位噪声、小数 N 分频锁相环 (PLL),带有压控振荡器 (VCO) 和内部 2× 乘法器,可为 I/Q 混频器产生必要的片内本地振荡器 (LO) 信号,无需外部频率合成。VCO 使用内部自动校准例程,以便 PLL 可选择必要设置,并锁定大约 100 μs。

*附件:ADMV4530具有集成小数N分频PLL和VCO的双模式Ka频段上变频器技术手册.pdf数据表:

PLL 的单端参考输入以高达 500 MHz 的频率运行,并采用内部参考分频器和倍频器,以实现更高的灵活性。此外,相位频率检波器 (PFD) 比较频率可高达 250 MHz(对于整数模式)和 160 MHz(对于小数 N 分频模式)。

上变频器包含一个 I/Q 混频器,该混频器既可以在带宽为 500 MHz 的 I/Q 模式下运行,也可以在带宽高达 3 GHz 的 IF 模式下运行,从而支持各种射频架构以及与旧系统的向后兼容性。

增益和可变衰减级紧随 I/Q 混频器。该配置可实现 19 dBm 的最小 1 dB 压缩点 (P1dB),从而无需外部增益级。

利用可编程 4 线串行端口接口 (SPI),可以调整正交相位,以实现较佳的边带抑制。此外,SPI 允许在 IF 模式下对 LO 馈通进行调零。在 I/Q 模式下,可以通过向差分基带 I/Q 输入施加外部直流失调来对 LO 馈通进行调零。

IF 自动增益控制 (AGC) 调节 IF 可变增益放大器 (VGA),以补偿输入功率变化。在正常操作期间,可以通过 SPI 启用或禁用此 AGC 功能。在正常操作期间禁用时,AGC 特性仅在关断模式下处理测试信号音,以跟踪温度变化。

ADMV4530 上变频器采用符合 RoHs 指令的 6 mm × 6 mm 40 端子岸面栅格阵列 (LGA) 封装。ADMV4530 在 −40°C 至 +85°C 的外壳温度范围内工作。

应用

- 卫星通信

- 点对点微波通信

特性

- RF 输出频率范围:27 GHz 至 31 GHz

- 两种升频转换模式

- 从差分基带 I/Q 直接进行升频转换(I/Q 模式)

- 单上边带升频转换(IF 模式)

- 1 dB 带宽:500 MHz(I/Q 模式)

- 输入频率范围:2 GHz 至 3 GHz(IF 模式)

- 匹配的 50 Ω 单端 RF 输出

- 匹配的 50 Ω 单端 IF 输入

- 可编程基带 I/Q 共模电压

- 边带抑制和载波馈通优化

- RF 和 IF 组合增益动态范围:70 dB

- 可编程自动 IF 增益控制

- 可通过 3 线或 4 线 SPI 进行编程

- 符合 RoHS 指令的 40 端子 6 mm × 6 mm LGA

功能框图

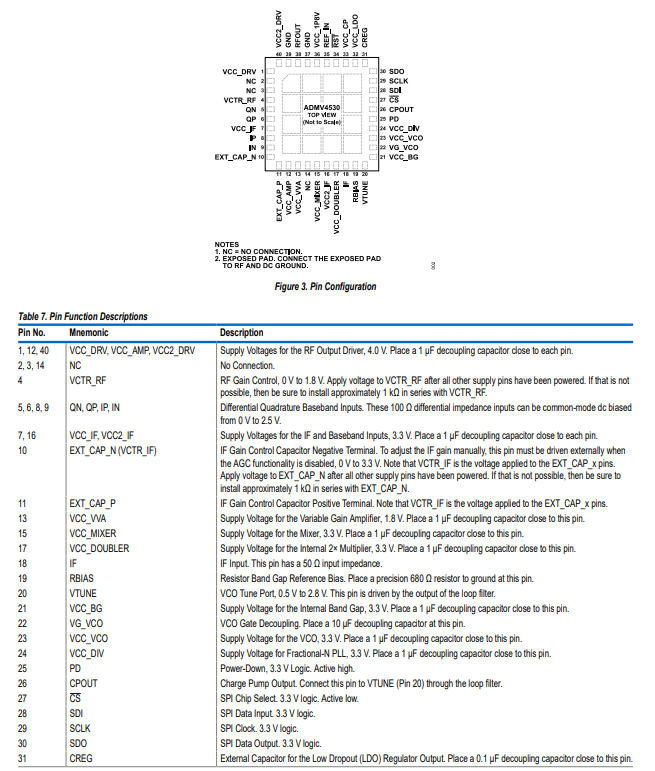

引脚配置和功能描述

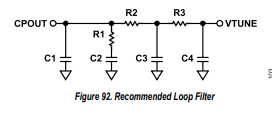

环路滤波器

为PLL定义环路滤波器取决于几个动态因素,如fpFD、N计数器值、Kyco和选定的电荷泵电流((cp))。在小数N分频模式下,较高的fpFD具有降低带内相位噪声性能的优势,但会降低边界杂散水平。因此,较低的fprD可以使PLL在整数n模式下工作,从而消除整数边界杂散,但代价是带内相位噪声性能较高。考虑到权衡因素,必须注意频率规划和fpFD选择,以确保适当的带内相位噪声性能与最终应用可接受的杂散水平相匹配。

利用ADMV4530评估板之一实现的环路滤波器(参见“订购指南”部分)是一种三阶无源滤波器,如图92所示。该滤波器采用以下仿真输入参数设计:fppo = 100 MHz,Kvco = 155MHz/V,uco = 15 GHz,lcp =4.2 mA。对于以下元件值,最终的lop滤波器带宽和相位裕量分别为540 kHz和558ộ:C1 = 150 pf,C2 = 15 nF,C3 =20 pF,C4 =不安装(DNI),r1 = 910,R2 = 910 Q2,R3 = 0ω。

-

ADMV4530:Ka频段上变频器的卓越之选2026-05-08 327

-

探索ADMV1139A:37 GHz - 50 GHz 5G微波上变频器与下变频器2026-04-30 168

-

探索ADMV1355:17.7GHz - 55GHz宽带微波上变频器的卓越性能2026-04-28 146

-

ADMV4630集成小数N分频PLL和VCO的Ku频段上变频器技术手册2025-04-18 1734

-

HMC1197集成小数N分频PLL和VCO的宽带直接正交调制器技术手册2025-03-01 1442

-

ADMV4530: Dual-Mode, Ka Band Upconverter with Integrated Fractional-N PLL and VCO Data Sheet ADMV4530: Dual-Mode, Ka Band Upconverter with I2023-10-12 55

-

ADMV4420:集成小数N PLL和压控振荡器数据表的K波段下变频器2021-04-29 809

-

ADMV4530:带集成小数N PLL和压控振荡器的双模Ka波段上变频器数据表2021-04-24 937

-

ADMV4530板损2021-03-23 889

-

ADMV4530 Board Loss2021-01-30 751

-

Analog Devices ADMV4530 Ka频段上变频器在贸泽开售2020-06-15 1933

全部0条评论

快来发表一下你的评论吧 !