ADRF5030 100MHz至20GHz、非反射式硅SPDT开关技术手册

描述

概述

ADRF5030 是非反射式单刀双掷 (SPDT) 开关使用绝缘体上硅 (SOI) 制造 过程。ADRF5030 的工作频率范围为 100 MHz 至 20 GHz,具有 插入损耗低于 1.2 dB,隔离度高于 45 分贝。该器件的 RF 输入功率处理能力为 RFC 和 RFx 的平均值为 33 dBm/峰值为 36 dBm 路径、终止路径和 RFC 和 RFx 端口。ADRF5030采用双电源电压工作 ±3.3 V。ADRF5030采用互补金属氧化物 半导体 (CMOS) 和低压晶体管到晶体管逻辑 (LVTTL) 兼容控制。

数据表:*附件:ADRF5030 100MHz至20GHz、非反射式硅SPDT开关技术手册.pdf

ADRF5030 还可以在单个正电源电压下工作 (V DD) 施加,同时将负电源电压 (V SS ) 连接到 地。在这种工作条件下,小信号性能 同时保持开关特性、线性度和功率 处理性能被降低。有

ADRF5030 与 ADRF5022 引脚兼容,并且 ADRF5026,并且引脚与 ADRF5031 兼容,这是一种慢速开关、 低截止版本,工作频率范围为 9 kHz 至 20 GHz。

ADRF5030 封装在 20 端子、3 mm × 3 mm 的封装中, 符合 RoHS 标准,基板栅格阵列 (LGA)。ADRF5030 运行 从 −40°C 到 +105°C。

应用

- 测试仪器

- 军用无线电、雷达、电子对抗措施 (ECM)

- 微波无线电和甚小孔径终端 (VSAT)

特性 - 宽带频率范围,100 MHz 至 20 GHz

- 非反光设计

- 低插入损耗

- 0.1 GHz 至 6 GHz 之间为 0.7 dB(典型值)

- 6 GHz 至 12 GHz 之间为 0.9 dB(典型值)

- 1.2 dB(典型值),最高 20 GHz

- 高隔离度

- 100 MHz 至 6 GHz 之间为 55 dB(典型值)

- 6 GHz 至 12 GHz 之间为 50 dB(典型值)

- 45 dB(典型值),最高 20 GHz/li>

- 高输入线性度

- P0.1dB:>36 dBm(典型值)

- IP3:60 dBm(典型值)

- 高 RF 功率处理能力

- 直通路径:36 dBm 峰值 / 33 dBm 平均值

- 端接路径:36 dBm 峰值 / 33 dBm 平均值

- 热开关路径:36 dBm 峰值/33 dBm 平均值

- CMOS/LVTTL 兼容

- 无低频杂散;无负电压发生器

- 快速 RF 开关时间:70 ns

- RF 建立时间 (0.1 dB):95 ns

- 单电源工作能力(V

DD= 3.3 V,VSS= 0 V) - 20 引脚、3 mm x 3 mm LGA 封装

- 引脚兼容ADRF5022 & ADRF5026

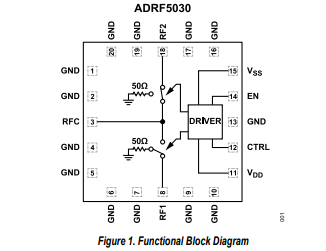

框图

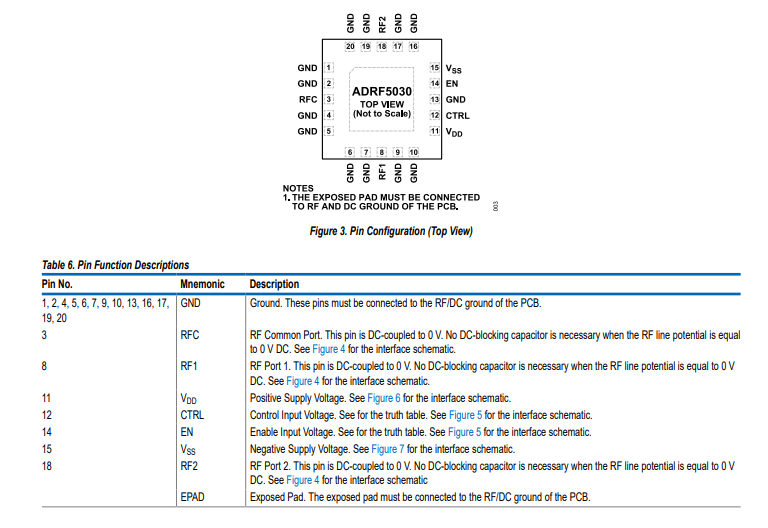

引脚配置

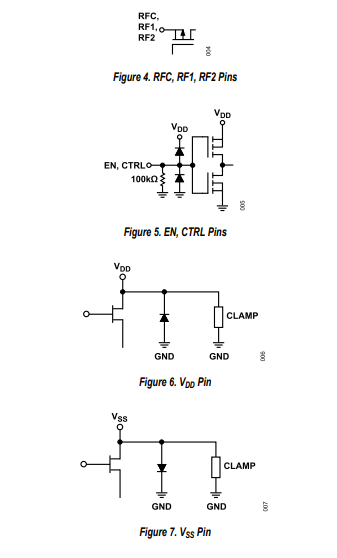

接口示意图

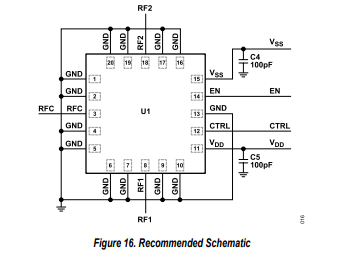

ADRF5030有两个电源引脚(VDD和Vss)和两个控制引脚(EN、CTRL)。图16显示了电源引脚的外部元件和连接。Vpo和Vss引脚通过一个100 pF电容去耦。器件引脚排列允许去耦电容靠近器件放置。当RF线路偏置电压不是0v时,除了RF引脚上的隔DC电容之外,偏置和工作不需要其他外部元件,详情参见表6。

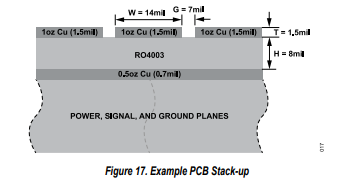

RF端口内部匹配50ω,引脚排列设计用于匹配PCB上具有50ω特性阻抗的共面波导(CPWG)。图17显示了RF基板的referencedCPWG RF走线设计,采用8密耳厚的RogersRO4003C电介质材料。对于1.5密耳的成品铜厚度,建议使用14密耳宽和7密耳间隙的RF走线。

-

ADRF5019 100MHz至13 GHz硅SPDT非反射式开关技术手册2025-03-05 1251

-

ADRF5010硅SPST开关,非反射式,100MHz至55GHz技术手册2025-03-04 1442

-

ADRF5024硅SPDT开关,反射式,100 MHz至44 GHz数据表2021-05-28 739

-

ADRF5301:硅SPDT开关,反射式,35 GHz至44 GHz初步数据表2021-05-17 828

-

ADRF5025:硅SPDT开关,反射式,9 kHz至44 GHz数据表2021-04-19 692

-

ADRF5019:硅,SPDT开关,无反射,100 MHz至13 GHz数据表2021-04-18 858

-

ADRF5024:硅SPDT开关,反射式,100 MHz至44 GHz数据表2021-04-09 902

-

ADRF5300:评估ADRF5300,硅片,SPDT开关,反射式,24 GHz至32 GHz用户指南18862021-03-22 912

全部0条评论

快来发表一下你的评论吧 !