ADRF5534 3.1GHz至4.2GHz,接收器前端技术手册

描述

概述

ADRF5534 是一款集成 RF 的前端多芯片模块,设计用于时分双工 (TDD) 应用。该套件的工作频率为 3.1 GHz 至 4.2 GHz。ADRF5534 配置有 LNA 和一个大功率硅 SPDT 开关。

在 3.6 GHz 的接收过程中,LNA 提供 1.3 dB 的低噪声指数 (NF) 和 35.5 dB 的高增益,并且具有 −4 dBm 的三阶交调截点 (IIP3)。

在发射过程中,该开关提供 0.8 dB 的低插入损耗,并在整个生命周期内处理 37 dBm 的长期演进 (LTE) 平均功率(8 dB 峰值至平均值比 (PAR)),而在单一事件(<10 秒)LNA 保护模式下为 39 dBm。

该套件采用符合 RoHS 标准的紧凑型 5 mm × 3 mm 24 引脚 LFCSP 封装。

数据表:*附件:ADRF5534 3.1GHz至4.2GHz,接收器前端技术手册.pdf

应用

- 无线基础设施

- TDD 大规模多输入和多输出 (MIMO) 以及有源天线系统

- 基于 TDD 的通信系统

特性 - 集成式 RF 前端

- LNA 和高功率硅 SPDT 开关

- 片内偏置和匹配

- 单电源供电

- 增益:3.6 GHz 时为 35.5 dB(典型值)

- 增益平坦度:25°C 下为 1.5 dB(400 MHz 带宽)

- 低噪声指数:3.6 GHz 时为 1.3 dB(典型值)

- 低插入损耗:3.6 GHz 时为 0.8 dB(典型值)

- T

CASE= 105°C 时具有高功率处理能力- 整个生命周期

- LTE 平均功率 (8 dB PAR):37 dBm

- 单一事件(运行时间 <10 秒)

- LTE 平均功率 (8 dB PAR):39 dBm

- 整个生命周期

- 高输入 IP3:−4 dBm

- 低电源电流

- 接收操作:5 V 时为 120 mA(典型值)

- 传输操作:5 V 时为 15 mA(典型值)

- 正逻辑控制

- 5 mm × 3 mm 24 引脚 LFCSP 封装

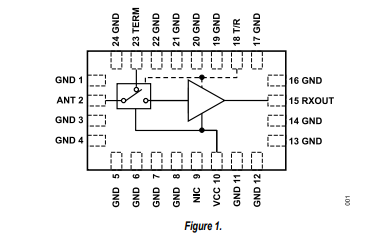

框图

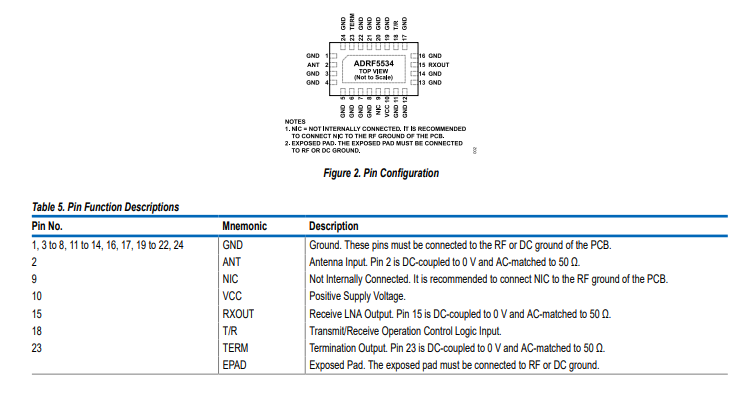

引脚配置

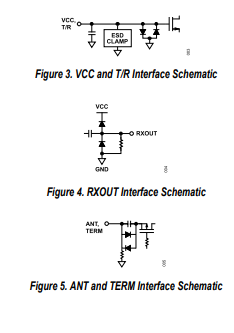

接口示意图

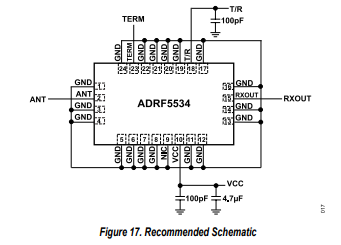

ADRF5534有一个电源引脚(VCC)和一个控制引脚(T/R)。图17显示了电源和控制引脚的外部元件和连接。VCC引脚通过一个100 pF多层陶瓷电容和一个4.7 uF电容去耦。T/R引脚通过一个100 pF多层陶瓷电容去耦。器件引脚排列允许去耦电容靠近器件放置。RF引脚(ANT、TERM、rxut)不需要外部DC隔直电容;所有引脚均通过高阻抗下拉至0 V DC。详情参见表5。

。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADRF5545A:2.4 GHz - 4.2 GHz双信道接收器前端模块深度解析2026-01-14 449

-

Analog Devices Inc. ADRF5354射频前端多芯片模块数据手册2025-06-15 1021

-

ADRF5545A双通道2.4 GHz至4.2 GHz接收器前端技术手册2025-03-11 1287

-

ADRF5515A双通道,3.3GHz至4.0GHz,20W接收器前端技术手册2025-03-10 1592

-

ADRF5519双通道,2.3GHz至2.8GHz,20W接收器前端技术手册2025-03-05 1410

-

ADRF5534:3.1千兆赫至4.2千兆赫,接收者前端数据表 ADI2023-10-10 65

-

UG-1587:评估ADRF5547双通道,3.7 GHz至5.3 GHz,接收器前端2021-05-21 935

-

UG-1676:评估ADRF5549双通道,1.8 GHz至2.8 GHz,接收器前端2021-05-13 754

-

ADRF5549:接收器前端,双通道,1.8 GHz至2.8 GHz数据表2021-05-08 892

全部0条评论

快来发表一下你的评论吧 !