ADRF5023硅SPDT开关,非反射式,9kHz至45GHz技术手册

描述

概述

ADRF5023是一款非反射式、单刀双掷(SPDT)开关,采用硅工艺制造。

ADRF5023的工作频率范围为9 kHz至45 GHz,典型插入损耗为1.7 dB,隔离度为42 dB。该器件的直通路径、端接路径和RF公共端口热切换分别具有30 dBm、24 dBm和30 dBm的RF输入功率处理能力。

ADRF5023需采用3.3 V正电源和−3.3 V负电源供电。该器件采用互补金属氧化物半导体(CMOS)/低压晶体管对晶体管逻辑(LVTTL)兼容控制。

当负电源电压(V SS )接地时,ADRF5023也可在单一正电源电压(V DD )下工作。在此工作条件下,可在降低开关特性、线性度和功率处理性能的同时保持小信号性能。

ADRF5023采用符合RoHS标准的20引脚、3.0 mm × 3.0 mm、基板栅格阵列(LGA)封装,工作温度范围为−40°C至+105°C。

数据表:*附件:ADRF5023硅SPDT开关,非反射式,9kHz至45GHz技术手册.pdf

特性

- 超宽带频率范围:9 kHz 至 45 GHz

- 非反射设计

- 低插入损耗

- 18 GHz 时为 0.9 dB

- 40 GHz 时为 1.6 dB

- 45 GHz 时为 1.7 dB

- 高隔离:45 GHz 时为 42 dB

- 高输入线性度:

- 0.1 dB 功率压缩 (P0.1dB):31 dBm

- 3 阶交调点 (IP3):53 dBm

- T

CASE= 85°C 时具有高功率处理能力- 30 dBm 直通路径

- 24 dBm 终止路径

- 30 dBm 热切换(RFC 端口)

- RF 建立时间(0.1 dB 最终 RF 输出):3.5 μs

- 无低频杂散信号

- 全关闭状态控制

- 正向控制接口:与 CMOS/LVTTL 兼容

- 20 引脚、3.0 mm × 3.0 mm LGA 封装

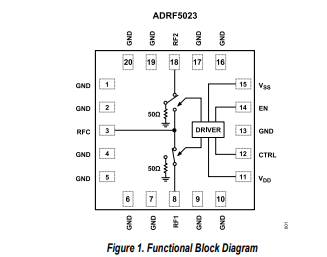

框图

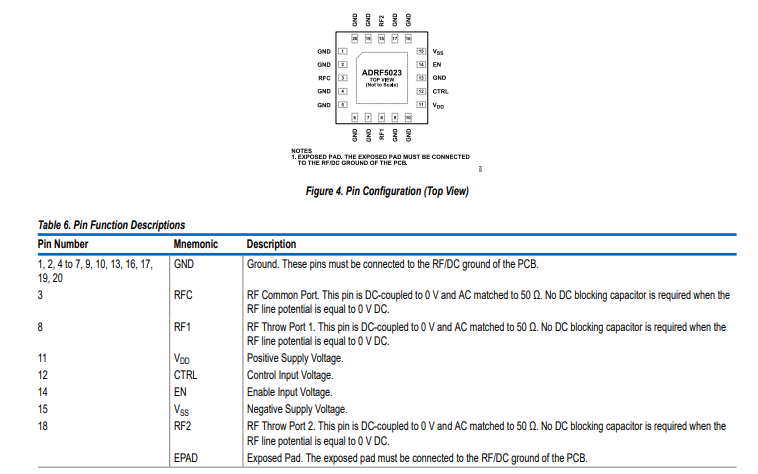

引脚配置

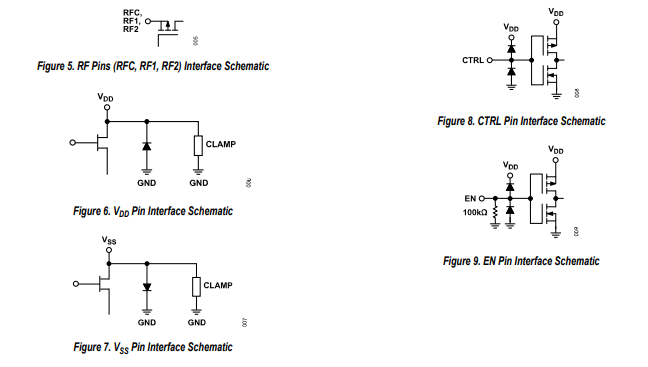

接口示意图

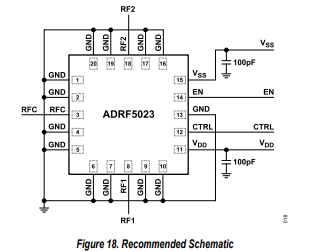

ADRF5023有两个电源引脚(VDo和Vss)和两个控制引脚(CTRL和EN)。图18显示了电源和控制引脚的外部元件和连接。Voppin和Vss引脚通过一个100pF多层陶瓷电容去耦。器件引脚排列允许去耦电容靠近器件放置。偏置和工作不需要其它外部元件,但当RF线路偏置0 V以外的电压时,RF引脚上的DC隔直电容除外,详情参见“引脚配置和功能描述”部分。

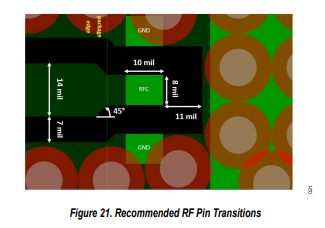

图21显示了参考叠层上从器件RF引脚到50ωCPWG的推荐布局。PCB焊盘与器件焊盘的比例为1:1。接地焊盘绘制为阻焊层定义,信号焊盘绘制为焊盘定义。PCB焊盘的RF走线以相同宽度延伸至封装边缘,并以45°角逐渐变细至RF走线。屏蔽罩还被设计成在没有任何孔径减小的情况下与衬垫相匹配,并且被分成用于桨的多个开口。

-

Analog Devices Inc. ADRF5023单刀双掷 (SPDT) 硅开关数据手册2025-06-17 1070

-

ADRF5049硅SP4T开关,非反射式,9 kHz至45 GHz技术手册2025-03-05 1473

-

ADRF5031 9kHz至20GHz、非反射式、硅SPDT开关技术手册2025-03-04 1106

-

ADRF5023 硅SPDDT开关、无反射、9千赫至45千兆赫数据表 ADI2023-10-11 57

-

ADRF5024硅SPDT开关,反射式,100 MHz至44 GHz数据表2021-05-28 745

-

ADRF5301:硅SPDT开关,反射式,35 GHz至44 GHz初步数据表2021-05-17 850

-

ADRF5047:硅SP4T开关,反射式,9 kHz至44 GHz数据表2021-04-24 785

-

ADRF5025:硅SPDT开关,反射式,9 kHz至44 GHz数据表2021-04-19 701

-

ADRF5024:硅SPDT开关,反射式,100 MHz至44 GHz数据表2021-04-09 917

-

ADRF5300:评估ADRF5300,硅片,SPDT开关,反射式,24 GHz至32 GHz用户指南18862021-03-22 930

全部0条评论

快来发表一下你的评论吧 !