14路差分输出时钟抖动消除器SC6302,兼容HMC7044

描述

SC6302是一款兼容HMC7044的高性能双环路整数、小数分频抖动衰减器,能够执行频率转换、选择参考信号并生成超低相位噪声的时钟提供给并行或串行(JESD204B)接口的高速数据转换器。SC6302提供14路低噪声且可配置的输出,可以灵活地匹配RF收发器系统中的许多不同器件接口,比如数据转换器、本振、发送/接收模块、FPGA和数字前端(DFE)ASIC。

SC6302可产生最多7对DCLK和SYSREF,符合JESD204B接口要求。该器件具有出色的串扰、频率隔离以及杂散性能,支持单端和差分输出频率。DCLK和SYSREF时钟输出可配置为不同的输出信号标准,如CML、LVDS、LVPECL和LVCMOS。

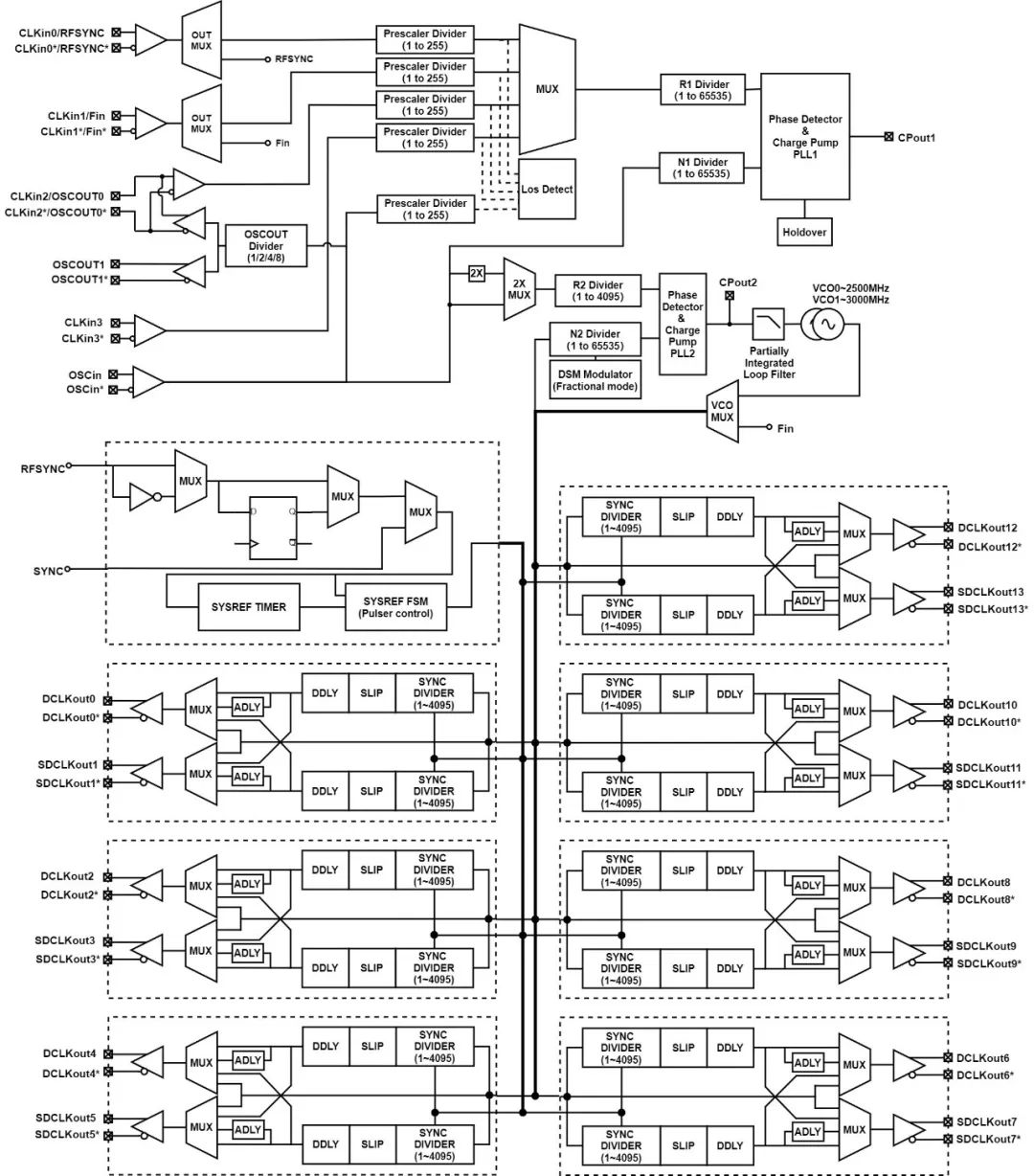

SC6302功能模块示意图

主要性能:

• 支持JEDEC JESD204B

• 超低RMS抖动

48fs RMS Jitter(12kHz到20MHz)@2457.6M

底噪:-153dBc/Hz@2457.6MHz

• PLL2可提供多达14路差分时钟

最多7个SYSREF时钟

时钟最大输出频率3.2GHz

支持LVPECL,LVDS,CML等输出接口

• 支持最多2个缓冲压控振荡器(VCXO)输出

• 信号丢失(LOS)检测和无中断参考切换

• 4 个GPIO报警/状态指示器

• 支持最高3200MHz的外部VCO输入

• 工作温度:-40℃到85℃

• 工作电压:3.15V到3.45V

• QFN-68封装

应用场景:JESD204B时钟产生、无线基础设施(多载波GSM、LTE、W-CDMA)、数据转换器时钟、微波基带卡、相控阵参考分配

注:如涉及作品版权问题,请联系删除。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HMC7044想输出8个不同相位的频率具体该如何操作?2026-05-12 47

-

HMC7044输出信号有vco/2的杂散怎么解决?2026-05-09 55

-

高性能时钟管理利器:HMC7044B深度解析2026-03-26 563

-

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B2025-05-08 1364

-

HMC7044外参考时钟切换失败的原因?2025-04-15 3108

-

hmc7044使用外部VCO时钟输入时,如何使得时钟能够相位对齐 ?2023-12-01 1251

-

UG-826:评估HMC7044双环时钟抖动清除器2021-05-12 1010

-

HMC7044 IBIS型号2021-03-24 806

-

HMC7044: 带 JESD204B 接口的高性能、3.2 GHz、14 路输出抖动衰减器2021-03-21 1726

-

AD9524:带6路差分或13路LVCMOS输出的抖动净化器和时钟发2021-03-19 770

-

HMC7044时钟输出不稳定2019-11-17 6356

-

请问HMC7044的环路带宽能用什么工具来仿真?2019-02-21 4736

-

请问HMC7044锁相环可以配出8路2.5G,相位可调的时钟吗?2018-08-02 4326

全部0条评论

快来发表一下你的评论吧 !