LTC6417 1.6GHz 低噪声、高线性度、差分缓冲器/16位ADC驱动器技术手册

描述

概述

LTC6417 是一款差分单位增益缓冲器,能够以极低的噪声和卓越的线性度来驱动一个 50Ω 负载。 该器件非常适合于采用频率范围为 DC 至高于 600MHz 的输入信号来驱动高速 14 位和 16 位流水线 ADC。 差分输入阻抗为 18.5kΩ,因而允许在输入端上使用 1:4 和 1:8 变压器,以在 50Ω 系统中实现额外的系统增益。

由于未采用外部偏置或增益设定组件,并运用了直通式引出脚配置,因此 LTC6417 非常容易使用。 该器件可进行 DC 耦合,并具有一个 -60mV 的共模输出偏移电压。 对于 AC 耦合应用,在内部对 LTC6417 的输入引脚施加偏压,以提供一个由 VCM引脚上的电压所设定的输出共模电压。

电源电流通常为 123mA,而且 LTC6417 可在 4.75V 至 5.25V 的电源电压范围内运作。 功耗可通过 PWRADJ 引脚降低至 74mA。 另外,LTC6417 还具有一种硬件停机功能,该功能可将电流消耗减小至 24mA。

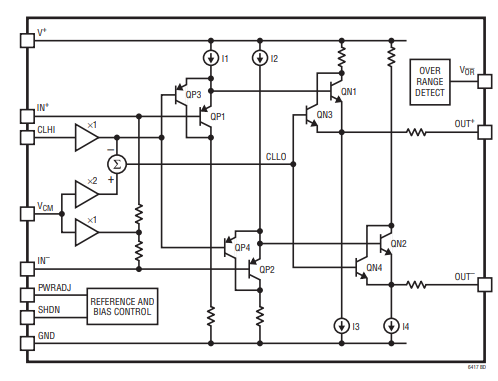

LTC6417 具有快速、可调的输出电压箝位功能电路,可帮助保护位于其后的电路。 CLHI 引脚负责设定最大摆幅,而一个对称的最小摆幅则在内部设置。 当箝位电路限制输出电压时,LTC6417 的 VOR 引脚将发出“超范围”的指示信号。

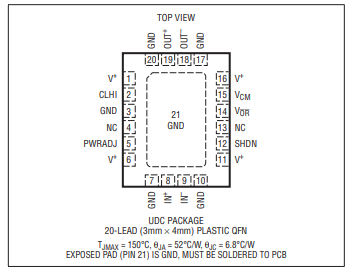

LTC6417 采用 20 引脚 3mm x 4mm QFN 封装。 该器件对引出脚配置进行了优化,以便直接布设在靠近凌力尔特的高速 14 位和 16 位 ADC 的地方。

数据表:*附件:LTC6417 1.6GHz 低噪声、高线性度、差分缓冲器 16位ADC驱动器技术手册.pdf

应用

- 差分 ADC 驱动器

- CCD 缓冲器

- 电缆驱动器

- 50Ω 缓冲器

特性

- 1.6GHz -3dB 小信号带宽

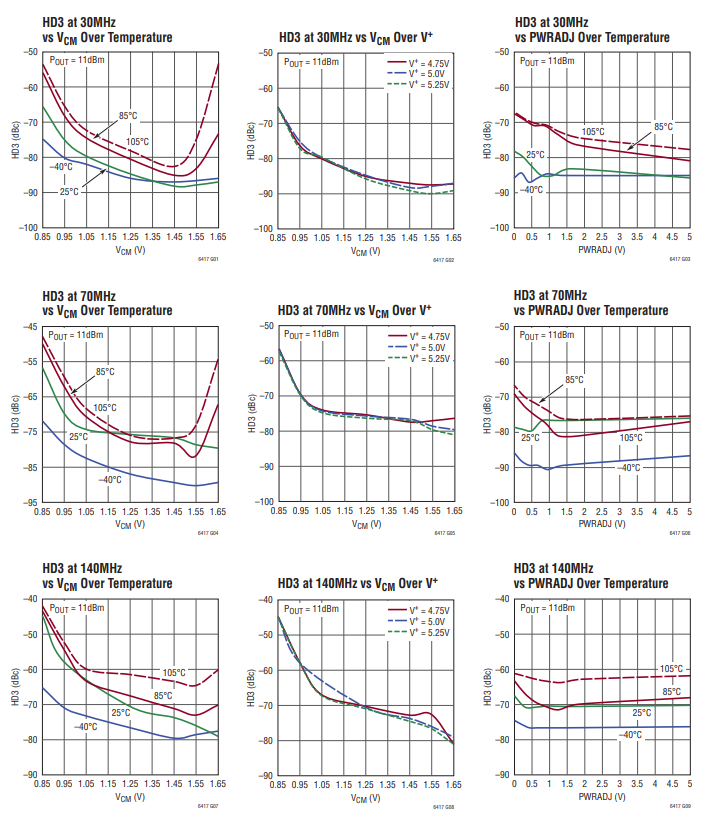

- 低失真 (驱动 50Ω 负载,2.4VP-P 输出)

- -100dBc/-69dBc HD2/HD3 (在 140MHz)

- -80dBc IM3 和 46dBm OIP3 (在 140MHz)

- -100dBc/-66dBc HD2/HD3 (在 380MHz)

- -68dBc IM3 和 39dBm OIP3 (在 380MHz)

- 1.5nV/√Hz 输出噪声

- 4.3pA/√Hz 输入电流噪声

- 可编程高速、快速恢复输出箝位

- 在一个 50Ω 差分负载上的最大输出摆幅为 4.28VP-P

- DC 耦合的信号通路

- 采用 4.75V 至 5.25V 单工作电源

- 功率:采用 5V 电源时为 615mW,可减低至 370mW,停机模式为 120mW

- 3mm x 4mm 20 引脚 QFN 封装

典型应用

引脚配置和功能描述

典型性能特征

框图

LTC6417是一款低噪声、低失真、全差分单位增益ADC驱动器,其–3dB带宽范围为DC至1.6GHz,差分输入阻抗为18.5欧姆,差分输出阻抗为392欧姆。LTC6417由一个全差分缓冲器组成,输出端没有输出共模电压控制电路和高速限压箝位。低通或带通滤波器只需少量外部元件即可轻松实现。LTC6417在I/O耦合方面非常灵活。它可以在输入端和/或输出端交流耦合或DC耦合。使用带直流耦合输入的LTC6417时,输入共模电压在1V至1.5V之间时可获得最佳性能。对于交流耦合操作,LTC6417将采用施加于VcM引脚的电压,并用它来偏置输入,使输出共模电压等于VcM,因此不需要外部电路。VcM引脚设计用于与Linear Technology高速ADC系列中的VcM引脚直接接口。

LTC6417具有18.5千欧的高差分输入阻抗。差分输入可能需要端接至较低值的阻抗,例如502,以便为信号源提供阻抗匹配。图1显示了使用1:1巴伦的输入匹配和单端到差分转换,而图2显示了使用1:4巴伦实现额外6dB电压增益的类似电路。这些电路提供宽带阻抗匹配。巴伦和匹配电阻必须靠近输入引脚放置,以便将输入不匹配引起的抑制降至最低。在图1和图2中,两个输入端接电阻的电容中心抽头可提高高频共模抑制性能。作为这种宽带方法的替代方案,可以在LTC6417的输入端使用窄带阻抗匹配来进行频率选择和/或降噪。

LTC6417应用电路的噪声系数也取决于输入端接。例如,图2中的输入1:4巴伦通过在输入端增加6dB的电压增益来改善噪声系数。当恒定噪声系数圆和恒定增益圆绘制在同一输入史密斯图中时,增益和噪声之间的权衡是显而易见的。这种技术可以用来确定给定增益和噪声要求下的最佳源阻抗。

-

LTC6417:高性能差分缓冲器的深度剖析与应用探索2026-01-12 435

-

1.6-2.2 GHz 高线性度、有源偏置、低噪声放大器 skyworksinc2025-10-21 67

-

LTC6416 2GHz、低噪声、差分16位ADC缓冲器技术手册2025-03-14 1575

-

ADC驱动器的理想之选:低噪声全差分运放SC75162024-10-25 3437

-

驱动16位ADC的差分单位增益缓冲器——LTC64162022-11-09 1590

-

LTC6417:1.6 GHz低噪声高线性度差分缓冲器/16位ADC驱动器,带快速钳位数据表2021-05-23 903

-

LTC6416:2 GHz低噪声差分16位ADC缓冲器数据表2021-04-29 746

-

LTC6401-14:2 GHz低噪声、低失真DC-140 MHz差分ADC驱动器数据表2021-04-24 739

-

LTC6417的主要功能是什么?2020-03-18 1350

-

LTC6417 具快速箝位的 1.6GHz 低噪声、高线性度、差分缓冲器 / 16 位 ADC 驱动器2019-02-15 451

-

凌力尔特推出全差分缓冲放大器 LTC64172012-08-17 4999

-

LTC6416-2GHz、低噪声、差分16位ADC缓冲器2010-11-27 1347

-

差分单位增益缓冲器LTC64162010-09-13 2255

全部0条评论

快来发表一下你的评论吧 !