GaN E-HEMTs的PCB布局经验总结

描述

本文介绍了应用GaN Systems器件的PCB布局设计原则, 包含以下四种电路:

- 单管GaN E-HEMTs 的隔离驱动电路

- 并联GaN E-HEMTs 的隔离驱动电路

- 半桥自举门极驱动电路

- EZDriveSM 电路

• 优化的电路板布局和极低的封装电感是优化氮化镓器件开关性能的关键

** 为什么我们需要优化PCB layout?**

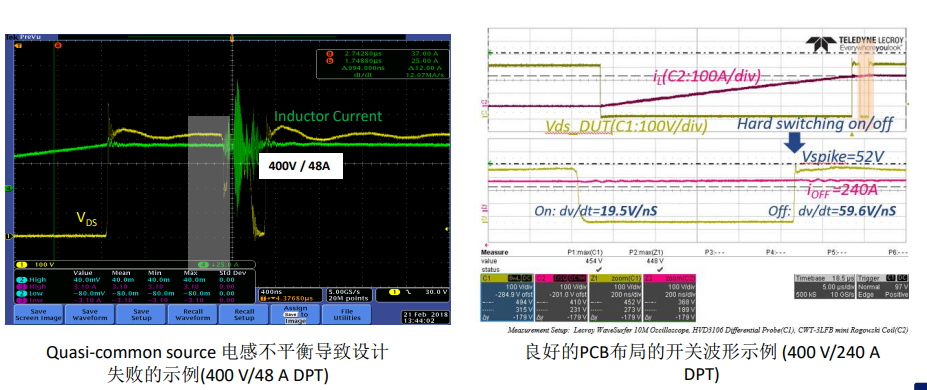

GaN 增强型器件开关速度远快于Si MOSFETs, 所以需要恰当的PCB 布局设计以减小寄生电感

寄生电感会导致较高的过冲电压, 振荡, 和EMI问题, 使得GaN器件承受过大的电气应力

GaN E-HEMT的PCB布线考虑

GaN E-HEMTs的PCB布局总结

一、总述

- 内容:本文件介绍了应用GaN Systems器件的PCB布局设计原则,涵盖单管GaN E-HEMTs的隔离驱动电路、并联GaN E-HEMTs的隔离驱动电路、半桥自举门极驱动电路以及EZDrive SM电路。

- 关键点:优化的电路板布局和极低的封装电感是优化氮化镓器件开关性能的关键。

二、PCB布局的重要性

- 开关速度:GaN增强型器件的开关速度远快于Si MOSFETs,需要恰当的PCB布局设计以减小寄生电感。

- 寄生电感影响:寄生电感会导致较高的过冲电压、振荡和EMI问题,增加GaN器件承受的电气应力。

三、PCB布局步骤

步骤1:确定原理图

- 确定每个关键电路的构成,包括单管GaN器件的隔离驱动电路、并联GaN器件的隔离驱动电路、半桥自举门极驱动电路和EZDrive SM电路。

步骤2:放置组件

- 原则:将组件尽可能靠近放置,根据当前电流方向依次设置组件。

- 优先级:根据设计优先级最小化所有回路,具体优先级根据电路类型(如功率换流回路、门极驱动回路等)确定。

步骤3:连接组件

- 技术:通过磁通消除技术降低寄生电感,即调整layout使高频电流在两个相邻的PCB层上以相反的方向流动,从而抵消磁通量。

四、具体电路设计原则

1. 单管GaN器件的隔离驱动电路

- 功率换流回路:Q1, Q2, C_BUS应尽可能小。

- 门极驱动回路:开通和关断回路中的组件(如C5, U1, R_gon, Q2等)应靠近放置。

2. 并联GaN器件的隔离驱动电路

- 功率换流回路:Q1, Q2, C_BUS应尽可能小,并联器件应尽可能对称。

- 门极驱动回路:每个器件的开通和关断回路应独立设计,确保电流平衡。

3. 半桥自举门极驱动电路

- 功率换流回路:Q1, Q2, C_BUS应尽可能小。

- 门极驱动回路:上管和下管的开通和关断回路应独立设计,使用自举电容和二极管提供上管门极驱动电压。

4. EZDrive SM电路

- 功率换流回路:Q1, Q2, C_BUS应尽可能小。

- 门极驱动回路:使用集成驱动的控制器和额外的电阻、电容组件来优化门极驱动回路。

五、磁通消除技术应用

- 原理:当两个相邻的导体以相反的电流方向靠近放置时,两个电流产生的磁通量将相互抵消,从而降低寄生电感。

- 实施:在PCB设计中,通过调整走线布局,使高频电流在两个相邻层上以相反方向流动,实现磁通抵消。

六、总结

- 优化布局:良好的PCB布局对于充分发挥GaN器件的性能至关重要,可以显著减小寄生电感,降低过冲电压和振荡。

- 设计原则:遵循关键电路设计原则,如最小化功率换流回路和门极驱动回路的电感,确保组件的适当放置和连接。

- 磁通消除:利用磁通消除技术进一步降低寄生电感,提高电路的稳定性和效率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- GaN

- PCB布局

- Pcb layout

- PCB

-

氮化镓系统 (GaN Systems) E-HEMTs 的EZDriveTM方案2025-03-13 6364

-

选择烧结银的经验总结2023-12-17 2507

-

EMI整改经验总结2021-12-20 1662

-

电路设计的一些经验总结2021-12-02 1372

-

指针经验总结2017-10-27 1020

-

模拟电路设计经验总结2016-09-27 1262

-

开关电源测量的经验总结2016-09-18 1001

-

手机RF射频PCB板布局布线经验总结2016-07-26 1577

-

麦斯艾姆的资深工程师PCB电路板设计经验总结2016-03-24 1145

-

做四轴飞行器的经验总结2015-11-11 867

-

线圈天线设计经验总结2013-09-12 1541

-

电子产品设计经验总结之PCB2012-08-12 4196

-

PCB板绘制经验总结2010-09-19 4023

-

SOPC Builder/Nios 学习经验总结2009-07-22 776

全部0条评论

快来发表一下你的评论吧 !