数据手册#TPS703系列 1-A,双通道超低压差稳压器,具有电源正常和启用功能

描述

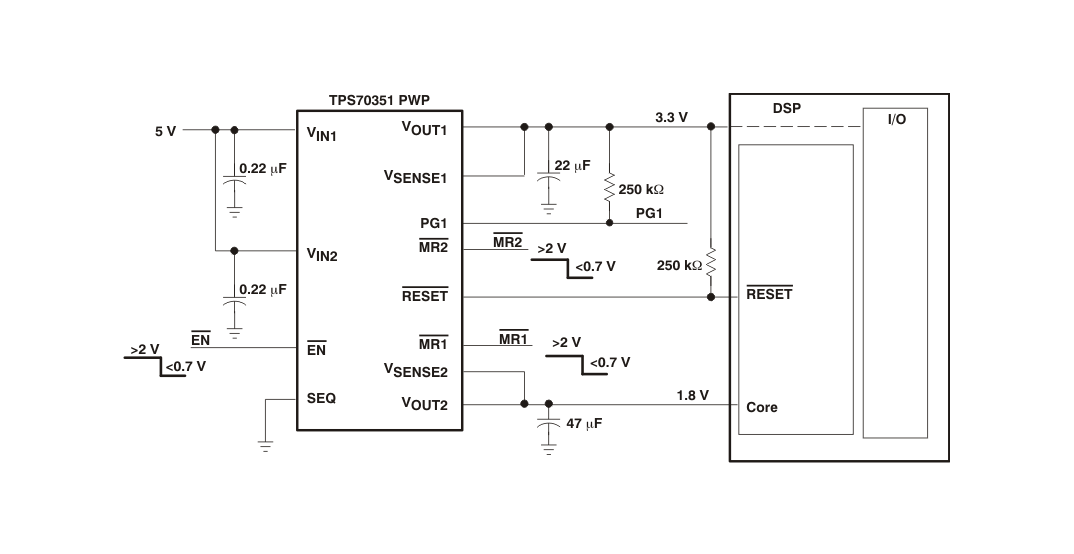

TPS703xx 系列器件旨在为需要双输出电压稳压器的 TI DSP、处理器电源、ASIC、FPGA 和数字应用提供完整的电源管理解决方案。时序控制功能易于编程,使该系列非常适合任何具有电源时序要求的 TI DSP 应用。精度、快速瞬态响应、SVS 监控电路(上电复位)、手动复位输入和使能功能等差异化功能提供了完整的系统解决方案。

TPS703xx 系列稳压器提供极低的压差和双输出,具有上电顺序控制功能,主要为 DSP 应用而设计。这些器件具有低噪声输出性能,无需使用任何额外的滤波器旁路电容器,并且设计为具有快速瞬态响应,并在使用 47 μF 低 ESR 电容器时保持稳定。

*附件:tps703 用于分压系统的双输出、低压差电压调节器,带集成 SVS 数据表.pdf

这些器件具有固定的 3.3 V/2.5 V、3.3 V/1.8 V、3.3 V/1.5 V、3.3 V/1.2 V 和可调电压选项。稳压器 1 可支持高达 1 A 的电流,稳压器 2 可支持高达 2 A 的电流。单独的电压输入允许设计人员配置电源。

由于 PMOS 传输元件充当低阻值电阻器,因此压差非常低(稳压器 1 上通常为 160mV),并且与输出电流成正比。此外,由于 PMOS 传输元件是电压驱动器件,因此静态电流非常低,并且与输出负载无关(在整个输出电流范围内最大为 250 μA)。该 LDO 系列还具有休眠模式;向 EN(使能)施加高信号会关断两个稳压器,从而将 T 时的输入电流降低到 1 μA J = +25°C 的 10 个温度。

当 EN 引脚连接到低电平输入电压时,该器件使能。两个稳压器的输出电压在 V 处感应感官1和 V感官2引脚。

SEQ 引脚的输入信号控制两个稳压器的上电顺序。当设备启用且 SEQ 端子被拉高或保持打开状态时,V输出 2首先打开 V,然后打开 V输出 1保持关闭状态,直到 V输出 2达到其稳压输出电压的约 83%。当时 V输出 1处于打开状态。如果 V输出 2被拉至其稳压 V 的 83% 以下(即在过载条件下)输出 1已关闭。将 SEQ 端子拉低可反转上电顺序,并将 V输出 1首先打开。SEQ 引脚连接到内部上拉电流源。

对于每个稳压器,都有一个内部放电晶体管,用于在稳压器关闭(禁用)时对输出电容器放电。

PG1 引脚报告 V 处的电压条件 输出 1 .PG1 引脚可用于为稳压器 1 提供的电路实现 SVS (POR,或上电复位)。

特性

- 用于双电源供电应用的双输出电压

- 独立启用功能(有关每个输出的独立启用

,请参见部件号 TPS704xx) - 稳压器 1 上的输出电流范围为 1 A,稳压器 2 上的输出电流范围为 2A

- 快速瞬态响应

- 电压选项:3.3 V/2.5 V、3.3 V/1.8 V、3.3 V/1.5 V、3.3 V/1.2 V

和双可调输出 - 漏极开路上电复位,延迟 120 ms

- 漏极开路电源适合稳压器 1

- 185 μA(典型值)超低静态电流

- 待机期间 2 μA 输入电流

- 低噪声:78 μV

RMS无旁路电容器 - 快速输出电容器放电功能

- 两个手动复位输入

- 2% 的负载和温度精度

- 欠压锁定 (UVLO) 功能

- 24 引脚 PowerPAD™ TSSOP 封装

- 热关断保护

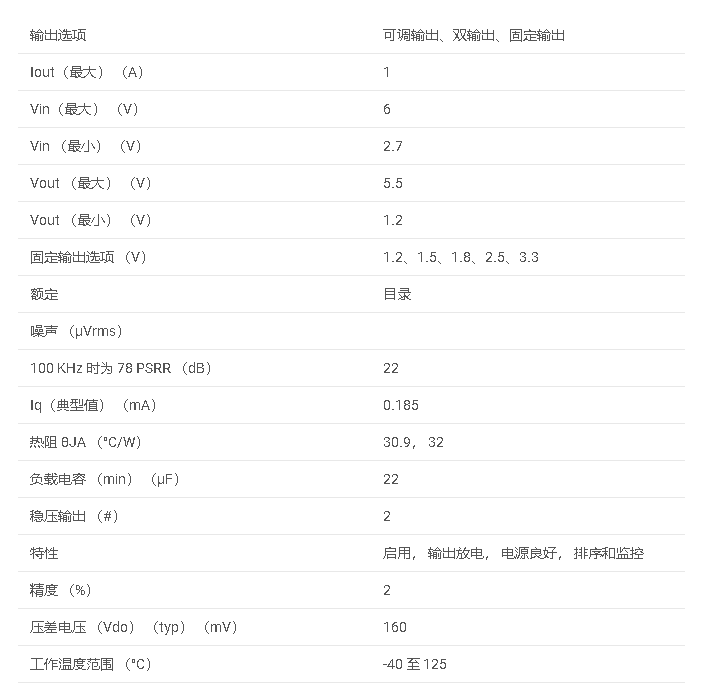

参数

方框图

1. 产品概述

TPS703xx 系列是一款专为分压系统设计的双输出低压差(LDO)电压调节器,集成了电源监控系统(SVS)。该系列提供多种电压选项,支持高达 1A 和 2A 的输出电流,适用于需要高性能电源管理的应用,如 DSP、ASIC、FPGA 和数字应用。

2. 主要特性

- 双输出电压:支持两个独立的输出电压,满足不同电路模块的供电需求。

- 独立使能功能:允许对每个输出进行独立控制,提高电源管理的灵活性。

- 集成 SVS:内置电源监控系统,包括电源良好(PG)和复位(RESET)信号,增强系统可靠性。

- 可编程上电顺序:通过 SEQ 引脚控制两个输出的上电顺序,满足特定应用需求。

- 快速瞬态响应:提供快速瞬态响应,确保负载变化时输出电压的稳定。

- 低噪声和低静态电流:输出噪声低,静态电流仅为 185μA(典型值),有助于延长电池寿命。

3. 电气特性

- 输出电压范围:提供多种固定电压(如 3.3V/2.5V、3.3V/1.8V 等)和可调电压选项。

- 输出电流:稳压器 1 支持高达 1A 的输出电流,稳压器 2 支持高达 2A 的输出电流。

- 输入电压范围:通常为 2.7V 至 6V,具体取决于输出电压选项。

- 线性调整率和负载调整率:具有优异的线性调整率和负载调整率,确保输出电压的精度和稳定性。

4. 保护功能

- 欠压锁定(UVLO) :防止输入电压过低时损坏电路或影响输出电压。

- 热关断保护:当结温超过设定值时,自动关闭输出,防止过热损坏。

- 输出短路保护:内置短路保护电路,防止输出短路时损坏稳压器。

- 电流限制:在输出电流过大时自动限制电流,防止损坏电路。

5. 应用场景

- 数字信号处理(DSP)应用:需要高性能、高可靠性电源管理的 DSP 系统。

- 通信系统:如基站、路由器等,需要双路独立供电和快速瞬态响应的应用场景。

- 工业控制:需要高稳定性和可靠性的电源监控系统。

6. 封装与尺寸

采用 24 引脚 PowerPAD™ TSSOP 封装,尺寸紧凑,适合高密度 PCB 布局。

7. 额外功能

- 两个手动复位输入:允许用户通过外部信号触发复位操作。

- 输出电容快速放电:关闭稳压器时,输出电容可快速放电,提高系统安全性。

-

TPS754系列 2-A,超低压差稳压器数据手册2025-03-14 1022

-

数据手册#TPS759系列 7.5-A,超低压差稳压器,电源正常并启用2025-03-13 1368

-

TPS712系列 具有启用功能的 250mA 双通道低压差稳压器数据手册2025-03-11 1019

-

TPS746 1-A,低IQ,高精度,可调超低压差电压调节器,具有电源正常和启用功能2025-02-28 1095

-

具有电源正常指示功能的500mA超低压降稳压器TPS745-Q1数据表2024-03-29 525

-

快速瞬态响应1-A低压差稳压器TPS767系列数据表2024-02-29 572

-

用于LT1431超低压差稳压器的简单超低压差稳压器2019-06-12 1968

-

AZ2940 1A超低压差线性稳压器的典型应用2019-04-24 2863

全部0条评论

快来发表一下你的评论吧 !