单片机控制的动态数据缓存器的控制电路

电子说

1.3w人已加入

描述

由于单片机具有功能强,使用灵活,体积小,性价比高等特点,近年来在测控系统中得到广泛应用。而在许多场合,单片机作为下位机,担负着控制数据测量、采集和向上位机传送的任务,也即起着收集、缓冲和存储数据的作用。动态存储器DRAM具有容量大,价格低的特点,适合于数据量比较大的单片机应用系统;但其不足之处在于,必须在规定的时间范围内进行定时刷新。本节介绍一种单片机控制的动态数据缓存器,通过合理设计软硬件,即可实现对DRAM的控制,特别适合性价比高的单片机系统。

控制电路

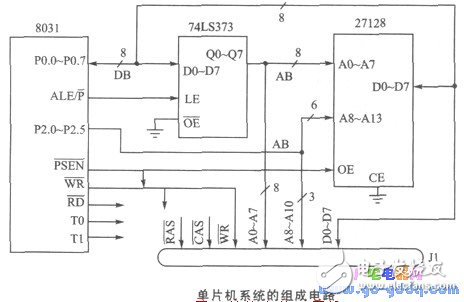

为了便于说明,给出单片机系统的部分组成电路,如图1所示。单片机采用51系列的8031,外扩16 KB的EPROM,动态存储器采用1 MB的微机内存,Jl为其插座及其各引脚信号。1 MB的动态存储器行、列地址各用10位,即用10根地址线A0~A9。

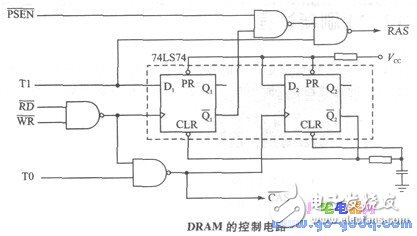

DRAM的控制电路如图2所示。其核心为一正沿触发双D触发器74LS74,由8031和TO、Tl、PSEN和EN、WR信号控制其工作状态。读/写数据时,TO、Tl置高电平;刷新DRAM时,TO置1,PSEN有效;当T0、T1都置0时,行、列选通关闭,禁止对DRAM读/写操作。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- �

-

基于单片机控制的MP3控制电路2013-05-21 0

-

基于单片机的交流调压触发控制电路设计2015-04-07 0

-

单片机控制电路2016-12-08 0

-

设计一个单片机维电器控制电路。2019-04-15 0

-

基于单片机和CPLD的步进电机控制电路2022-04-02 0

-

单片机控制触发电路2008-03-22 965

-

AT89C2051单片机做节日彩灯控制电路程序2008-10-14 1059

-

基于单片机的直流电机控制系统在动态送风装置中的应用2010-07-21 457

-

51单片机温度控制电路2008-06-07 4186

-

单片机控制LED灯电路图2009-11-13 19192

-

采用单片机的电子密码锁控制电路2016-02-17 425

-

控制电路与单片机2016-05-10 684

-

一种基于单片机系统的DMA控制电路的模块化设计方案2017-01-14 952

-

单片机的挡车器控制电路改造2018-01-18 731

-

如何使用51单片机制作硬盘控制电路?包括控制电路和程序2018-10-10 1074

全部0条评论

快来发表一下你的评论吧 !