LTC6412 800MHz、31dB范围模拟控制型VGA技术手册

描述

概述

LTC6412 是一款全差分可变增益放大器,采用对数线性模拟增益控制。 它专为IF接收器链路 (从 1MHz 至 500MHz) 中的 AC 耦合操作而设计。 该器件在一个很宽的输出幅度范围和 31dB 增益控制范围内具有一个恒定的 OIP3。 而且,输出噪声 (NF + 增益) 与增益的关系曲线也是平坦的,以在 240MHz 和整个增益控制范围内提供一个 >120dB 的一致无寄生动态范围 (SFDR)。

LTC6412 非常适合与 LT5527 和 LT5557 下变频混频器、LTC6410-6 IF 放大器以及适合在 12 位、14 位和 16 位 ADC 应用中使用的 LTC6400/ LTC6401/ LTC6416 ADC 驱动器相连。

LTC6412 能够实现从过驱动条件的快速恢复,而且 EN 引脚提供了一种快速输出信号禁用功能,以保护敏感的下游元件。 把 SHDN 引脚置为低有效状态将把电流消耗减小至 1mA 以下,以实现断电或睡眠模式。

数据表:*附件:LTC6412 800MHz、31dB范围模拟控制型VGA技术手册.pdf

应用

- IF 信号链路自动增益控制 (AGC)

- 2.5G 和 3G 蜂窝基站收发器

- WiMAX、WiBro、WLAN 接收器

- 卫星和 GPS 接收器 IF

特性

- 800MHz -3dB 小信号带宽

- 连续可调的增益控制

- -14dB 至 +17dB 对数线性 (Linear-in-dB) 增益范围

- 在所有的增益设定值条件下实现了 35dBm OIP3 (在 240MHz)

- 10dB 噪声系数 (在最大增益条件下)

- 在所有增益条件下 (IIP3 – NF) = +8dBm (在 240MHz)

- 2.7nV/√Hz 输出参考噪声

- 差分输入和输出

- 所有增益条件下的 50Ω 输入阻抗

- 单电源操作从 3V 至 3.6V

- 110mA 电源电流

- 4mm x 4mm x 0.75mm 24 引脚 QFN 封装

典型应用

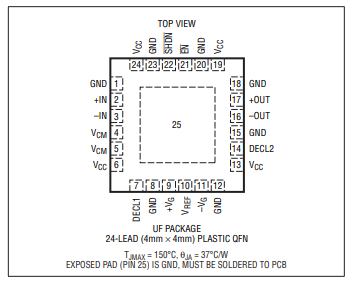

引脚配置

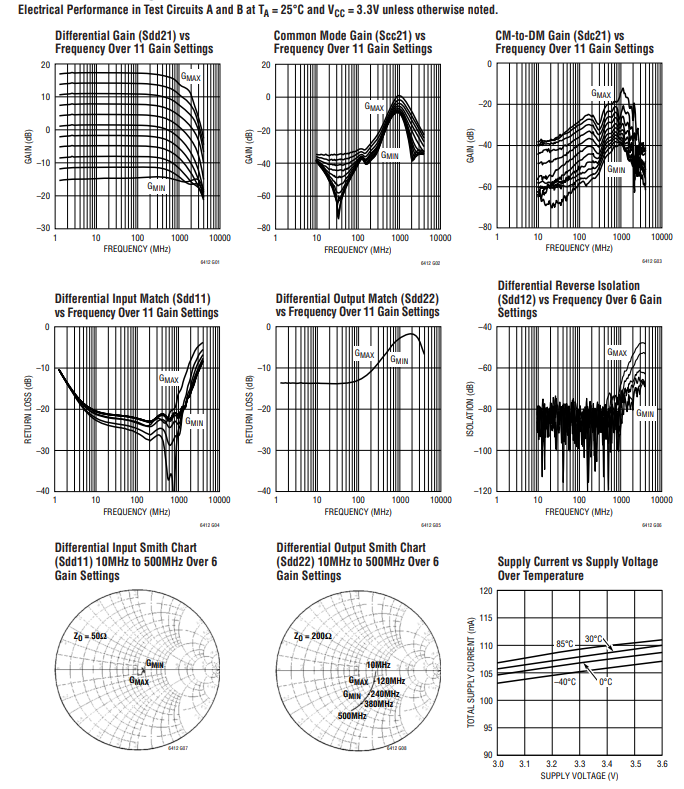

典型性能特征

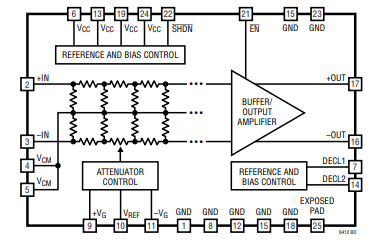

框图

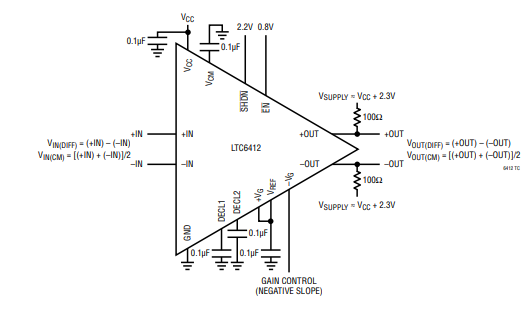

DC测试电路

操作

LTC6412采用插值抽头衰减器电路架构来产生放大器的可变增益特性。抽头衰减器馈入缓冲器和输出放大器,以完成框图所示的差分信号路径。这种电路架构提供良好的RF输入功率处理能力,以及恒定的输出噪声和输出ip3特性,适合大多数中频信号链应用。内部控制电路从VG引脚获取gaincontrol信号,并将其转换为一组适当的控制信号,发送至衰减器或加法器。衰减器控制电路确保线性dB增益响应在慢速和快速移动输入控制信号的增益范围内连续且单调,同时输入阻抗随增益变化极小。这些设计考虑因素导致增益与VG特性曲线具有0.1dB纹波和0.5us增益响应时间,比类似的数字步进衰减器设计要慢。

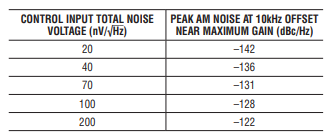

模拟控制VGA的一个常被忽视的特性是来自增益控制端的上变频调幅(AM)噪声。VGA相当于一个二象限乘法器,因此只需很少的注意就可以避免产生过多的AM边带噪声。下表展示了基线的影响LTC 6412电路的20nV//Hz等效输入控制噪声,以及高噪声外部控制电路导致的更高组合输入噪声的影响”

基准等效20nV//Hz输入噪声产生–142 DBC/Hz的最差情况AM边带,接近标称OdBm输出信号最大增益时的-147dBm/Hz输出噪底。一般建议输入控制噪声电压小于80nV//Hz,以避免可测量的AM边带噪声。虽然运算放大器控制电路输出噪声电压通常低于80nV//Hz,但一些低功耗DAC输出超过150nV//Hz。DAC输出噪声在100nV//Hz至150 NV//Hz范围内,通常可以在DAC输出端采用合适的2:1或3:1电阻分压器网络,以相同的比例抑制噪声幅度。如果极小的AM噪声对应用至关重要,则应避免超过150nV//Hz的高噪声DAC。

-

AD8368:800 MHz线性dB VGA的卓越性能与应用解析2026-05-12 135

-

MAX2056:800MHz - 1000MHz可变增益放大器的卓越之选2026-01-15 333

-

深入解析LTC6412:800MHz高性能模拟控制VGA2026-01-12 586

-

MAX2056 800MHz至1000MHz可变增益放大器,具有模拟增益控制技术手册2025-04-22 1121

-

LTC6412 800MHz、31dB 范围模拟控制型VGA技术手册2025-04-21 6118

-

AD8368 800 MHz, 线性dB VGA内置AGC检测器技术手册2025-03-17 1468

-

LTC6412:800 MHz,31dB范围模拟控制VGA数据表2021-05-20 768

-

可变增益放大器LTC6412相关资料分享2021-04-16 679

-

拥有 31dB 模拟控制范围的 800MHz VGA 从 3.3V 电源获得 35dBm OIP32021-03-18 1176

-

为什么800Mhz 90度不工作?2019-04-18 1074

-

LTC6412 800MHz、31dB 范围模拟控制型 VGA2019-02-22 313

-

LTC6412-800MHz、31dB范围模拟控制型VGA2010-11-27 1017

-

MAX2056 pdf datasheet (800MHz2009-02-16 489

全部0条评论

快来发表一下你的评论吧 !