电磁兼容性(EMC)系统化解决方案:基于三要素的工程实践与技术演进

描述

时源 专业EMC解决方案提供商 为EMC创造可能

一、EMC三要素理论模型与工程映射

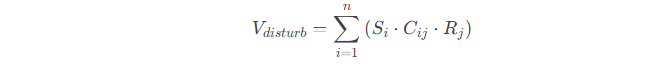

电磁兼容性问题遵循"干扰源-耦合路径-敏感设备"的经典三要素模型,其数学表征可描述为:

(Si:干扰源强度,Cij:耦合系数,Rj:敏感度因子)

1.1 干扰源抑制技术体系

核心干扰源分类与特征:

| 类型 | 典型频谱特性 | 关键参数 |

|---|---|---|

| 开关电源 | 基频(50kHz-2MHz)+宽谐波 | dv/dt≥50V/ns,di/dt≥100A/μs |

| 数字电路 | 时钟谐波(奇次倍频) | Tr/Tf≤1ns,Vpp≥3.3V |

| 电机系统 | 宽带随机噪声(10kHz-1GHz) | 共模电流≥30mA,Lstray≥100nH |

源端抑制关键技术:

器件级优化:

选用第三代半导体器件(SiC/GaN),dv/dt降低至传统硅器件的1/5

采用低寄生电容光耦(Cio≤0.3pF)

拓扑重构:

三电平逆变架构降低共模电压幅值(Vcm从Vdc/2降至Vdc/4)

随机PWM技术将谐波能量扩散至±15%频带

滤波设计规范:

多级LC滤波器网络(截止频率fc=1/(2π√LC))

X电容(0.1-10μF薄膜电容)

共模电感(μi≥5000的铁氧体磁芯)

二、耦合路径阻断策略与量化分析

2.1 传导耦合控制

电缆管理黄金法则:

屏蔽线缆转移阻抗:ZT≤50mΩ/m@30MHz

非屏蔽线处理:

双绞线节距≤50mm(降低辐射效率40%)

穿磁环匝数≥3(镍锌铁氧体μi≥800)

接地系统设计:

| 接地类型 | 适用场景 | 设计要点 |

|---|---|---|

| 单点接地 | 低频模拟电路 | 接地线阻抗≤10mΩ |

| 多点接地 | 高频数字系统 | 网格间距≤λ/20@最高频率 |

| 混合接地 | 混合信号系统 | 通过1nF电容实现高频多点接地 |

2.2 辐射耦合抑制

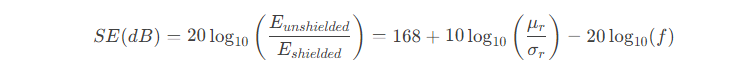

机箱屏蔽效能计算:

(μr:相对磁导率,σr:相对电导率,f:频率)

先进屏蔽技术:

导电复合涂层(厚度50μm,表面电阻≤0.1Ω/sq)

电磁密封衬垫(压缩形变率25%,屏蔽效能≥60dB@1GHz)

三、敏感设备防护技术演进

3.1 硬件防护架构

抗干扰电路设计:

差分信号设计规范:

等长误差≤50mil,间距≥3H(H为参考平面高度)

终端匹配电阻(Z0±1%)

电源净化方案:

三级滤波:10μF钽电容 + 100nF陶瓷电容 + 1nF高频电容

LDO选型:PSRR≥60dB@1MHz(如TPS7A4700)

3.2 软件容错机制

智能抗干扰算法:

自适应数字滤波:

128阶FIR滤波器(截止频率动态调整步长1kHz)

实现60dB带外衰减(过渡带≤5%)

冗余校验协议:

CRC32校验 + 三模冗余表决

误码率从10-6降至10-12

四、典型工程案例分析

4.1 无线通信设备EMC整改

问题描述:

2.4GHz频段接收灵敏度下降20dB

开关电源在12MHz产生传导噪声超标8dB

解决方案:

源端抑制:

采用零电压开关(ZVS)拓扑,将dv/dt从50V/ns降至5V/ns

部署三阶EMI滤波器(fc=100kHz,插损≥40dB@12MHz)

路径阻断:

射频模块与数字电路间设置屏蔽隔舱(SE≥80dB@2.4GHz)

使用双层屏蔽同轴线(内层覆盖率≥95%)

敏感防护:

LNA前端增加带通滤波器(Q≥50,带宽±10MHz)

实施软件跳频算法(跳频速率≥1600hops/s)

整改效果:

传导发射余量+12dB

误码率恢复至10-6(Eb/N0=8dB)

4.2 新能源汽车电机控制器EMC优化

挑战:

需同时满足CISPR 25 Class 5与ISO 11452-2标准

空间受限(安装体积≤200×150×50mm)

创新方案:

干扰源抑制:

采用SiC MOSFET(开关损耗降低70%)

集成式扩频IC时钟芯片(扩频范围±1%,抖动增加≤30ps)

耦合控制:

直流母线层叠设计(回路电感从120nH降至30nH)

纳米晶屏蔽涂层(厚度20μm,SE≥45dB@100MHz)

敏感防护:

CAN总线防护:TVS(2TS24CA) + 共模扼流圈TSLS1608- 1R0MT(100μH)

软件容错:增加CRC16校验与超时重传机制

测试结果:

辐射发射通过Class 5限值(余量6dB)

EFT抗扰度从±2kV提升至±4kV

五、未来技术发展方向

5.1 智能EMC预测系统

基于机器学习的干扰预测:

训练数据集:106组EMC测试数据

预测精度:频点偏差≤±5%,幅度误差≤2dB

5.2 新型材料应用

超材料屏蔽层:

负折射率特性实现定向波束控制

1mm厚度下SE≥100dB@6GHz

5.3 量子抗干扰技术

量子密钥分发:

抗电磁窃听能力提升103倍

相位噪声容限扩展至±π/2

结论:构建全生命周期EMC管理体系

现代电子系统的EMC设计需贯穿产品全生命周期:

设计阶段:基于ANSYS HFSS/Maxwell的协同仿真(误差≤3dB)

测试阶段:执行CISPR 16-4-2风险评估(置信度≥95%)

维护阶段:部署在线监测系统(采样率≥10GSa/s)

通过系统化工程方法,可使EMC整改成本降低40%,开发周期缩短30%。随着5G-Advanced与自动驾驶技术的发展,EMC工程将进入"预防为主、智能调控"的新纪元。

审核编辑 黄宇

- 相关推荐

- 热点推荐

- 电磁兼容

-

设备电磁兼容整改:从原理到实践的系统化解决方案2025-12-02 786

-

EMC工程电磁兼容性测试整改:诊断问题到解决方案2025-04-08 1483

-

EMC电磁兼容性摸底检测测试整改:技术挑战与解决方案2025-04-07 1362

-

电磁兼容性(EMC)系统软件化解决方案:基于三要素的工程实践与技术演进2025-03-20 1009

-

电线EMC电磁兼容性测试整改:定制一体化解决方案2025-02-17 1132

-

EMC电磁兼容性:原理实践,电子设备稳定运行2024-05-20 1449

-

EMC概述(1)——什么是电磁兼容性(EMC)?2023-12-07 2788

-

EMC概述(3)——什么是电磁兼容性(EMC)?2023-12-06 1996

-

电磁兼容三要素的哲学思辨2023-03-14 3321

-

电磁兼容性(EMC)常见问题及解决方案2022-03-30 9993

-

电磁兼容性(EMC)测试的重要性2020-05-22 5969

-

电路保护解决方案之EMC电磁兼容性测试经验分享2019-08-07 2953

-

电磁兼容三要素和三个重要规律2019-07-24 1719

-

浅谈电磁兼容性设计的三规律三要素五层次2019-02-14 5538

全部0条评论

快来发表一下你的评论吧 !