SDRAM控制器设计之signaltap调试

描述

Signal Tap 概述

Signal Tap Logic Analyzer是Intel Quartus Prime设计软件中自带的新一代系统级调试工具,它可以在FPGA设计中采集和显示实时的信号行为。当设计在FPGA上全速运行时,无需额外的I/O引脚即可检查正常器件操作期间内部信号的行为。

Signal Tap Logic Analyzer具有可扩展性,易于使用,支持以下功能:

无需外部设备,通过探测内部信号的状态来调试FPGA设计。

自定义触发条件逻辑,提高准确性并提升分析问题的能力。

将所有捕获的信号数据存储在设备存储器中,直到需要进行读取和分析。

Signal Tap Logic Analyzer支持可编程逻辑市场上任何逻辑分析仪中最多的通道数、最大的采样深度和最快的时钟速度。

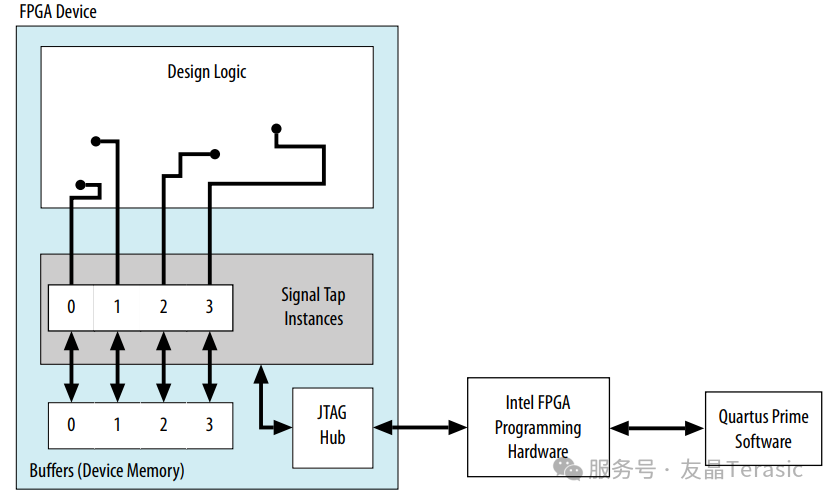

下图1.1是Signal Tap Logic Analyzer内部结构图,它是利用JTAG边界扫描的原理来读取FPGA内部节点的值,然后传输到buffer(缓冲器),再由JTAG把数据送到Quartus下的Signal Tap Logic Analyzer工具。整个过程只读取数据,而数据的频率无法直接知道,只能由设计者自行计算得出。

图1.1 Signal Tap Logic Analyzer结构图

在设计中嵌入Signal Tap Logic Analyzer

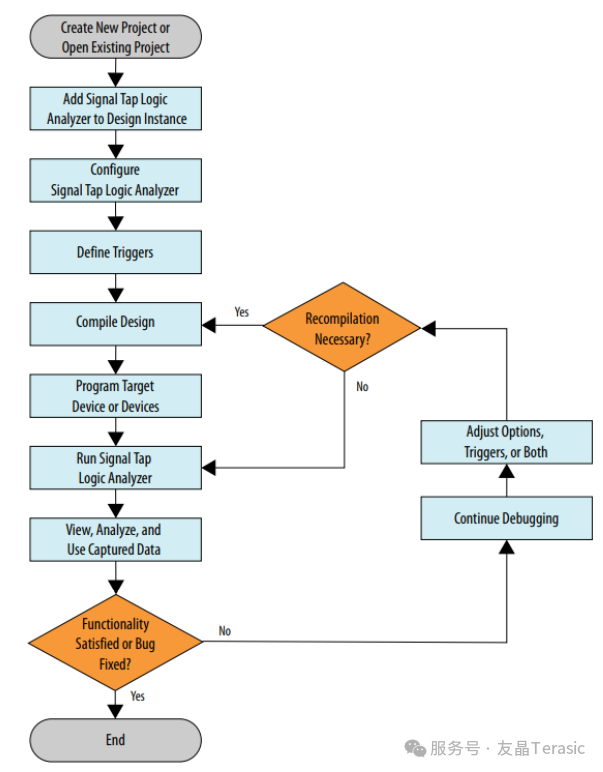

要使用Signal Tap Logic Analyzer对设计进行调试,需要执行几个任务来添加、配置和运行Signal Tap Logic Analyzer。如下图所示为Signal Tap Logic Analyzer任务流程图。

图2.1 Signal Tap Logic Analyzer任务流程图

在设计中嵌入Signal Tap Logic Analyzer有以下两种方法:

建立一个Signal Tap文件,即.stp文件,然后定义该文件的详细内容。

用MegaWizard Plug-In Manager建立并配置.stp文件,然后使用MegaWizard实例化一个HDL输出模块。

本教程采用第一种方法,在设计好的Quartus工程文件中嵌入Signal Tap Logic Analyzer进行时序波形的在线调试。

创建.stp文件

.stp文件包括Signal Tap Logic Analyzer设置部分和捕获数据的查看、分析部分。创建一个.stp文件的步骤如下:

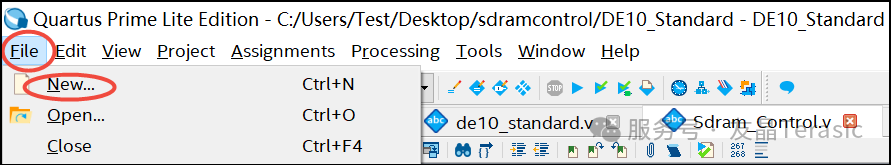

打开Quartus Prime软件,并打开需要嵌入Signal Tap Logic Analyzer的Quartus工程,然后依次点击Quartus工具栏的File-->New,如下图所示2.2所示。

图2.2 选择New对话框

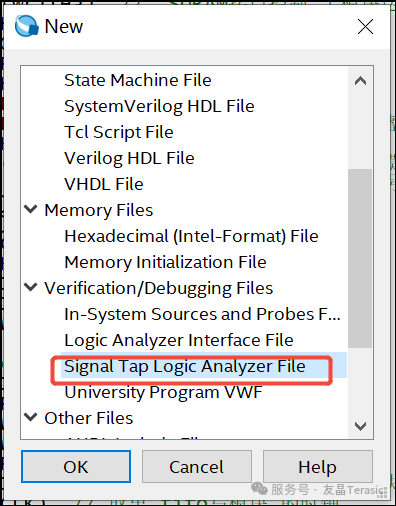

2. 在弹出的New对话框中,选择Verification/Debugging Files中的Signal Tap Logic Analyzer File,如图2.3所示,点击OK确认。

图2.3 选择Signal Tap Logic Analyzer File

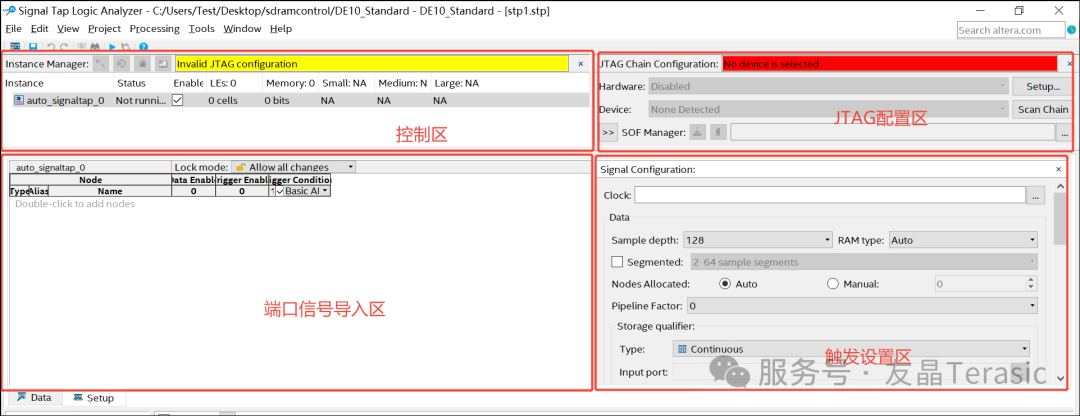

3. 弹出新的Signal Tap Logic Analyzer窗口,如图2.4所示。

图2.4 Signal Tap Logic Analyzer窗口

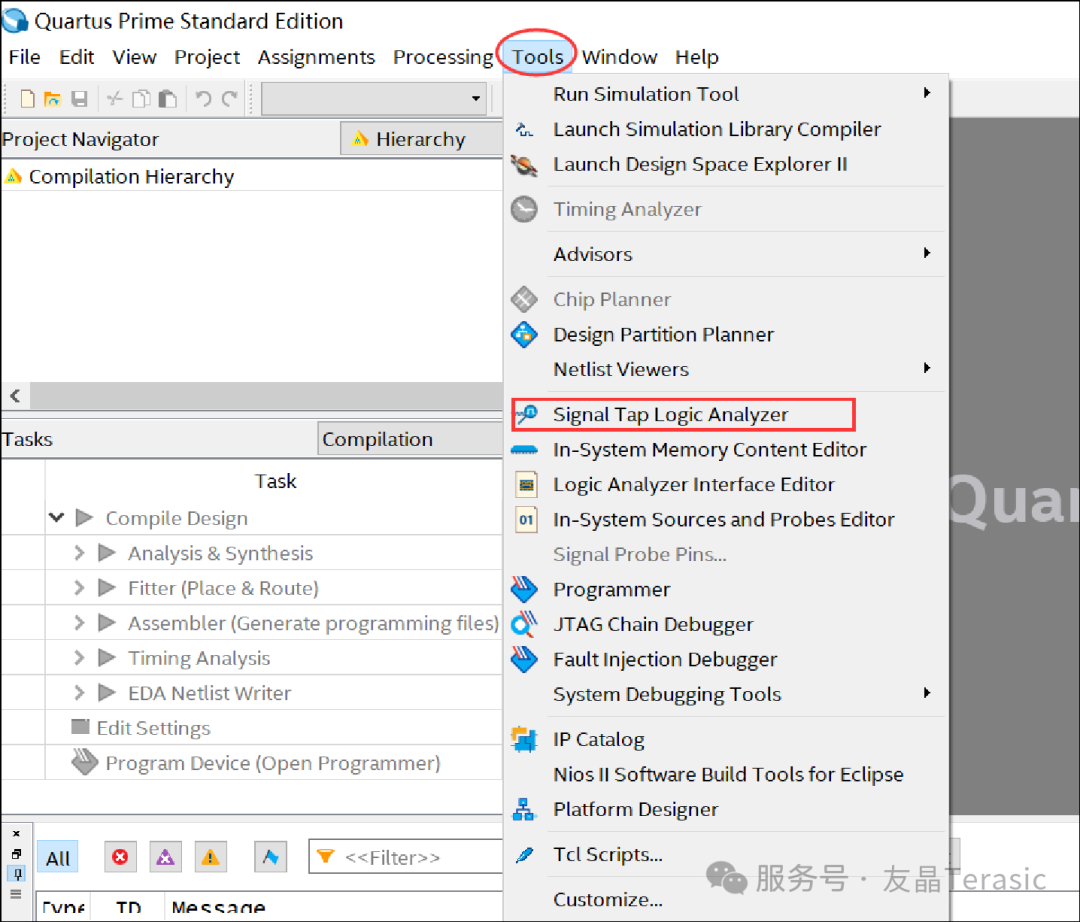

以上操作也可以通过Quartus软件的工具栏Tools-->Signal Tap Logic Analyzer来完成,如下图2.5所示。

图2.5 打开Signal Tap Logic Analyzer

设置.stp文件采集时钟

在使用Signal Tap Logic Analyzer进行FPGA在线调试之前,需要设置.stp文件的采集时钟,采集时钟是在上升沿采集数据。可以使用Quartus工程设计中的任意信号作为采集时钟,最好使用全局时钟,而不要使用门控时钟,并且选择的采样信号和待观测的信号要满足奈奎斯特采样定理。

设置采集时钟的步骤如下:

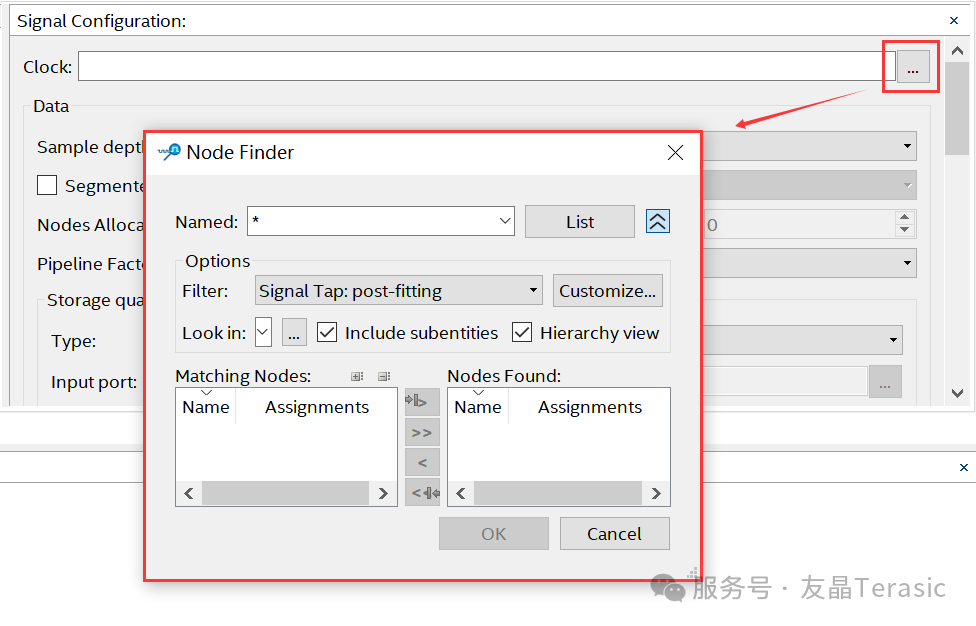

1. 在图2.4所示的Signal Tap Logic Analyzer窗口的触发设置框,点开Clock后面的"..."按钮,打开Node Finder对话框,如图2.6所示。

图2.6 打开Node Finder对话框

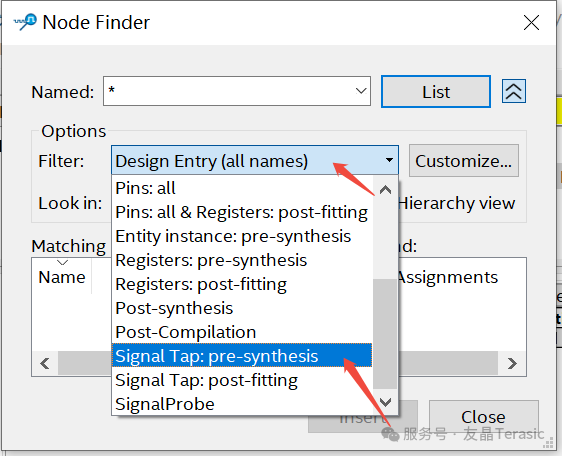

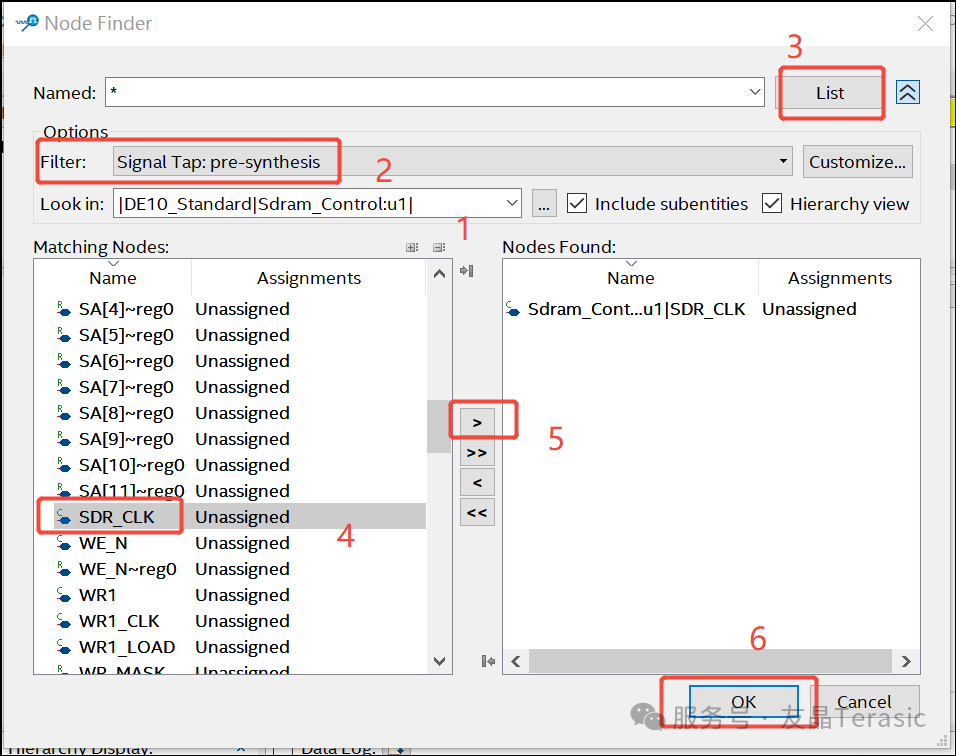

2. 在Node Finder对话框中,在Filter列表中选择 Design Entry(all names)或SignalTap:pre-synthesis,如图2.7所示。

图2.7 选中 Design Entry(all names)

3. 想要看工程里面的哪个文件的信号,就在Look in这里选择对应的文件(或者直接选top文件,所有信号在top文件里面可以找到),然后点击Name行后的List按钮,在Nodes Found列表中选择合适的信号作为Signal Tap Logic Analyzer的采集时钟,如图2.8所示,此处举例选择Sdram_Control.v文件的信号进行查看,选择Sdram_Control.v文件里面的100MHz作为采样时钟。选中后点击">"按钮将时钟信号添加到Nodes Found列表中,也可以直接双击CLK将时钟信号添加到Nodes Found列表。

图2.8 Node Finder对话框设置

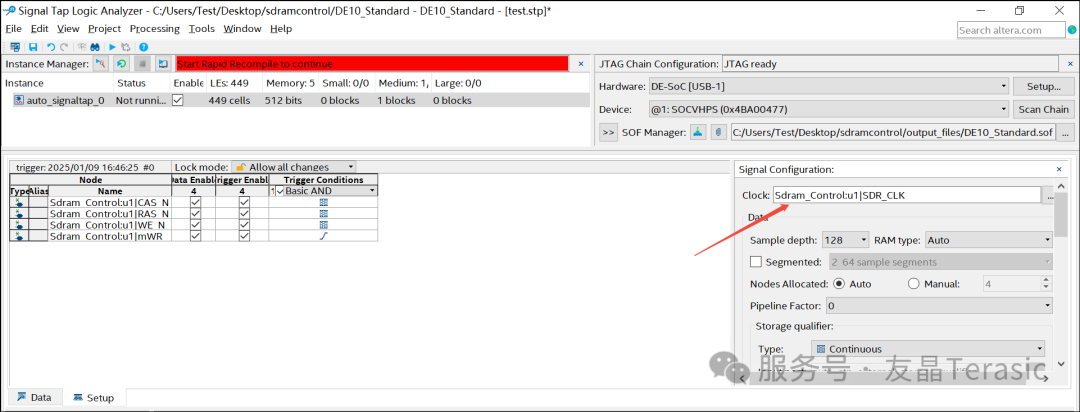

4. 点击OK按钮确定。在Signal Tap Logic Analyzer窗口中可以看到,设置作为采样时钟的信号CLK显示在Clock栏中。如图2.9所示。

图2.9 显示Clock采样时钟信号

注意:如果在Signal Tap Logic Analyzer窗口中没有分配采集时钟,Quartus软件会自动建立一个名为auto_stp_external_clk_0的时钟引脚。在设计中必须为这个引脚单独分配一个器件引脚。在开发板上也必须有一个外部时钟信号驱动该引脚。

在.stp文件中配置信号节点

在.stp文件中,常分配如下两种类型的信号:

Signal Tap: pre-synthesis——该信号在对设计进行Analysis&Elaboration操作以后存在,这些信号表示寄存器传输级(RTL)信号。在Signal Tap Logic Analyzer中要分配Pre-synthesis信号,可以选择Quartus软件工具栏的Processing-->Start Analysis&Elaboration。对设计进行修改后,如果要在物理综合之前快速加入一个新的节点名,使用这项操作特别有用。

Signal Tap: post-fitting——该信号在对设计进行物理综合优化以及布局布线操作后存在。

本教程采用分配Signal Tap: pre-synthesis类型信号为例进行说明。

分配数据信号

依次点击Quartus软件工具栏的Processing-->Start-->Start Analysis&Elaboration,对设计进行Analysis&Elaboration。

图2.10 对设计进行Analysis&Elaboration

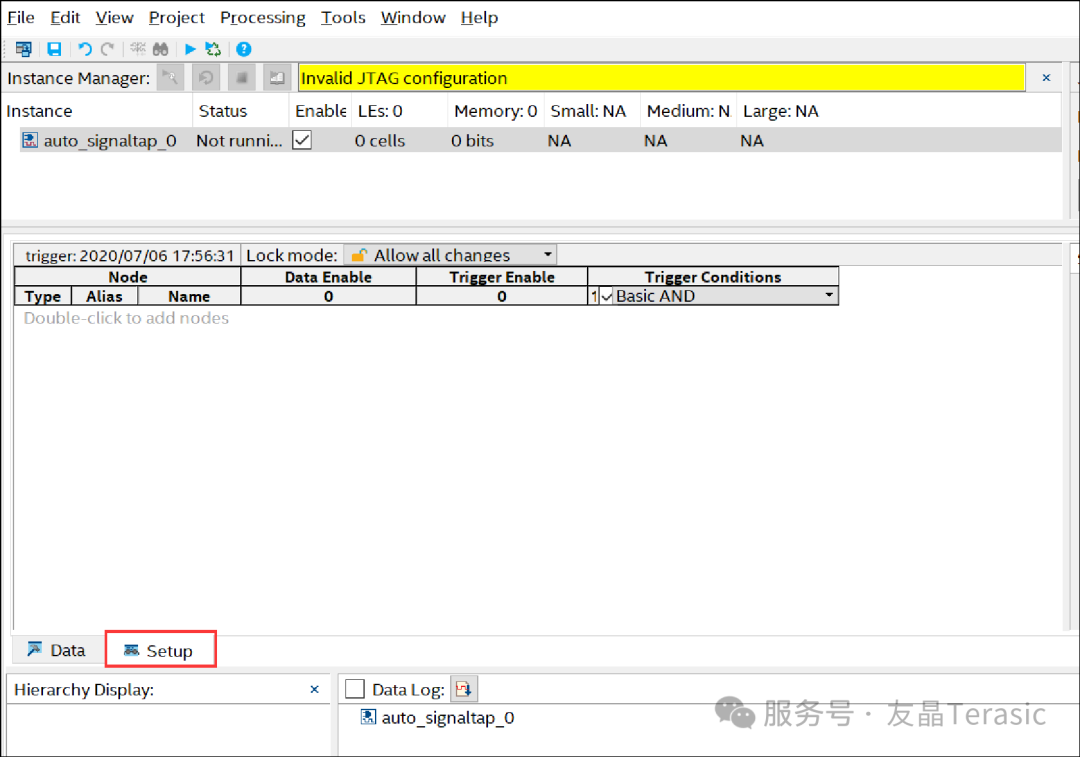

2. 在Signal Tap Logic Analyzer窗口中点击Setup标签页,如下图2.11所示。

图2.11 Setup标签页

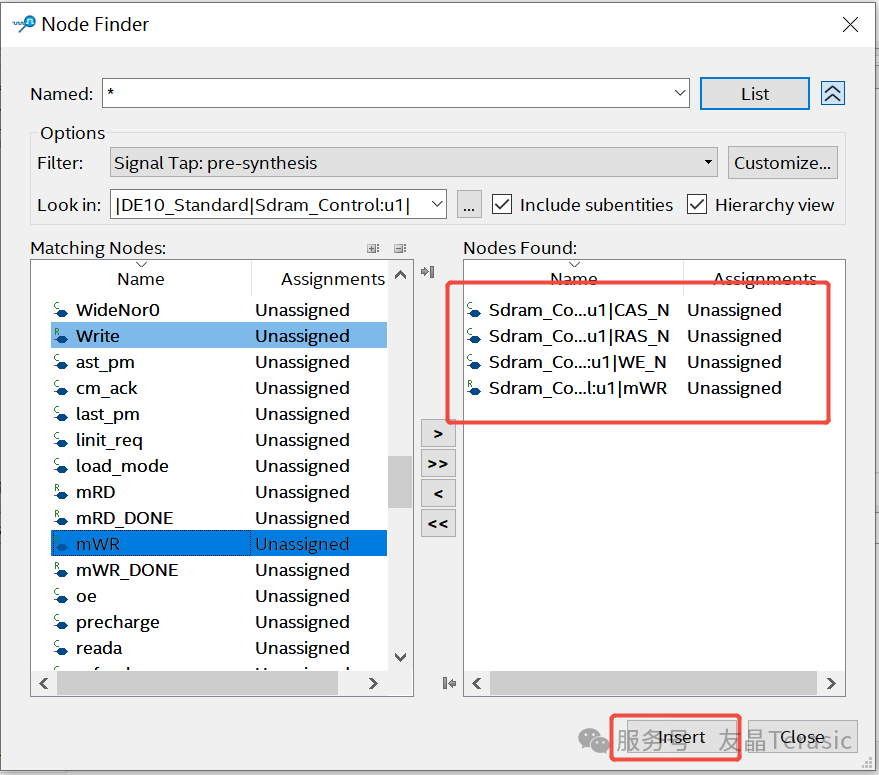

3. 双击Setup标签页的空白处,弹出Node Finder对话框。

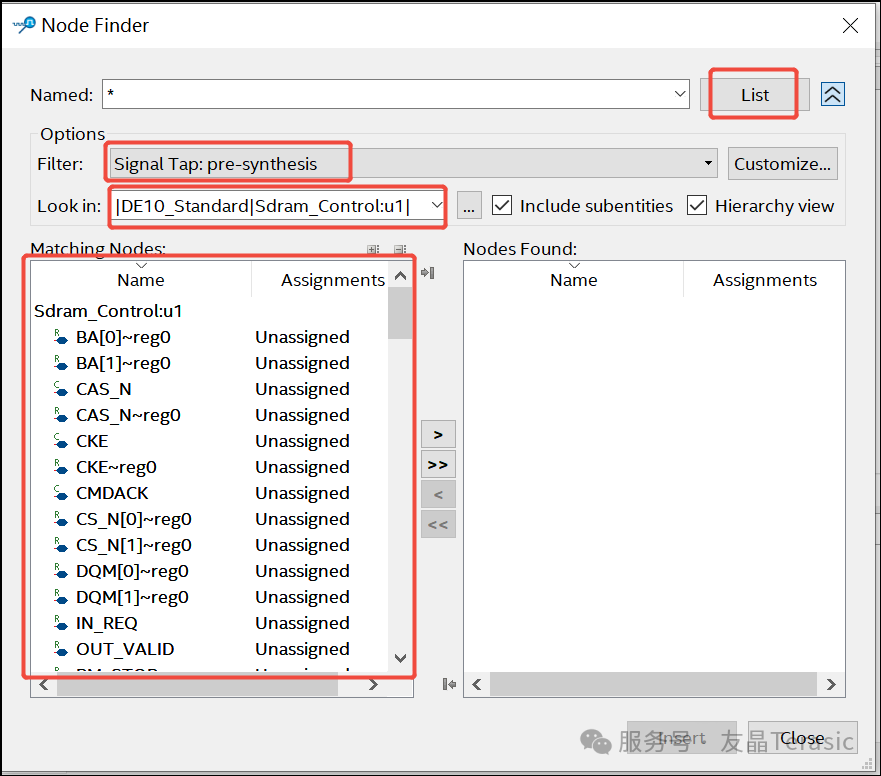

4. 在Node Finder对话框的Filter列表中选择Signal Tap: pre-synthesis。

5. 点击Node Finder对话框Name行后的List按钮查找节点,所有节点都显示在Matching Nodes列表中。

图2.12 Nodes Finder对话框

6. 双击相应的节点或总线将其添加到Nodes Found列表中。

7. 点击Insert按钮,将选择的节点或总线插入到.stp文件。

图2.13 选择节点

Signal Tap Logic Analyzer触发设置

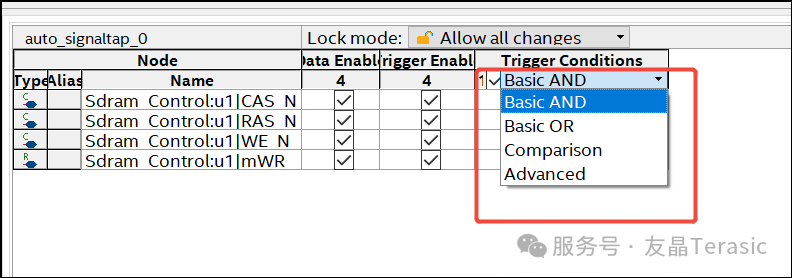

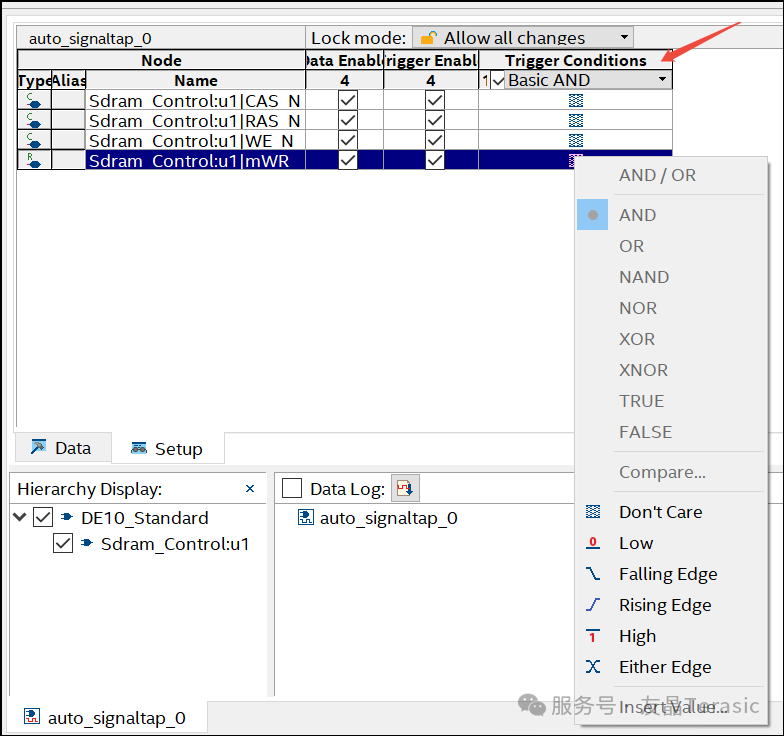

Signal Tap Logic Analyzer触发设置主要是设置观测信号的触发条件(Trigger Conditions)。

触发类型选择Basic AND或Basic OR:如果触发类型选择Basic,在.stp文件中必须为每个信号设置相应的触发模式(Trigger Pattern)。Signal Tap Logic Analyzer中的触发模式包括Don't Care(无关项触发)、Low(低电平触发)、High(高电平触发)、Falling Edge(下降沿触发)、Rising Edge(上升沿触发)和Either Edge(双边沿触发)。如图2.14所示,当设定的触发条件满足时,Signal Tap Logic Analyzer开始捕获数据。

图2.14-1 设置类型

图2.14-2 设置触发模式

触发类型选择Advanced:如果触发类型选择Advanced,则必须为Signal Tap Logic Analyzer建立触发条件表达式。一个Signal Tap Logic Analyzer最关键的特点是它的触发能力。如果不能很好的为数据捕获建立相应的触发条件,它可能无法帮助设计者捕捉到需要观测的有效信号。

在Signal Tap Logic Analyzer中,使用高级触发条件编辑器(Advanced Trigger Condition Editor)可以在简单的图形界面建立非常复杂的触发条件。设计者只需要将运算符拖动到触发条件编辑器窗口中,就可以建立复杂的触发条件,如图2.15所示。

图2.15 高级触发条件编辑器

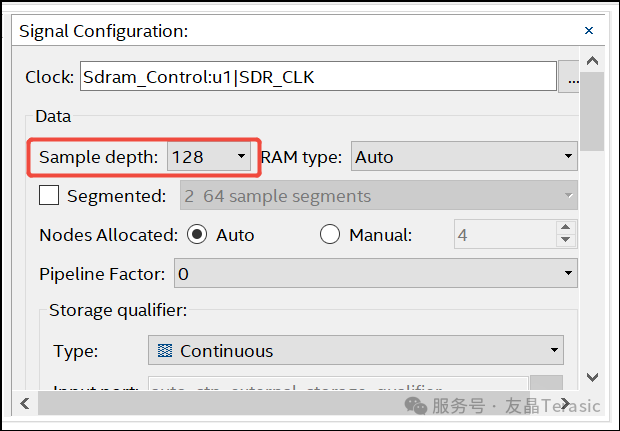

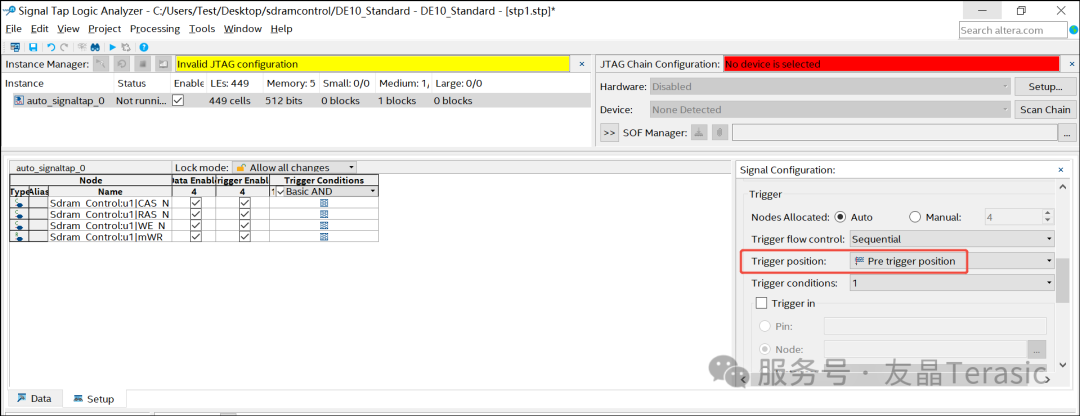

指定采样点数及触发位置

在触发事件开始之前,可以指定要观测数据的采样点数,即数据存储深度,以及触发事件发生前后的采样点数,如图2.16所示。

图2.16-1 设置采样点数及触发位置

图2.16-2 设置采样点数及触发位置

在Signal Tap Logic Analyzer窗口右侧Signal Configuration部分的Data栏中,在Sample depth列表中可以选择需要观测的采样点数;在Trigger栏中,在Trigger Condition列表中可以选择触发信号有效前后的数据比例:

1. Pre trigger position:保存触发信号发生之前信号状态信息(88%的触发前数据,12%的触发后数据)。

2. Center trigger position:保存触发信号发生前后数据,各占50%。

3. Post trigger position:保存触发信号发生之后信号状态信息(12%的触发前数据,88%的触发后数据)。

重新编译嵌入.stp文件的Quartus工程

配置好并保存.stp文件后,在使用Signal Tap Logic Analyzer之前必须编译Quartus工程。如下图2.17所示,点击Signal Tap Logic Analyzer窗口的编译按钮,对工程进行全编译。

图2.17 全编译Quartus工程

使用Signal Tap Logic Analyzer进行编程调试

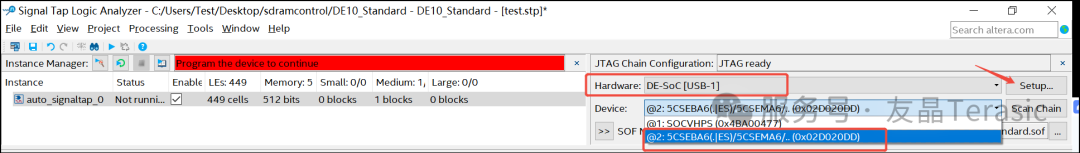

在设计中嵌入.stp文件并完全编译完成后,通过USB Blaster II下载电缆连接好开发板并接通电源。打开.stp文件后,详细调试步骤如下:

1. 在.stp文件右上方的JTAG Chain Configuration部分,在Hardware列表中选择 "DE-SoC[USB-1]",一般情况下Signal Tap Logic Analyzer可以自动扫描到开发板上的FPGA器件并显示在Device列表中。如下图2.18所示。

图2.18 JTAG Chain设置

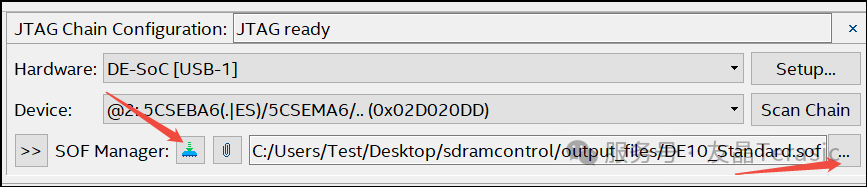

2. 点击SOF Manager右侧的"..."按钮,选择.sof文件,然后点击下载按钮对FPGA进行配置,如下图2.19所示。

图2.19 配置FPGA

查看Signal Tap Logic Analyzer调试波形

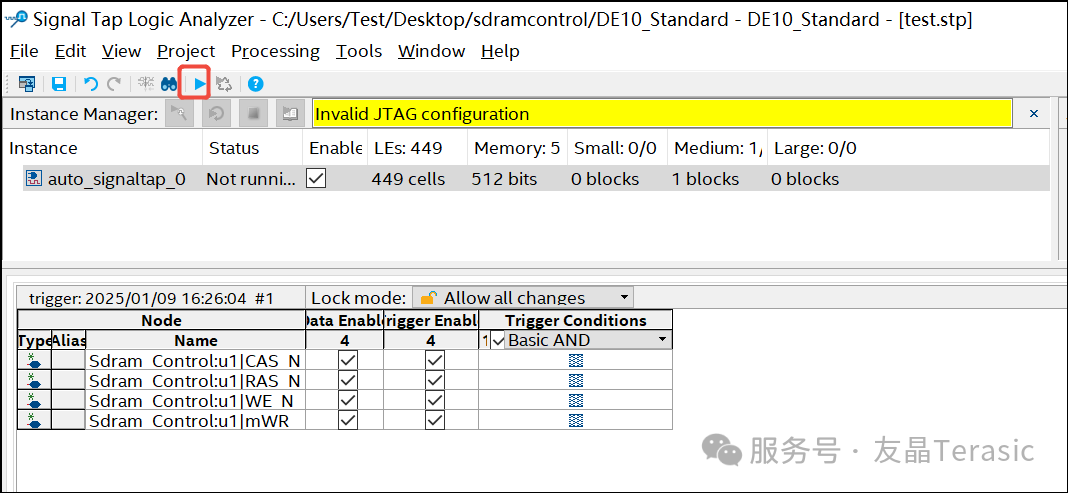

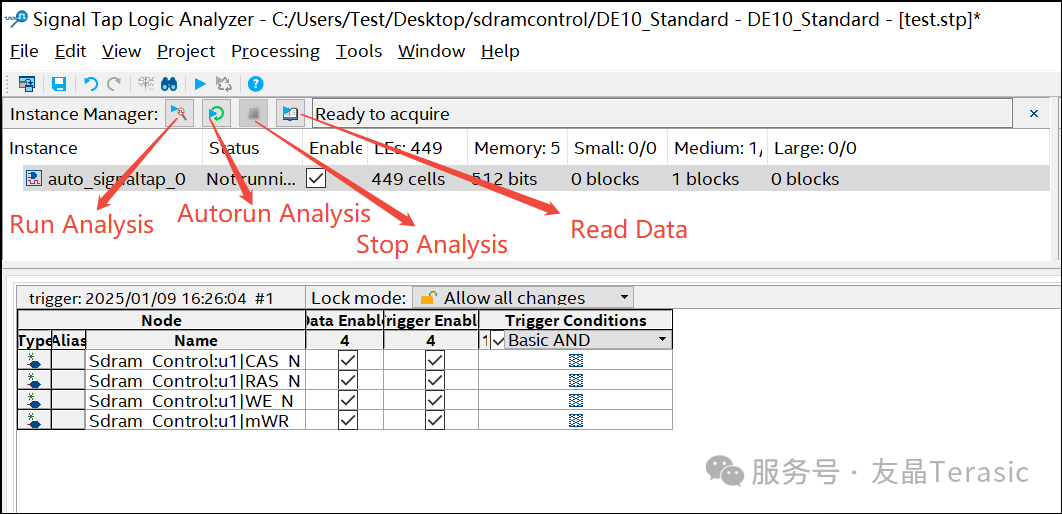

Signal Tap Logic Analyzer工具条上有四个执行逻辑分析的选项,如下图所示。

图2.20-1

1. Run Analysis:单步执行捕获数据进行逻辑分析,即执行该命令后,Signal Tap Logic Analyzer等待触发事件,当触发事件发生时开始采集数据,然后停止。

2. Autorun Analysis:执行该命令后,Signal Tap Logic Analyzer根据所设置的触发条件连续采集数据,直到用户按下Stop Analysis按钮为止。

3. Stop Analysis:停止Signal Tap Logic Analyzer。如果触发事件还没有发生,则没有接收数据显示。

4. Read Data:显示捕获的数据。如果触发事件还没有发生,用户可以点击该按钮查看当前采集的数据。

选择Run Analysis或AutoRun Analysis按钮,当触发条件满足时,Signal Tap Logic Analyzer开始捕获数据。

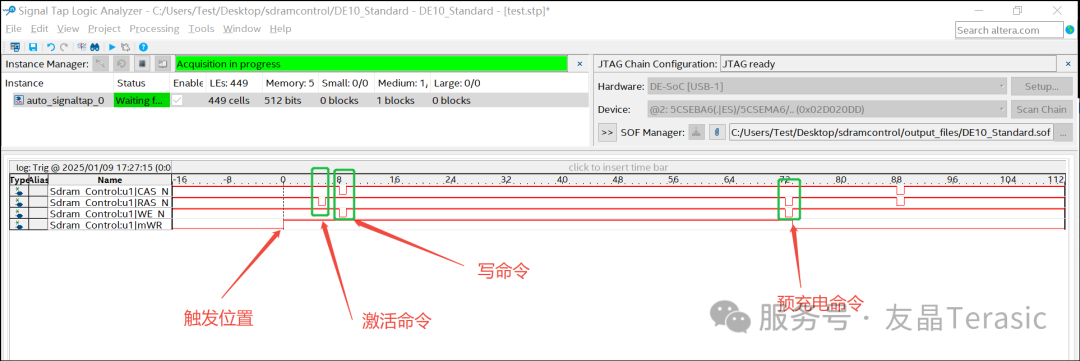

图2.20-2

Signal Tap Logic Analyzer会自动将采集的数据显示在Data标签页中,如图2.20-2所示。

从波形图可以看到,写SDRAM之前先发送了一个行激活命令,然后是写命令,连续写64个数据以后系统发送了一个预充电命令结束页突发操作。

-

SDRAM控制器的设计——Sdram_Control.v代码解析(异步FIFO读写模块、读写SDRAM过程)2025-03-04 2642

-

PIC32系列参考手册之DDR SDRAM控制器2023-09-25 558

-

FPGA之SDRAM控制器设计(二)精选资料分享2021-07-30 898

-

基于SDRAM控制器软核的Verilog设计2021-06-30 3671

-

DDR SDRAM控制器的设计与实现2021-03-28 1222

-

如何使用FPGA设计SDRAM控制器2020-12-18 1043

-

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文2018-12-25 1737

-

SDRAM控制器的设计2017-11-28 1495

-

EPM1240的SDRAM控制器的设计2017-10-31 905

-

基于VHDL的SDRAM控制器的实现2017-01-22 1080

-

DDR SDRAM控制器参考设计VHDL代码2016-06-07 1139

-

SDRAM控制器简易化设计2011-10-24 1197

-

基于FPGA的高速SDRAM控制器的视频应用2009-11-04 1106

-

使用Verilog实现基于FPGA的SDRAM控制器2009-06-20 2505

全部0条评论

快来发表一下你的评论吧 !