TPS53676 带 AVSBus 的双通道 D-CAP+、双通道 (N+M<= 7 相) 降压、多相控制器数据手册

描述

TPS53676 是一款具有双通道、内置非易失性存储器 (NVM) 和 PMBus™ 兼容串行接口的降压控制器,并且与 TI NexFET™ 智能功率级完全兼容。D-CAP+ ™ 架构等高级控制功能可提供快速瞬态响应、低输出电容和良好的均流。该器件还提供新颖的相位交错策略和灵活的触发序列,以提高热性能。还支持输出电压转换速率和电压定位的可调控制。此外,该器件还支持 PMBus 通信接口,用于向系统主机报告电压、电流、功率、温度和故障条件的遥测数据。所有可编程参数都可以通过串行接口进行配置,并且可以作为新的默认值存储在 NVM 中,以最大限度地减少外部元件数量。

TPS53676 器件采用热增强型 48 引脚 QFN 封装,额定工作温度范围为 –40°C 至 125°C。

*附件:TPS53676 双通道 D-CAP+™、(N+M ≤ 7 相)降压、多相控制器,带 AVSBus 和 PMBus 接口 数据表.pdf

特性

- 输入电压范围:4.5 V 至 17 V

- 输出电压范围:0.25 V 至 5.5 V

- 每相开关频率范围:300 kHz 至 2000 kHz

- 双输出支持 N+M 相位配置(N+M ≤ 7、M ≤ 3)

- 符合 AVSBus 标准,符合 PMBus 1.3.1 第 III 部分

- PMBus v1.3.1 系统接口,用于配置、控制和遥测电压、电流、功率、温度和故障状态

- 通过 VOUT_COMMAND 实现自适应电压调节 (AVS)

- 增强的 D-CAP+ 控制,提供超瞬态性能和出色的动态均流

- 可编程环路补偿

- 灵活的相位触发顺序

- 用于 Ch. 的外部针带A 启动电压设置

- 单独的相电流校准和报告

- 相热平衡管理 (TBM)

- 完全支持动态切相 (DPS)

- 用于下冲减少 (USR) 的快速相位添加

- 用于减少过冲 (OSR) 的体二极管制动

- 无驱动器配置,实现高效的高频开关

- 与 TI NexFET™ 功率级完全兼容,适用于高密度解决方案

- 精确、可编程的自适应电压定位 (AVP)

- 获得专利的 AutoBalance™ 相位平衡

- 6 mm × 6 mm、48 引脚 QFN 封装

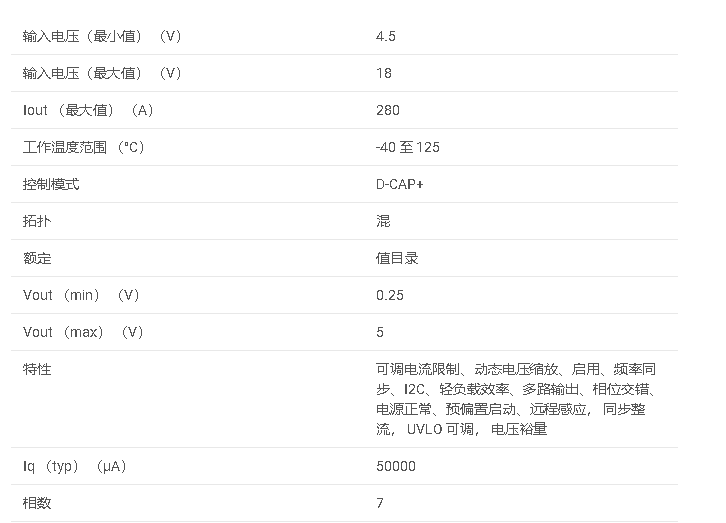

参数

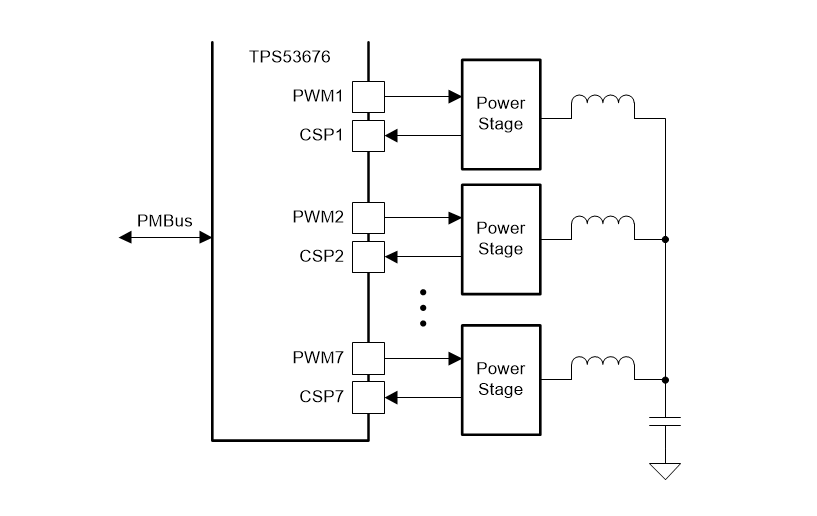

方框图

1. 产品概述

- 型号:TPS53676

- 类型:双通道D-CAP+™降压、多相控制器

- 特点:支持N+M ≤ 7相,集成非易失性存储器(NVM),带AVSBus和PMBus接口,兼容TI NexFET™智能功率级。

2. 关键特性

- 高效控制:采用D-CAP+™控制技术,实现快速瞬态响应。

- 可编程性:通过PMBus接口可编程,支持多种工作模式,如快速相位添加(DPS)和过冲减少(OSR)。

- 高密度解决方案:与TI NexFET™智能功率级完全兼容,支持高密度电源设计。

- 灵活性:支持多相操作,可配置为1至7相,适用于各种负载需求。

- 监控与保护:提供全面的故障保护和系统监控功能,确保系统稳定运行。

3. 功能描述

- D-CAP+™控制:采用峰值电流模式控制,结合D-CAP+™技术,实现优异的瞬态响应和稳定性。

- 自适应电压定位(AVP) :通过编程实现准确的自适应电压定位,提高系统效率。

- 动态VID(DVID) :支持动态电压调节,根据系统负载实时调整输出电压。

- 非线性控制:包括动态集成、过冲减少(OSR)和欠冲减少(USR)功能,优化瞬态性能。

- 故障保护:提供过压、过流、过温等多种故障保护功能,确保系统安全。

4. 应用领域

- 数据中心网络交换机

- 校园和分支交换机

- 核心和边缘路由器

- 硬件加速器卡

- 高性能CPU/ASIC/FPGA电源

5. 设计资源与支持

- WEBENCH® Designer:支持快速设计和优化电源系统。

- PMBus兼容性:通过PMBus接口实现远程监控和控制,提高系统灵活性。

- 详细文档:提供全面的数据表、应用笔记、用户指南等技术文档,支持用户快速上手。

6. 封装与尺寸

- 封装类型:48引脚QFN封装(6mm × 6mm)

- 热性能:增强的热设计,确保高功率密度应用下的可靠性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TPS53685双通道多相控制器技术解析与应用指南2025-09-03 1006

-

TPS59641 双通道 SVID,D-CAP+;用于 IMVP-7 Vcore 的降压工业级控制器数据手册2025-03-27 899

-

TPS53679 双通道 6+1/5+2 VR13 D-CAP+ ™ 降压多相控制器数据手册2025-03-24 1142

-

TPS53688 带 VR13 的双通道、8 相降压、数字多相 D-CAP+ ™ 控制器数据手册2025-03-21 1044

-

TPS536C7 双通道 D-CAP+™、PMBus(N+M ≤ 12 相)降压、多相 PWM 控制器数据手册2025-03-20 1007

-

TPS53689T 双通道、8 相降压数字多相 D-CAP+ ™ 控制器数据手册2025-03-19 1177

-

双通道DCAP+多相控制器:TPS536C7B1,TPS536762024-11-22 467

-

双通道(6相+1相)或(5相+2相)D-CAP+™降压多相控制器TPS53679 数据表2024-04-25 475

-

双通道(4相+1相)或(3相+2相)D-CAP+™降压多相控制器TPS53659数据表2024-04-11 447

-

具有PMBus和VR14 SVID接口的双channel(N + M ≤ 8 相)D-CAP+™、 降压多相控制器TPS53689数据表2024-04-10 418

-

具有AVSBus™和PMBus™接口的双通道D-CAP+™降压多相控制器TPS53676数据表2024-03-21 526

全部0条评论

快来发表一下你的评论吧 !