TPS51622A 用于 VR12.6 vCPU 的 2 相 D-CAP+ ™ 降压控制器数据手册

描述

TPS51622A 是一款无人驾驶、完全符合 SVID 标准的 VR12.6 降压控制器。 具有重叠脉冲的 D-CAP+ 架构等高级控制功能支持下冲 减少 (USR) 和过冲减少 (OSR) 提供快速瞬态响应和最低输出 电容和高效率。该 TPS51622A 还支持 CCM 或 DCM 中的单相作 实现轻负载效率。TPS51622A集成了完整的 VR12.6 I/O 功能 包括 VR_READY (PGOOD)、ALERT 和 VR_HOT。这 SVID 接口地址允许从 0 到 7 进行编程。在 PS4 中,静态功耗 控制器的典型值为 0.25 mW。VCPU 转换速率和电压定位轮次的可调控制 推出 VR12.6 功能。与新型 TPS51604 FET 栅极驱动器配合使用,该解决方案可提供 极高的速度和低开关损耗。该TPS51622A与选定的 TI 功率级™配合使用 产品以及 DrMOS 产品。

TPS51622A 封装是一种节省空间的热增强型 32 引脚 QFN,可运行 从 –40°C 至 105°C。

*附件:用于 VR12.6 Vcpu 的 2 相 D-CAP+ ™ 降压控制器 数据表.pdf

特性

- 符合 Intel 串行 VID (SVID) 标准^©^

- 1 相或 2 相作

- 完整的 VR12.6 移动功能集,包括数字电流

监视器、PS3 和 PS4作 - 输出范围为 0.50V 至 2.30V 的 8 位 DAC

- 优化轻负载和重负载下的效率

- 8 个独立的过冲减少 (OSR) 和下冲减少 (USR)

级别 - 用于高效高频

开关的无驱动器配置 - 支持分立器件、Power Block、PowerStage 或

DrMOS MOSFET 实现 - 精确、可调的电压定位

- 300kHz 至 1MHz 频率选择

- 获得专利的 AutoBalance 相位平衡

- 可选 8 级电流限制

- 4.5V 至 28V 转换电压范围

- 小型 4 × 4 引脚 32 引脚 QFN PowerPad 封装

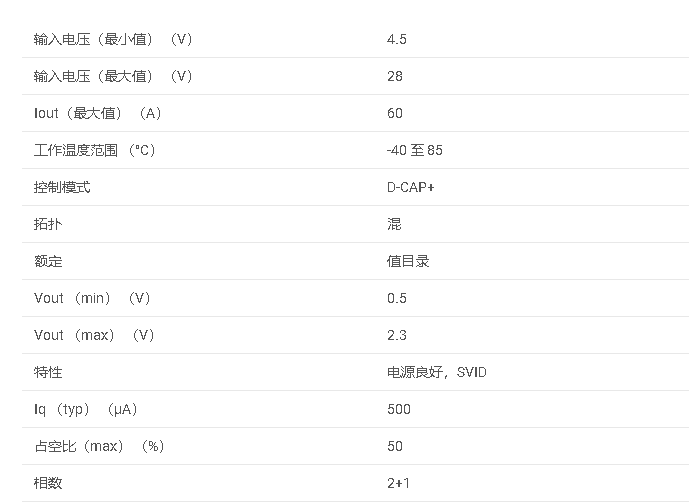

参数

一、产品概述

该设备专为在严格保密协议下与Intel Corporation合作的IMVP(Intel Mobile Voltage Positioning)移动处理器供电而设计。终端用户必须与Intel Corporation签订有效的保密协议(CNDA)才能使用。

二、联系方式

如需详细的数据表和其他设计支持工具,请联系IMVP团队:IMVP@list.ti.com。

三、封装选项

- 封装类型:提供多种封装选项,如VQFN RSM等。

- 封装状态:包括ACTIVE(推荐用于新设计)、PREVIEW(已宣布但未生产,可能有样品)、NRND(不推荐用于新设计,但仍在生产以支持现有客户)等状态。

- 环保计划:产品符合RoHS要求,部分产品还标记为Green(无溴、无锑)。

- 引脚数量与封装数量:不同封装选项的引脚数量和封装数量有所不同。

- 湿度敏感性等级(MSL)与峰值温度:根据JEDEC行业标准分类。

四、标记信息

设备标记可能包括设备型号、批次追踪代码信息或环境类别等。多个设备标记将包含在括号内,且设备上只会显示其中一个标记。

五、免责声明

提供的信息代表TI在提供日期时的知识和信念。TI基于第三方提供的信息,不对信息的准确性做任何陈述或保证。TI已采取并将继续采取合理步骤提供代表性和准确的信息,但可能对进入的材料和化学品未进行破坏性测试或化学分析。

六、包装材料信息

- 带和卷盘信息:提供卷盘的尺寸、腔体中心间距等详细信息。

- 卷盘盒尺寸:提供不同封装选项的卷盘盒宽度、长度和高度信息。

七、封装视图与尺寸

- 通用封装视图:展示了封装家族的表示,实际封装可能有所不同。

- 封装轮廓与尺寸:提供详细的封装尺寸图,包括引脚间距、封装高度等。

- 板布局示例:提供焊盘布局示例,包括焊盘尺寸、间距和推荐布局等。

- 模板设计示例:提供焊膏模板设计示例,包括开口尺寸、形状和焊膏覆盖率等。

-

TPS51631A 用于 VR12.5 vCPU 的 3 相 D-CAP+ ™ 降压控制器数据手册2025-03-26 938

-

TPS51633 用于 VR12.6/VR12.6+ VCPU 的 3 相 D-CAP+ ™ 降压控制器数据手册2025-03-25 909

-

适用于VR13 CPU VCORE 和 DDR内存的两相 D-CAP+™ 降压控制器TPS53627数据表2024-04-25 427

-

双通道(4相+1相)或(3相+2相)D-CAP+™降压多相控制器TPS53659数据表2024-04-11 447

-

适用于VR12.6 VCPU的两相D-CAP+降压控制器TPS51624数据表2024-04-10 403

-

VR12.6 Vcpu的两相D-CAP+™降压控制器数据表2024-04-07 389

-

适用于VR12.6 VCPU 的三相 D-CAP+™ 降压控制器TPS51633 数据表2024-03-27 365

-

适用于VR12.1 VCPU 的两相 D-CAP+™降压控制器TPS51623数据表2024-03-26 412

-

TPS51622A 用于 VR12.6 Vcpu 的 2 相 D-CAP+ 降压控制器2018-10-16 559

全部0条评论

快来发表一下你的评论吧 !