ADMV7310系统级封装 (SiP) 同相/正交 (I/Q) 升频器技术手册

描述

概述

ADMV7310 是一款完全集成的系统级封装 (SiP) 同相/正交 (I/Q) 升频器,可在直流至 2 GHz 的中频 (IF) 输入范围和 71 GHz 至 76 GHz 的射频 (RF) 输出范围之间工作。该套件使用由 6× 本地振荡器 (LO) 倍频器驱动的镜像抑制混频器。混频器输出后接可变增益放大器 (VGA) 和功率放大器 (PA),提供 35 dB(典型值)的转换增益。提供差分 I 和 Q 混频器输入,并可通过适用于直接转换应用的差分 I 和 Q 基带波形进行驱动。或者,可以针对单端应用使用一个外部 90° 混合和两个外部 180° 混合来驱动输入。

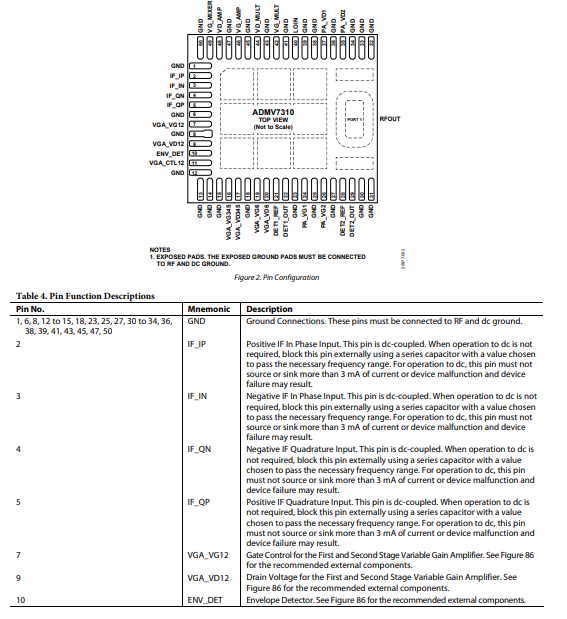

ADMV7310 采用完全集成的表面安装 50 端子 16.00 mm × 14.00 mm 芯片阵列小外形无铅腔面 (LGA_CAV) 封装。ADMV7310 的工作温度范围为 −40°C 至 +85°C。

数据表:*附件:ADMV7310系统级封装 (SiP) 同相 正交 (I Q) 升频器技术手册.pdf

应用

- E 频段通信系统

- 高容量无线回程

- 测试与测量

- 航空航天和防务

特性

- 最大转换增益:35 dB(典型值)

- 增益调节范围:40 dB(最小值)

- P

SAT:增益 = 23.5 dB 和 19.5 dB 时为 26 dBm(典型值) - OIP3:增益 = 23.5 dB 且每个信号音的 P

OUT= 16.5 dBm 时为 31 dBm(典型值) - OP1dB:增益 = 23.5 dB 和 19.5 dB 时为 25 dBm(典型值)

- 内置功率检波器

- 用于 LO 调零的内置包络检波器

- 完全集成的表面安装 50 端子 16.00 mm × 14.00 mm LGA_CAV 封装

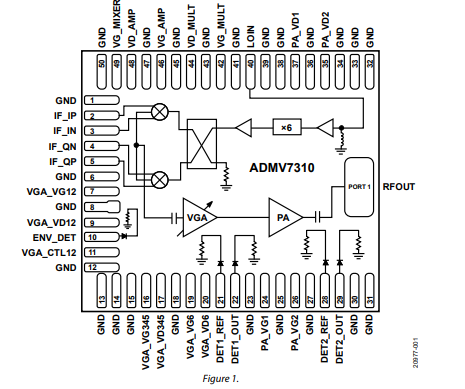

框图

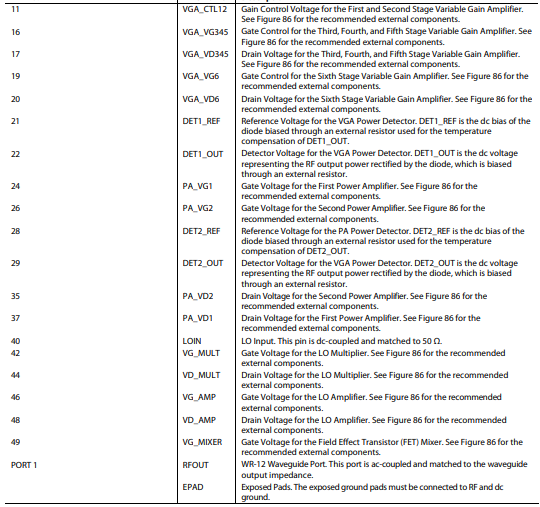

引脚配置描述

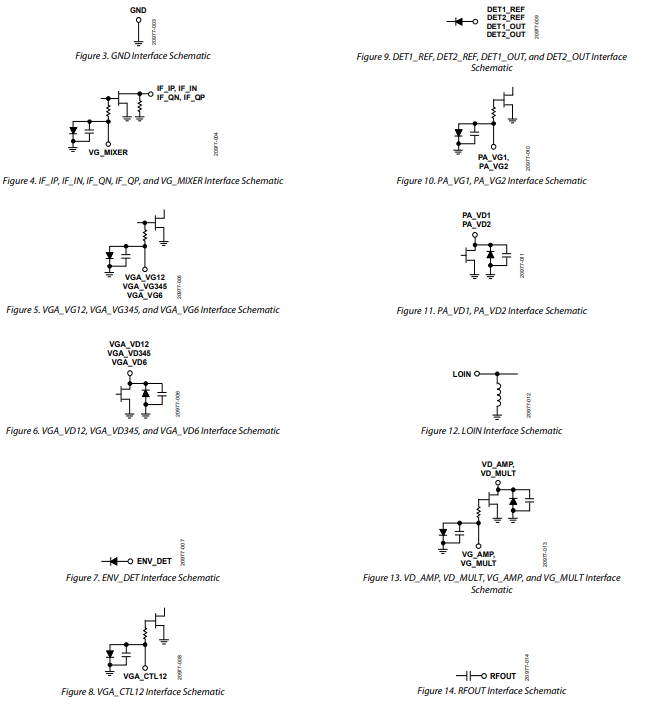

接口示意图

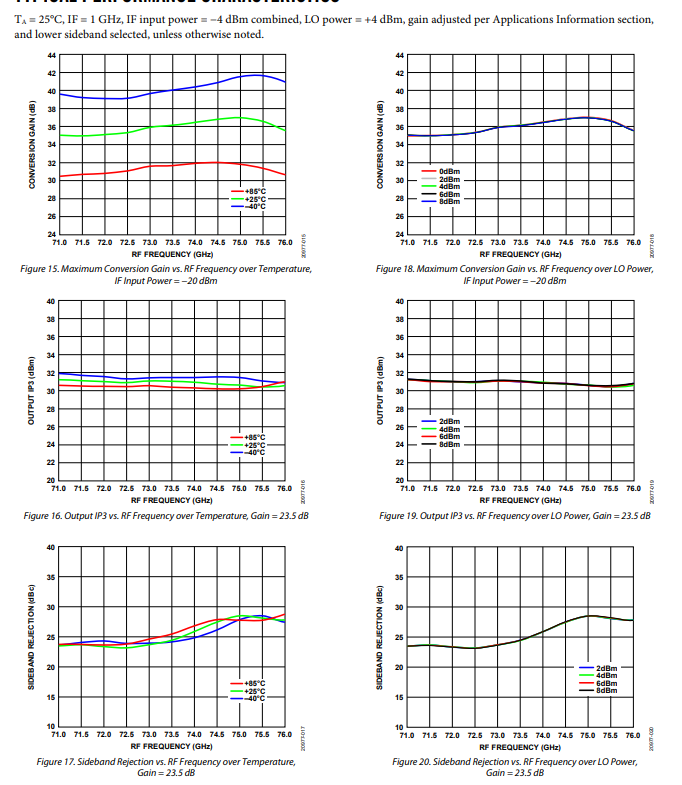

典型性能特征

工作原理

ADMV7310是一款完全集成的系统级封装(SiP)的同相/正交(I/Q)上变频器,由三个功能模块组成:混频器和本振(LO)路径、包络检波器、可变增益放大器(VGA),以及功率检波器和功率放大器。

混频器和本振路径

第一个功能模块是一个砷化镓(GaAs)I/Q上变频器,由一个6倍频乘法器驱动。6倍频乘法器允许使用较低频率范围的LO输入信号,频率范围在11.8 GHz至12.7 GHz之间。该6倍频乘法器通过级联的3倍频和2倍频乘法器实现。LO缓冲放大器用于提供典型4 dBm的LO路径驱动电平。典型的LO路径包括一个片内带通滤波器,随后是片内平衡器,用于驱动I和Q混频器核心。混频器核心由平衡的混频器对组成。

I和Q混频器的射频输出随后通过片内威尔金森功率合成器求和,然后输入到第二个功能模块。

包络检波器、可变增益放大器和功率检波器

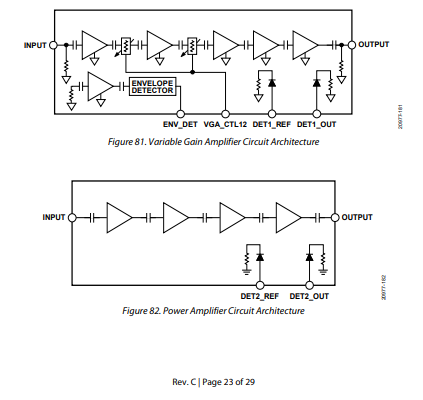

第二个功能模块是一个可变增益放大器(见图81)。该可变增益放大器利用多个增益级和一个级联的可变衰减级,形成一个低噪声、高线性度的可变增益放大器。第一级是可变增益放大器的低噪声前置放大器。信号的一部分在驱动片内包络检波器之前被耦合,该包络检波器提供与峰值输入功率成比例的输出。

前置放大器之后是信号路径中的第一个电压可变衰减器。然后,第二级放大器在驱动第二个可变衰减器之前提供额外的增益和隔离。在第二个可变衰减器之后是三个级联的增益级。

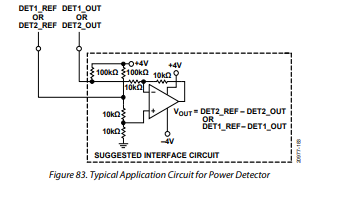

在第二级的输出端,另一个耦合器取出一小部分输出信号。耦合后的信号被送到片外二极管检波器,用于外部监测输出功率。匹配参考二极管2(DET2)用于帮助校正检波器的温度相关性。功率检波器的典型应用电路如图83所示。有关不同偏置条件下可变增益放大器如何馈入ADMV7310的第三个功能模块的更多详细信息,请参见“应用信息”部分。

功率放大器和功率检波器

第三个功能模块是一个功率放大器,它由四个级联的增益级组成一个放大器链(见图82)。在输出级的起始处,一个耦合器取出一小部分输出信号。耦合后的信号被送到片外二极管检波器,用于外部监测输出功率。匹配参考二极管1(DET1)用于帮助校正检波器的温度相关性。

功率检波器的典型应用电路如图83所示。

-

Analog Devices Inc. ADMV1555宽带I/Q混频器数据手册2025-05-26 940

-

HMC6505A 5.5GHz到8.6GHz,GaAs,MMIC,I/Q升频器技术手册2025-03-27 845

-

ADMV7320 E频段升频器 SiP,81GHz至86GHz技术手册2025-03-26 919

-

ADMV1013 24GHz至44GHz、宽带微波上变频器技术手册2025-02-28 809

-

系统级封装(SiP)技术介绍2024-11-26 3012

-

SiP系统级封装设计仿真技术2022-08-29 1147

-

EVAL-ADMV7310 EVAL-ADMV7310评估板2021-07-10 266

-

UG-1590:ADMV7310-EVALZ用户指南2021-05-24 693

-

ADMV7310:E波段更新SIP,71 GHz到76 GHz数据Sheet2021-04-18 729

-

Analog Devices ADMV4530 Ka频段上变频器在贸泽开售2020-06-15 1798

-

ADMV1013ACCZ微波升频器产品介绍2019-07-09 1392

-

ADI ADMV1013 24-44GHz宽带微波升频器解决方案2019-05-04 3038

-

SiP(系统级封装)技术的应用与发展趋势2018-08-23 4904

全部0条评论

快来发表一下你的评论吧 !