TPS51604 4A、28V 半桥栅极驱动器,适用于同步降压高频 CPU 内核电源应用技术资料

描述

TPS51604 驱动程序针对高频 CPU 进行了优化 V核心应用。先进的功能,如减少的死区时间驱动和 自动过零用于优化整个负载范围内的效率。

SKIP 引脚提供 CCM作选项以支持 输出电压的受控管理。此外,TPS51604 还支持 两种低功耗模式。当 PWM 输入处于三态时,静态电流降低到 130 μA,其中 立即响应。当 SKIP 保持在三态时,电流减小 降至 8 μA(通常需要 20 μs 才能恢复开关)。与适当的 TI 配对 控制器,驱动器提供超高性能的电源系统。

*附件:用于高频 CPU 内核电源的 TPS51604 同步降压 FET 驱动器 数据表 .pdf

TPS51604 器件采用节省空间、热增强型封装 8 引脚、2mm × 2mm WSON 封装,工作温度范围为 –40°C 至 105°C。

特性

- 降低死区时间驱动电路,优化

CCM - 自动过零检测,优化

DCM 效率 - 多种低功耗模式,优化轻

负载效率 - 针对高频

作优化的信号路径延迟 - 集成 BST 开关驱动强度,针对超极本 FET 进行了优化

- 针对 5V FET 驱动进行了优化

- 转换输入电压范围 (V

在):4.5 至 28 V - 2mm × 2mm、8 引脚 WSON 导热垫

封装

参数

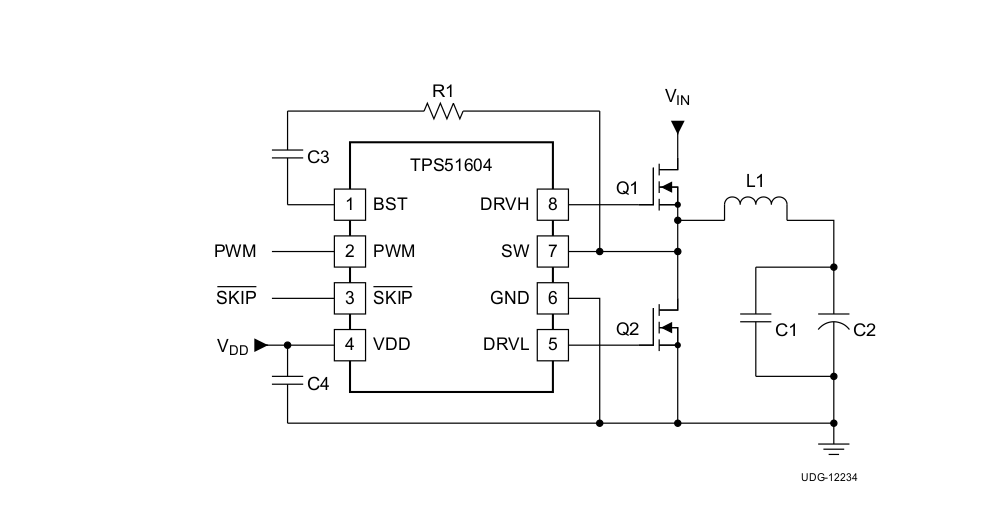

方框图

一、产品概述

- 产品名称:TPS51604

- 制造商:Texas Instruments

- 类型:同步降压FET驱动器

- 应用领域:高频CPU内核电源,适用于平板电脑、适配器、电池供电的NVDC铁路等

二、主要特性

- 优化性能:针对高频CPU VCORE应用优化,提供先进的CCM(连续导通模式)特性,如减少死区时间的驱动电路和自动零交叉检测,以提高整个负载范围的效率。

- 低功耗模式:提供多个低功耗模式,通过SKIP引脚实现CCM操作的受控管理,支持输出电压的精细控制。

- 快速响应:集成的BST开关和优化的FET驱动强度,确保对Ultrabook FETs的快速响应。

- 宽输入电压范围:转换输入电压范围从4.5V到28V。

- 小尺寸封装:采用2mm x 2mm的8引脚WSON热垫封装,节省空间并具有增强的热性能。

三、电气特性

- UVLO(欠压锁定)保护:VDD的UVLO阈值为4.15V(上升)和3.7V(下降),具有0.2V的迟滞。

- 供电电流:在PWM输入为高电平时,供电电流为600µA;在PWM输入为低电平时,供电电流为250µA;在PWM输入为浮空状态时,供电电流为130µA;在SKIP引脚为浮空状态时,供电电流典型值为8µA。

- PWM和SKIP引脚规格:包括输入阻抗、高低电平电压、迟滞电压和三态电压等。

- 栅极驱动器特性:提供高侧和低侧栅极驱动器的上升/下降时间、传播延迟、源/漏电阻等详细规格。

四、功能描述

- UVLO保护:监控VDD电压水平,确保在电压达到安全范围之前,驱动器保持禁用状态。

- PWM引脚功能:支持三态输入,当PWM引脚处于三态时,驱动器进入低功耗状态。

- SKIP引脚功能:控制零交叉检测比较器的启用/禁用,从而控制转换器在CCM和DCM模式之间的切换。当SKIP引脚处于三态时,驱动器进入极低功耗状态。

- 自适应死区时间控制:减少低侧体二极管导通时间,提高效率,并避免高侧和低侧MOSFET的同时导通。

- 集成BST开关:维持BST-SW电压接近VDD,降低高侧FET的导通损耗。

五、应用与实现

- 典型应用:提供了与TPS51632控制器和CSD87381功率块配合使用的两相设计示例。

- 设计步骤:包括选择输入电容、启动电容和电阻、建立TPS51604与控制器和功率块之间的连接等。

- 布局指南:建议将驱动器尽可能靠近MOSFET放置,使用宽迹线连接DRVH和DRVL引脚,以及避免PWM和使能迹线靠近高dV/dT电压区域。

六、封装与供货信息

- 封装类型:WSON(DSG)封装,包含8个引脚和热垫。

- 供货状态:活跃生产

七、其他信息

- 开发支持:提供Power Stage Designer工具链接,帮助用户进行设计。

- 相关文档:提供了与其他TI产品的相关文档链接,如TPS51632控制器和CSD87330功率块的数据表。

- 社区资源:提供了TI E2E在线社区和设计支持的链接,方便用户获取帮助和分享知识。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

4A隔离半桥栅极驱动器ADuM4221系列详解2026-02-04 580

-

UCC27735 700V半桥栅极驱动器技术文档总结2025-10-10 1661

-

TPS54438 3.8V 至 28V 输入、4A、200kHz 至 2.2MHz 同步降压转换器数据手册2025-05-28 1327

-

TPS28226 具有 8V UVLO 的 4A、27V 半桥栅极驱动器,用于同步整流数据手册2025-05-21 791

-

TPS28225-Q1 具有 4V UVLO 的汽车类 4A、27V 半桥栅极驱动器数据手册2025-05-20 840

-

TPS51604-Q1 用于同步降压高频 CPU 的汽车类 4A、28V 半桥栅极驱动器数据手册2025-03-25 885

-

TPS53676适用于CPU/ASIC内核电源轨应用的DCAP+直流/直流降压控制器评估模块2024-11-07 389

-

高频 4A 灌电流同步 MOSFET 驱动器TPS28225数据表2024-03-21 592

-

汽车应用中用于高频CPU内核功率的同步降压场效应晶体管 (FET) 驱动器TPS51604-Q1数据表2024-03-13 437

-

SCT52A40_ 120V,4A,高频高压侧和低压侧栅极驱动器2023-07-03 1603

-

用于同步DC/DC转换的ADuM3220 4A栅极驱动器2021-05-11 816

-

TPS51604 用于高频 CPU 内核功率应用的同步降压·FET 驱动器2018-10-16 871

-

NJW4800 提供4A电流的通用半桥驱动器2010-12-30 1946

全部0条评论

快来发表一下你的评论吧 !