ADMV7320 E频段升频器 SiP,81GHz至86GHz技术手册

描述

概述

ADMV7320 是一款完全集成的系统级封装 (SiP) 同相/正交 (I/Q) 升频器,可在直流至 2 GHz 的中频 (IF) 输入范围和 81 GHz 至 86 GHz 的射频 (RF) 输出范围之间工作。该套件使用由 6× 本地振荡器 (LO) 倍频器驱动的镜像抑制混频器。混频器输出后接可变增益放大器 (VGA) 和功率放大器 (PA),提供 33 dB(典型值)的转换增益。提供差分 I 和 Q 混频器输入,并可通过适用于直接转换应用的差分 I 和 Q 基带波形进行驱动。或者,可以针对单端应用使用一个外部 90° 混合和两个外部 180 混合来驱动输入。

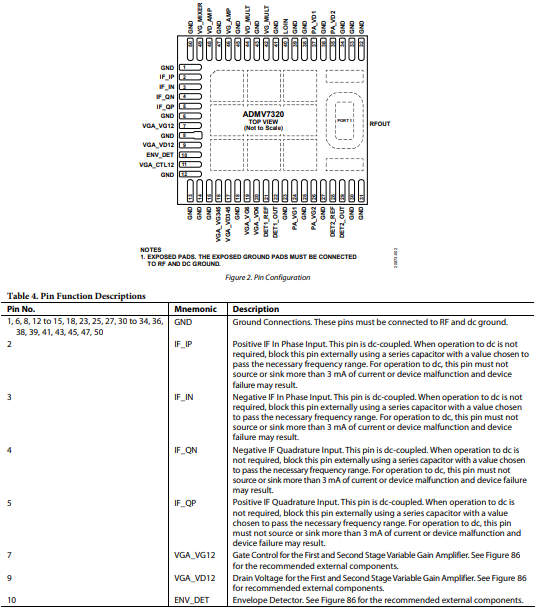

ADMV7320 采用完全集成的表面安装 50 端子 16.00 mm × 14.00 mm 芯片阵列小外形无铅腔面 (LGA_CAV) 封装。ADMV7320 的工作温度范围为 −40°C 至 +85°C。

数据表:*附件:ADMV7320 E频段升频器 SiP,81GHz至86GHz技术手册.pdf

特性

- 最大转换增益:33 dB(典型值)

- 增益调节范围:40 dB(最小值)

- P

SAT:增益 = 23.5 dB 和 19.5 dB 时为 26 dBm(典型值) - OIP3:增益 = 23.5 dB 且每个信号音的 P

OUT= 16.5 dBm 时为 31 dBm(典型值) - OP1dB:增益 = 23.5 dB 和 19.5 dB 时为 25 dBm(典型值)

- 内置功率检波器

- 用于 LO 调零的内置包络检波器

- 完全集成的表面安装 50 端子 16.00 mm × 14.00 mm LGA_CAV 封装

应用

- E 频段通信系统

- 高容量无线回程

- 测试与测量

- 航空航天和防务

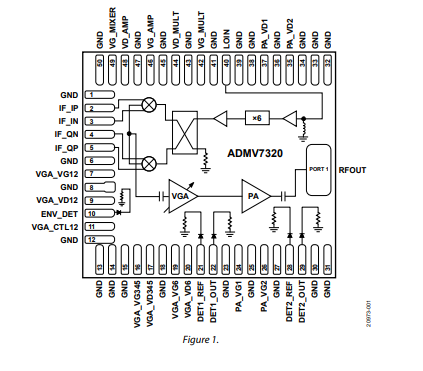

框图

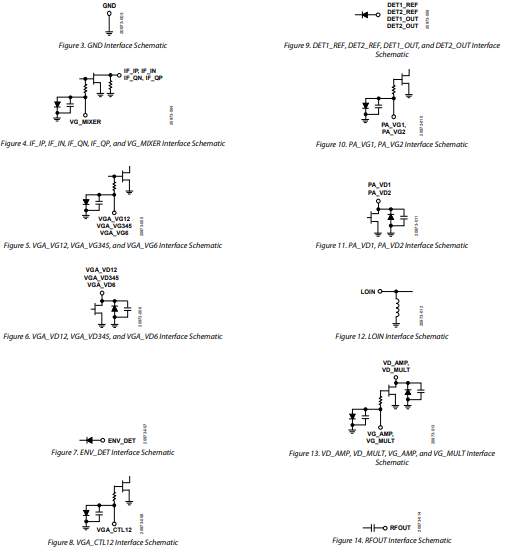

引脚配置描述

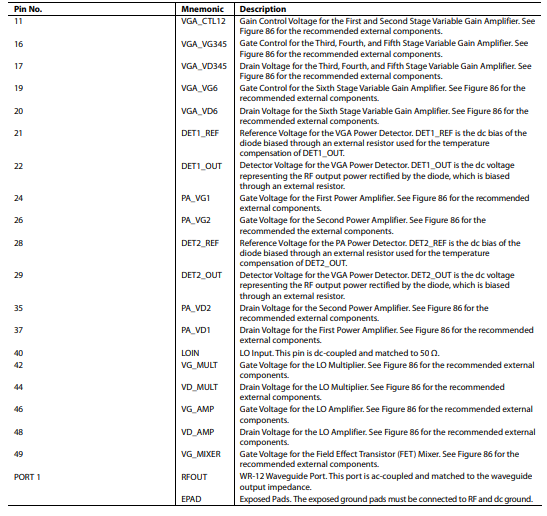

接口示意图

工作原理

ADMV320 是一款完全集成的系统级封装(SiP)同相 / 正交(I/Q)上变频器,由三个功能模块组成:混频器及本振(LO)路径、包络检波器、可变增益放大器(VGA)和功率检波器,以及功率放大器。

混频器和本振路径

第一个功能模块是一个由 6 倍频器驱动的砷化镓(GaAs)I/Q 上变频器。6 倍频器允许使用较低频率的本振源。本振输入信号频率范围在 13.4 GHz 至 14.6 GHz 之间。6 倍频器通过芯片内的三个 2 倍频器实现。每个 2 倍频器都有一个本振缓冲放大器,以实现典型的芯片上负载。本振路径的驱动电平约为 4 dBm。本振信号通过芯片内的巴伦馈入一个正交分路器。该分路器产生两路平衡的信号,分别驱动 I 路和 Q 路混频器。I 路和 Q 路混频器的射频输出随后被送入芯片内的威尔金森功率合成器进行合成,然后进入下一个功能模块。

包络检波器、可变增益放大器和功率检波器

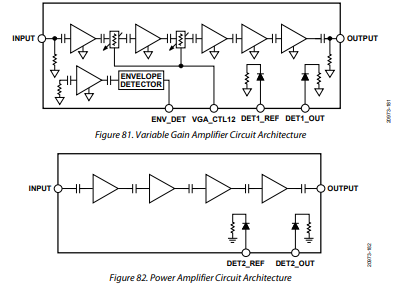

第二个功能模块是一个可变增益放大器(VGA,见图 81)。该 VGA 利用多级增益和级联的高可变衰减级,形成一个低噪声、高线性度的可变增益放大器。VGA 的第一级是一个低噪声前置放大器。第一级的输出通过耦合器进行耦合,然后通过可变增益驱动级进一步放大。该耦合信号用于外部监控,以实现精确的参考检测。检波器 1(DET1)是一个集成的耦合器,用于辅助相关检波器进行温度补偿。功率检波器的典型应用电路如图 83 所示。有关各个功能模块偏置的更多详细信息,请参见 “应用信息” 部分。VGA 的输出随后被送入下一个功能模块 ADMV320。

功率放大器和功率检波器

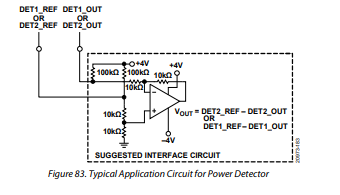

第三个模块是一个功率放大器,它使用四个级联的增益级来形成放大器,如图 82 所示。在最后一级的输出处,耦合器取出一小部分输出信号。耦合后的信号被送入芯片上的二极管检波器,用于外部监控输出功率。检波器 2(DET2)是一个集成的耦合器,用于辅助相关检波器进行精确的参考检测。

功率检波器的典型应用电路如图83所示。有关不同模块偏置的更多信息,请参见“应用信息”部分。

-

探索ADMV7810:81 GHz - 86 GHz E波段功率放大器的卓越性能2026-01-05 349

-

HMC8121 81GHz至86GHz,E频段可变增益放大器技术手册2025-04-19 1403

-

HMC7587 E频段I/Q下变频器,81GHz至86GHz技术手册2025-03-28 1190

-

ADMV7420 E频段低噪声下变频器SiP,81GHz至86GHz技术手册2025-03-26 1320

-

HMC8142集成功率检波器的81GHz至86GHz E频段功率放大器技术手册2025-03-12 1218

-

ADMV7810具有功率检测器的81GHz到86GHz、1WE频段功率放大器技术手册2025-03-11 1098

-

UG-1597:ADMV7320评估板用户指南2021-05-14 755

-

ADMV7420:E波段低噪声下变频器Sip,81 GHz至86 GHz数据表2021-04-17 862

-

ADMV7810:81 GHz至86 GHz,1 W E波段功率放大器,带功率检测器数据表2021-04-15 904

-

HMC7585LG:E波段更新SIP 81-86 GHz数据Sheet2021-04-14 708

-

ADMV7320: E-Band Upconverter SiP, 81 GHz to 86 GHz Data Sheet2021-01-28 778

-

ADMV1013ACCZ微波升频器产品介绍2019-07-09 1442

全部0条评论

快来发表一下你的评论吧 !