Low-K材料在芯片中的作用

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了芯片制造中的Low-K材料。

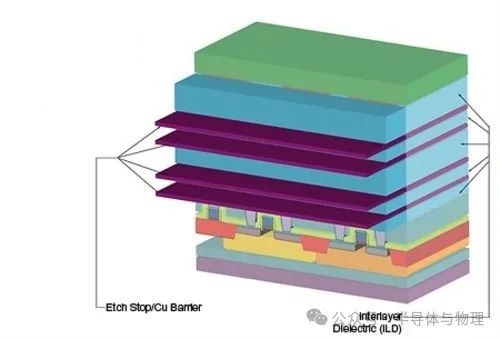

Low-K材料是介电常数显著低于传统二氧化硅(SiO₂,k=3.9–4.2)的绝缘材料,主要用于芯片制造中的层间电介质(ILD)。其核心目标是通过降低金属互连线间的寄生电容,解决RC延迟(电阻-电容延迟)和信号串扰问题,从而提升芯片性能和集成度。

Low-K材料在芯片中的作用

1. 降低RC延迟

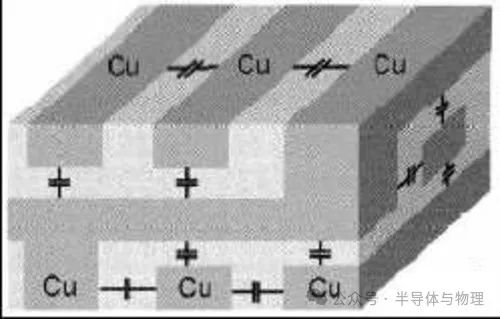

随着芯片制程微缩,金属互连线间距缩小,传统SiO₂的电容效应导致信号延迟和功耗增加。Low-K材料通过减少互连线间的寄生电容,使RC延迟降低并显著提升芯片速度。

2. 抑制信号串扰

互连线间的耦合电容与k值成正比。Low-K材料通过降低k值,减少电容耦合效应,使相邻线路的串扰噪声降低,允许更密集的布线设计。

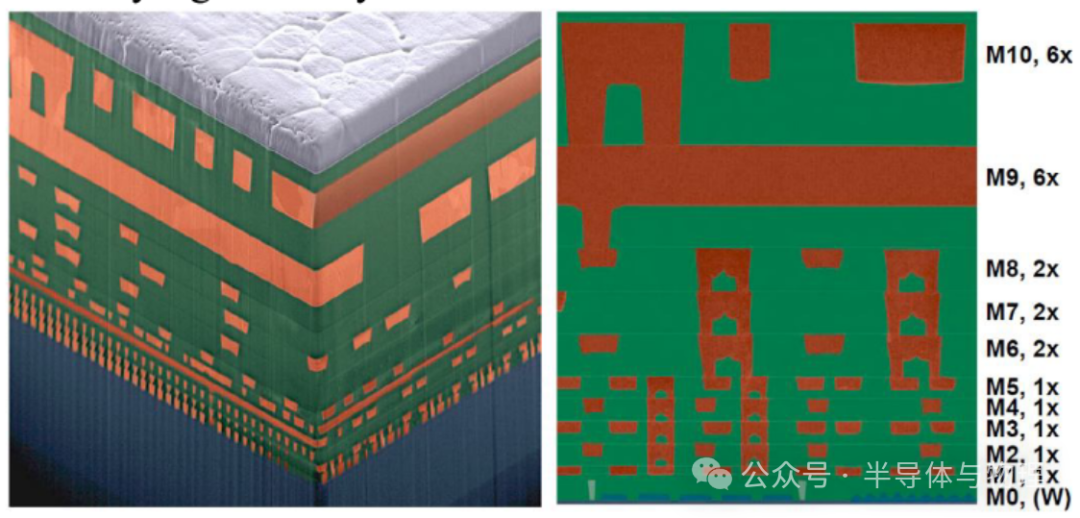

3. 支持多层互连结构

现代芯片采用10层以上的金属互连,Low-K材料的高绝缘性和低热膨胀系数可避免层间应力开裂,保障结构稳定性。

Low-K材料的分类与合成原料

Low-K材料根据成分可分为三大类,其合成工艺和原料差异显著:

| 类型 | 典型材料 | 合成原料与工艺 | k值范围 |

|---|---|---|---|

| 无机多孔材料 | 多孔氧化硅 | 溶胶-凝胶法,前驱体为TEOS | 2–2.5 |

| 有机高分子材料 | 聚酰亚胺、含氟聚合物 | 旋涂法,前驱体为聚酰亚胺单体或PTFE | 1.5–2.7 |

| 有机/无机复合材料 | 甲基倍半硅氧烷(MSQ) | CVD或旋涂,前驱体为硅氧烷衍生物 | 2.2–2.8 |

LOW-K材料工艺:

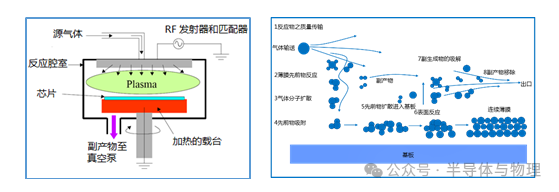

化学气相沉积(CVD)

:用于沉积MSQ等材料,需使用含碳/氟前驱体(如SiCOH),通过PECVD提升薄膜致密度。

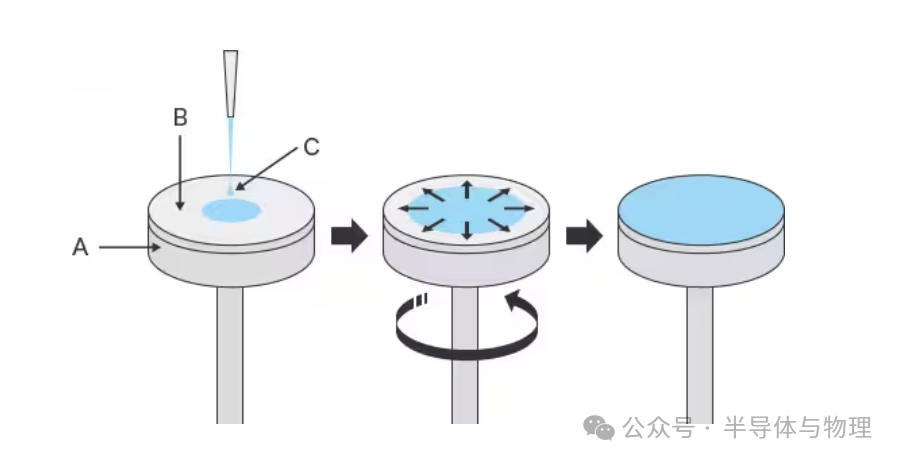

旋涂法

:适用于有机材料,需优化溶剂挥发速度以避免薄膜裂纹。

Low-K材料的制造工艺挑战

1. 机械强度与热稳定性

多孔材料易脆裂,需通过掺杂纳米颗粒如SiO₂纳米球提升硬度。例如,掺入10% SiO₂可使多孔Low-K薄膜的杨氏模量从3 GPa提升至8 GPa。

2. 铜扩散阻挡

Low-K材料的孔隙可能被铜原子渗透,需集成超薄阻挡层(如2nm的TiN)以防止互联金属铜扩散导致漏电。

3. CMP兼容性

材料疏松易导致抛光不均匀,需要使用压力抛光液(如含二氧化铈磨料)。

-

蓝牙芯片中的晶振:内部集成与功能解析2024-10-24 6320

-

hmc704 BIAS引脚影响相噪请问这个引脚在芯片中起什么作用?2018-09-04 4582

-

Scratch Testing of Low-k Diele2010-08-17 830

-

磁性材料在芯片中的应用2011-01-05 3035

-

晶振在芯片中的作用2022-08-23 12001

-

Aston™ 过程质谱提高 low-k 电介质沉积的吞吐量2023-06-21 1165

-

锁相环是什么?在dsp芯片中有什么作用2023-09-02 4691

-

芯片制程中常见的介质材料有哪些?都有什么作用?2023-10-19 9339

-

金在芯片中有什么用途呢?金在芯片中的应用和优势介绍2023-12-22 4610

-

误差放大器在LDO芯片中的作用2024-09-11 2717

-

芯片中介质及其性能解析2025-02-10 2957

-

Cu/low-k互连结构中的电迁移问题2025-03-13 2790

-

FIB制备Low-K材料的TEM样品面临难点2025-04-29 1392

-

为什么芯片需要低介电常数材料2025-05-15 1958

-

电子束对Low-K材料有什么影响2025-05-27 1299

全部0条评论

快来发表一下你的评论吧 !