ADRF6658集成IF放大器的宽带双通道RX混频器技术手册

描述

概述

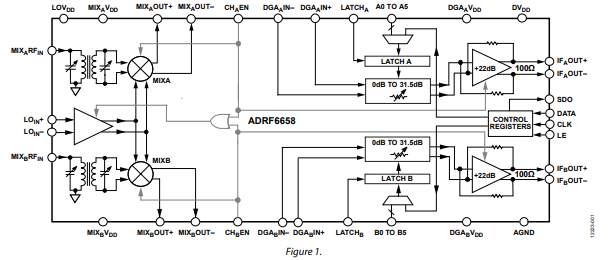

ADRF6658是一款高性能、低功耗、宽带、双通道无线电频率(RF)下变频器,集成中频(IF)数字控制放大器(DGA),适用于宽带、低失真基站无线电接收机。

双通道Rx混频器为双平衡吉尔伯特单元混频器,具有高线性度和出色的图像抑制能力。 两款混频器均可将50 Ω RF输入转换为开集宽带IF输出。 在混频器输入前,RF输入端的内部可调谐巴伦可抑制RF信号谐波并衰减带外信号,从而减少输入反射和带外干扰信号。 灵活的本振(LO)架构允许使用差分或单端LO信号。

双通道IF DGA基于ADL5201和ADL5202,固定差分输出阻抗为100 Ω。通过片内SPI,或支持闩锁功能的独立6位并行端口,可在31.5 dB范围内调节增益,步进为0.5 dB。 从混频器输入至IF放大器输出的各通道以及LC级间带通滤波器,可实现26.5 dB的最大电压转换增益。

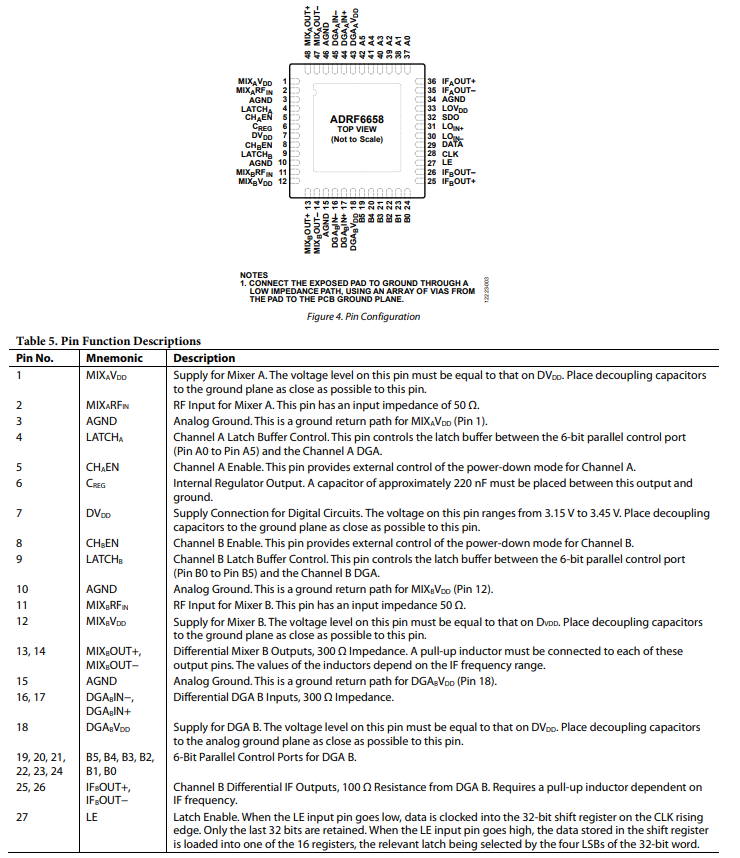

ADRF6658采用ADI公司的高速SiGe工艺制造,提供紧凑型7 mm × 7 mm、48引脚LFCSP封装,工作温度范围为−40°C至+105°C。

数据表:*附件:ADRF6658集成IF放大器的宽带双通道RX混频器技术手册.pdf

应用

- 蜂窝基站和无线基础设施接收机(W-CDMA、TD-SCDMA、WiMAX、GSM、LTE、PCS、DCS、DECT)

- 有源天线系统

- PTP无线电链路下变频器

- 无线局域网(LAN)和有线电视设备

特性

- 宽带、双通道、有源下变频混频器

- 低失真、快速建立、IF DGA

- RF输入频率范围:690 MHz至3.8 GHz

- RF输入端的可编程巴伦

- 差分和单端LO输入模式

- 差分IF输出阻抗:100 Ω

- 可通过三线式串行端口接口(SPI)进行编程

- 对于RF=1950 MHz、IF=281 MHz、高线性度模式:

- 电压转换增益,包括IF滤波器损耗:−5至+26.5 dB

- (更多详细信息,请参见数据手册)

- 灵活的省电模式,针对低功耗操作

- 通道使能后的上电时间:100 ns,典型值

- 3.3 V单电源

- 高线性度模式:440 mA

- 低功耗模式:260 mA

功能框图

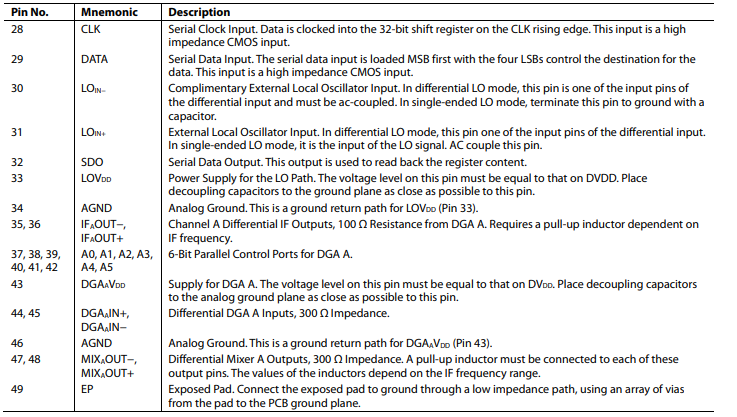

引脚配置描述

工作原理

双混频器核心

ADRF6658提供两个基于吉尔伯特单元设计的双平衡有源混频器。射频(RF)输入、本振(LO)输入和中频(IF)输出相互独立,在1 dB压缩点(P1dB)下可提供最大30 dBm的射频输入功率。混频器的输入阻抗设计为50 Ω,外部射频扼流圈连接到电源。

射频端口

在ADRF6658的每个通道(MIX_RFEx和MIX2_RFEx)中,射频输入单端信号通过巴伦转换为差分信号,然后馈入混频器部分。混频器的调谐由两个寄存器控制:射频巴伦输出缓冲器(Cac0)在寄存器13中(Bits[DB12:DB10]),以及射频巴伦输出缓冲器(Cac1)在寄存器13中(Bits[DB19:DB17])。

混频器偏置电路

带隙基准电路生成混频器使用的参考电流。混频器本振电路的偏置电流可通过寄存器13中的Bits[DB26:DB25]进行编程设置。

电压转换(V to I)电路

从巴伦来的差分射频单端信号,在内部生成的参考电流的作用下,输入到一个电压 - 电流转换器(MIX_RFEx或MIX2_RFEx引脚),该转换器将电压转换为输出电流。混频器的偏置电流和V to I电路的偏置电流可通过寄存器13中的Bits[DB24:DB22]进行调整。调整电流可改善I/Q3和P1dB性能,但会增加单边带噪声系数(SSB NF)。调整电流超过一定范围后,混频器转换增益在很宽的输入功率范围内会接近恒定。混频器V to I增益设置允许动态调整增益,设置为3或4时会影响转换增益,同时保持良好的I/Q3和SSB NF性能。

混频器断电

通过对寄存器13中的Mixer A使能位(Bit DB35)和Mixer B使能位(Bit DB34)进行编程,可以关闭混频器。对这些位进行编程设置为低电平,可关闭混频器。

混频器输出

混频器输出端使用一对150 Ω的电阻连接到正电源,这样可提供300 Ω的差分输出阻抗,与增益放大器(DGA)模块的输入阻抗匹配。可以通过使用输出缓冲器(将射频扼流圈连接到正电源),或使用中心抽头连接到正电源的输出变压器,来下拉混频器输出。混频器输出可进行交流耦合,并可在高达5.4 GHz的频率下工作。

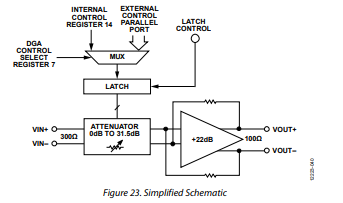

数字增益放大器(DGA)基本结构

在每个通道中,ADRF6658内置了一个可变增益放大器(DGA)。每个放大器由一个300 Ω差分输入阻抗的数字控制无源衰减器、一个增益为10 dB的有源放大器以及每个输出端的100 Ω负载组成。DGA模块的输入阻抗与混频器的输出阻抗匹配。

每个放大器的增益可通过串行控制寄存器,或通过外部6位并行端口进行独立编程。DGA控制选择位由寄存器14中的Bit DB22决定。对该位进行编程设置为0时,通过寄存器14中的Bits[DB17:DB12]设置增益;设置为1时,增益由施加到6位外部并行控制接口(通道A为Pin A0至A5,通道B为Pin B0至B5)的二进制值设置。

输入系统

每个放大器输入端的直流电压设置为约1.1 V。这两个独立的内部电压参考电路无法访问,也不能进行调整。

通过设置寄存器14中的Bit DB5和Bit DB4,可以使放大器断电。当放大器断电时,每个放大器的静态电流降至约10 μA(典型值)。无论寄存器14中Bit DB5和Bit DB4的状态如何,输入端的直流电平仍保持在约1.1 V。

-

HMC684集成LO放大器的BiCMOS混频器技术手册2025-04-02 1016

-

ADRF6658评估软件2021-05-31 829

-

ADRF6602:1550 MHz至2150 MHz Rx混频器,集成小数N PLL和VCO数据表2021-05-24 699

-

ADRF6658:集成中频放大器的宽带双接收混频器2021-05-12 920

-

UG-968:评估ADRF6612/ADRF6614,700 MHz至3000 MHz Rx双混频器,集成小数N PLL和压控振荡器2021-05-07 799

-

ADRF6658 Gerber文件2021-04-09 677

-

ADRF6658 Gerber Files2021-02-19 710

-

ADL5811/2集成宽带LO放大器的性能特点及应用2019-07-10 2991

-

LTC559x双通道无源下变频混频器系列介绍2019-07-04 1821

-

ADRF6658 集成IF放大器的宽带双通道RX混频器2019-02-22 858

-

超宽带低噪声放大器和混频器的研究与设计2015-12-21 881

-

ADI推出高集成宽带无源混频器ADL5811/ADL58122011-05-13 1459

-

有源混频器ADRF66042010-08-12 1467

全部0条评论

快来发表一下你的评论吧 !