ADRF6603 1,100 MHz至3,200MHz接收混频器,集成小数N分频PLL和VCO技术手册

描述

概述

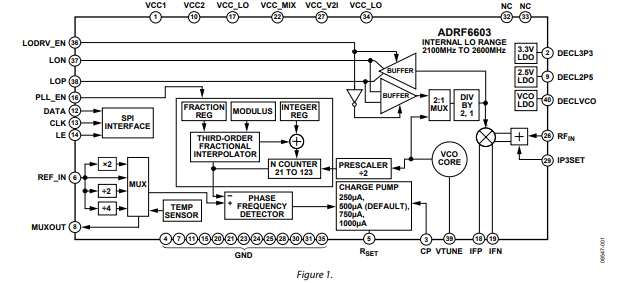

ADRF6603是一款高动态范围有源混频器,集成小数N分频锁相环(PLL)和压控振荡器(VCO),用于内部混频器LO的产生。

ADRF6603与ADRF6602共同构成了一个集成PLL/混频器系列,涵盖2100 MHz至2600 MHz频率范围。

数据表:*附件:ADRF6603 1,100 MHz至3,200MHz接收混频器,集成小数N分频PLL和VCO技术手册.pdf

PLL基准输入支持12 MHz至160 MHz范围内的输入频率。PFD输出控制一个电荷泵,其输出驱动一个片外环路滤波器。

环路滤波器输出再施加于一个集成式VCO。VCO输出(2× fLO)施加于一个LO分频器和一个可编程PLL分频器。可编程PLL分频器由一个Σ-Δ调制器(SDM)进行控制。SDM的模数可以在1至2047范围内编程。

有源混频器可将单端50 Ω RF输入转换为200 Ω差分IF输出。IF输出的工作频率最高可达500 MHz。

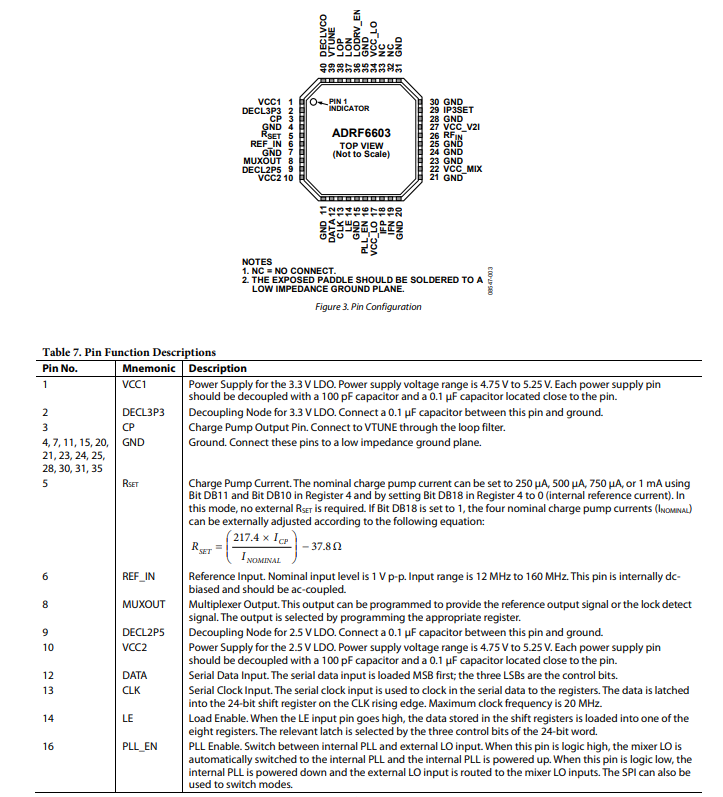

ADRF6603采用先进的硅-锗BiCMOS工艺制造,提供40引脚、裸露焊盘、6 mm × 6 mm、符合RoHS标准的LFCSP封装,额定温度范围为−40°C至+85°C。

特性

- 集成小数N分频PLL的Rx混频器

- RF输入频率范围:1100 MHz至3200 MHz

- 内部LO频率范围:2100 MHz至2600 MHz

- 输入P1dB:14.6 dBm

- 输入IP3:27 dBm

- 通过外部引脚优化输入IP3

- SSB 噪声系数

IP3SET引脚开路:14.2 dBIP3SET引脚3.3 V:15.2 dB - 电压转换增益:6.9 dB

- 200 Ω IF输出匹配阻抗

- IF 3 dB 带宽:500 MHz

- 可通过三线式SPI接口进行编程

- 40引脚、6 mm × 6 mm LFCSP封装

框图

引脚配置描述

基本工作连接

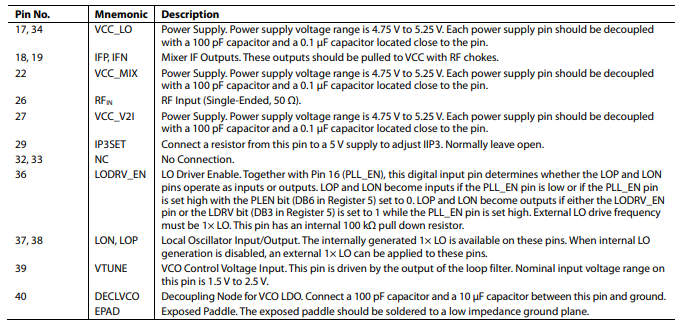

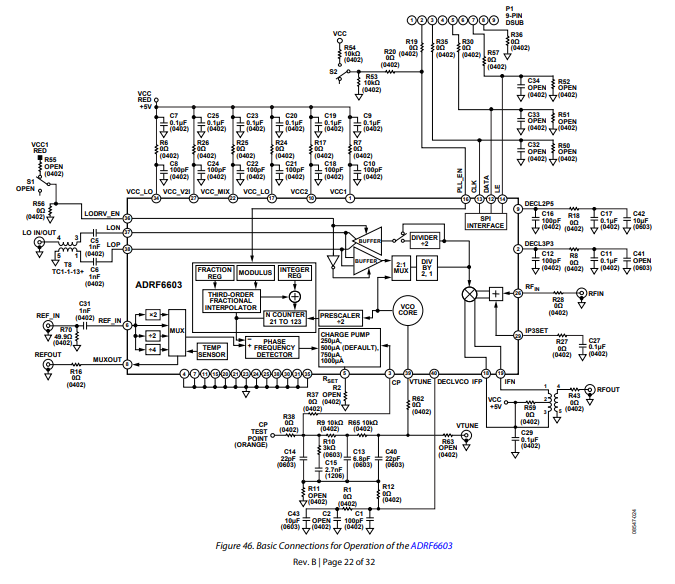

图46展示了ADRF6603评估板的原理图。六个电源引脚应分别使用100pF和0.1μF电容进行去耦,电容应尽可能靠近器件放置。此外,内部去耦节点(DECL3P、DECL3N、DECL2P和DECL2N)也应按图46所示的电容值进行去耦。

射频输入为交流耦合,且无需外部偏置。中频输出为集电极开路,需要一个偏置电感来将这些输出连接到VCC。

在RF输入上施加1V峰峰值(正弦波输入时为0.353V均方根值)的差分摆动,会得到4.7dBm的中频输出功率。

PLL的参考频率应为12MHz至160MHz,应施加到REF_IN引脚。参考信号应进行交流耦合,并如图46所示用50Ω电阻端接。该参考信号可以是多路复用器输出引脚(MUXOUT)上的分频版本,可从芯片背面引出。也可以在多路复用器输出引脚上选择锁定检测信号和与环境温度成比例的电压。

环路滤波器连接在CP和VTUNE引脚之间。连接完成后,内部压控振荡器(VCO)将工作。有关环路滤波器选项的信息,请参见“评估板配置”部分。

也可以使用外部VCO进行工作。在这种情况下,环路滤波器组件应接地。外部VCO的输出应连接到LOP和LON引脚上器件的输入电压引脚。必要时可使用巴伦将VCO的输出连接到LOP和LON引脚。

-

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc2025-05-22 128

-

EVADRF6603 ADRF6603评估板2021-06-06 704

-

ADRF6604:1200 MHz至3600 MHz接收混频器,集成小数N PLL和VCO数据表2021-05-27 815

-

ADRF6612:700 MHz至3000 MHz双无源接收混频器,集成PLL和VCO数据表2021-05-24 757

-

ADRF6704:2500 MHz至2900 MHz集成小数N PLL和VCO的正交调制器数据表2021-05-12 854

-

UG-968:评估ADRF6612/ADRF6614,700 MHz至3000 MHz Rx双混频器,集成小数N PLL和压控振荡器2021-05-07 803

-

ADRF6603:1100 MHz至3200 MHz接收混频器,带集成小数N PLL和压控振荡器数据表2021-04-30 730

-

ADRF6614:700 MHz至3000 MHz,双无源接收混频器,集成PLL和VCO数据表2021-04-24 734

-

ADRF6603 1,100 MHz至3,200 MHz接收混频器,集成小数N分频PLL和VCO2019-02-22 545

-

高动态范围有源混频器ADRF66552010-08-12 1798

全部0条评论

快来发表一下你的评论吧 !