小数分频频率合成器的实现方法

电子说

描述

小数分频频率合成器的实现方法有多种,如Pulse swallowing、Pulse interpolatoin、Wheately random jittering、Σ-Δ modulation[1],其中Σ-Δ modulation架构以其优良的相噪指标及全数字化而成为小数分频频率合成器的主流。本文旨在分析Σ-Δ量化噪声对小数分频频率合成器相位噪声及杂散的影响,找到适合于小数分频频率合成器的Σ-Δ调制器。

1相位噪声

基于锁相环闭环回路实现小数分频频率合成器,建立线性数学模型,分析其相位噪声源及传递函数。

1.1 相位噪声模型

Rohde已经阐明[2],PLL的每个组成部分都产生噪声。小数分频频率合成器主要相位噪声源有参考时钟相位噪声θref(t)、PFD相位噪声θPFD(t)、VCO相位噪声θVCO(t)、分频器相位噪声θdiv(t)、Σ-Δ量化噪声。

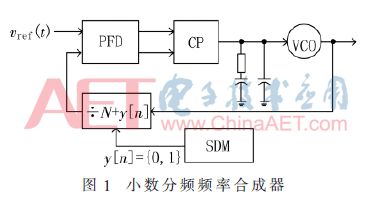

基于锁相环小数分频频率合成器如图1所示。

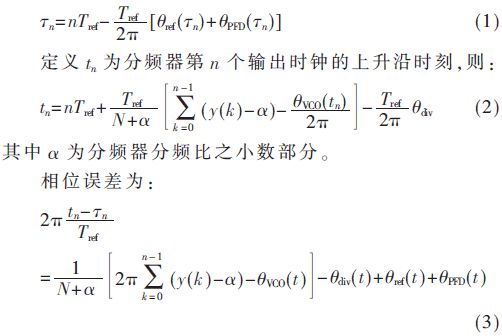

定义τn为第n个参考时钟的上升沿时刻,则:[3]

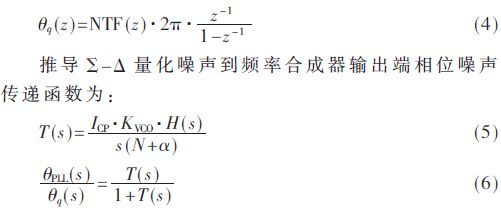

由相位误差公式及图1,可以推得图2所示的Σ-Δ小数分频频率合成器相位噪声线性模型。

1.2 相位噪声分析

Σ-Δ小数分频频率合成器相位噪声源到输出端的传递函数除VCO相位噪声传递函数为高通滤波传递函数外,其余噪声源到输出端的传递函数均为低通滤波传递函数。本文着重分析Σ-Δ量化噪声对输出相位噪声的影响。

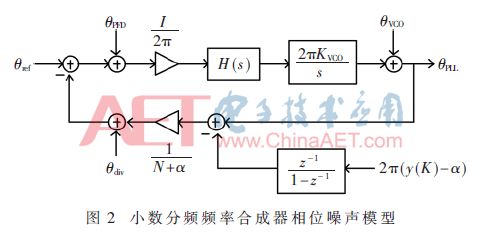

图2中(y(k)-α)为Σ-Δ量化噪声q(t),其Z域传递函数NTF(z)=(1-z-1)L[4]。由量化噪声注入到PLL的相位噪声为:

1.2.1 Σ-Δ量化器阶数对相位噪声的影响

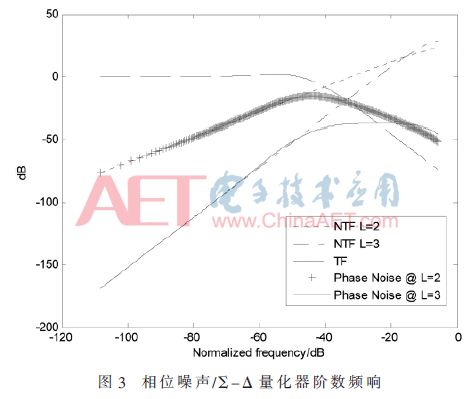

MATLAB绘制不同Σ-Δ量化器阶数,量化噪声引起的PLL输出相位噪声频域响应,如图3所示。曲线“.”为二阶Σ-Δ量化器注入到频率合成器的相位噪声

可见,Σ-Δ量化器阶数越高,小数分频频率合成器带内相位噪声越低。

1.2.2 环路带宽对相位噪声的影响

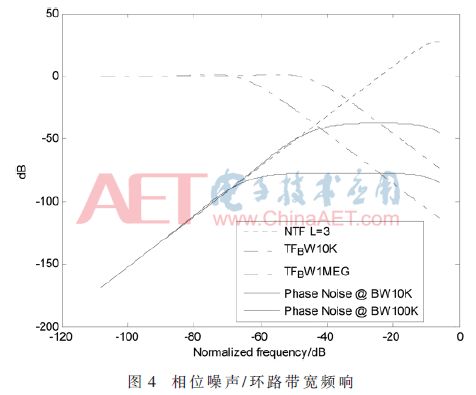

图4为3阶Σ-Δ量化器,在不同PLL环路滤波器带宽条件下,小数分频频率合成器带相位噪声频谱图。曲线“.”为三阶Σ-Δ量化器相位噪声;曲线“.-”分别为带宽10 kHz与1 MHz频率合成器相位噪声传递函数;实线分别为带宽10 kHz与1 MHz的三阶Σ-Δ频率合成器相位噪声。

由此可见,环路带宽越小,由Σ-Δ量化引起的相位噪声越低。

2相位噪声优化

通过1.2.1分析,高阶Σ-Δ量化器可以将量化噪声推到高频,使得带内量化噪声降低,频率合成器输出相位噪声也降低。

由一阶调制器构成的MASH高阶Σ-Δ量化器,无条件稳定,但是MASHΣ-Δ量化器存在的问题是它的输出是多位,频率合成器之分频器设计复杂,且分频比会在多模之间切换,会给鉴相器的输出引入高频抖动。

高阶单环路Σ-Δ量化器存在稳定性问题。为使高阶单环路Σ-Δ量化器稳定工作,其噪声传递函数增益需满足[5]:

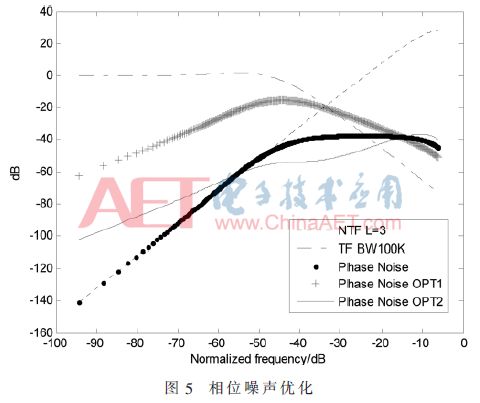

通过高阶环路引入前馈通路,改变NTF增益,使其稳定工作。但是带来的缺点是NTF对量化噪声的抑制低于理想NTF(z)=(1-z-1)L对量化噪声的抑制。本文提出,信号在输入Σ-Δ量化器之前,添加高频零点,从而使内置二阶Σ-Δ量化器的小数分频频率合成器获得可以与高阶Σ-Δ频率合成器相当的相位噪声指标。相位噪声优化如图5所示。

图5中,曲线“--”为三阶Σ-Δ量化器相位噪声;曲线“.-”相位噪声传递函数;曲线“+”为二阶Σ-Δ频率合成器相位噪声;曲线“.”为三阶Σ-Δ频率合成器相位噪声;实线为插入高阶零点后的二阶Σ-Δ频率合成器相位噪声。显而易见,输入信号插入高频零点后,二阶Σ-Δ频率合成器可以获得高阶Σ-Δ量化频率合成器性能。

另一种优化相位噪声的方法是降低频率合成器环路带宽,如1.2.2分析所示。但是为抑制VCO相位噪声,需要增加频率合成器带宽[6]。设计中需要折中优化,找到最优带宽。

需要注意的是,Σ-Δ频率合成器锁定后,Σ-Δ量化器输出频率等于参考时钟频率,提高参考时钟频率,量化器工作频率也提高,可以把量化噪声推到更高频,进入信号带内的相位噪声更低,不需要通过压低频率合成器带宽来降低相位噪声,使得Σ-Δ频率合成器带宽提升。

3杂散

分析Σ-Δ频率合成器杂散产生机理,从优化Σ-Δ调制器角度,提出杂散抑制措施。

3.1 杂散分析

Σ-Δ频率合成器由于其反馈支路分频器分频比动态切换,反馈信号上升沿时刻为:

此外,Σ-Δ量化器位数不够,会导致量化器饱和,产生很大的杂散。同时,量化器饱和也会恶化噪声传递函数NTF,高频量化噪声会进入信号带内。

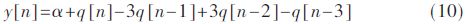

三阶Σ-Δ量化器时域表达式为:

归一化量化噪声|q[n]|≤0.5,可得|y[n]|≤|a|+4。

至少需要3 bit表示y[n],量化器才不会饱和[7]。

3.2 杂散抑制

优化Σ-Δ量化器设计,抑制杂散。

为抑制Σ-Δ频率合成器固有杂散,可以在Σ-Δ量化器的输入信号上迭加一个能量很低的白噪声[8]。迭加白噪声后的输出频率误差部分可表达为(y[n]-α+qwhite)×fref。白噪声的存在使得频率误差部分不再固定出现在α×fref与(1-α)×fref及其谐波处的杂散。

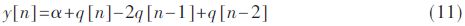

为降低Σ-Δ频率合成器相位噪声,需要高阶Σ-Δ量化器。由3.1节分析可知,高阶Σ-Δ量化器需要量化器位数高,才不至于导致量化器饱和而产生杂散。但是量化器位数高,y[n]取值范围宽,输出频率杂散部分(y[n]-α)×fref会产生更多的谐波,会产生更大的瞬时相位差,要鉴相器具有很高的线性度[9]。从抑制杂散角度看,Σ-Δ量化器阶数不宜高。对于二阶Σ-Δ量化器,时域表达式为:

归一化量化噪声|q[n]|≤0.5,可得|y[n]|≤|a|+2。y[n]可由2 bit表示,量化器才不会饱和。相比于高阶Σ-Δ频率合成器,2阶Σ-Δ频率合成器杂散成分小。

4芯片实现

基于SMIC0.13 μm RF制程,设计了1.575 GHz PLL IP。PLL之小数分频通过数字二阶Σ-Δ量化器的输出动态切换PLL反馈路径分频比实现,满足GPS时钟超低相噪/杂散指标,该IP已量产于GPS接收机芯片,可获得-150 dBm接收灵敏度。

5结论

本文分析研究了Σ-Δ量化器对小数分频频率合成器相位噪声及杂散的影响,并建立小数分频频率合成器线性数学模型,通过MATLAB验证理论分析的可靠性。同时,提出优化Σ-Δ量化器措施,以降低小数分频频率合成器相位噪声与杂散。本文认为,输入信号预先插入高频零点,且迭加低能量白噪声的二阶Σ-Δ量化器适合于Σ-Δ频率合成器。通过提高Σ-Δ驻量化器工作频率可提升频率合成器带宽。

-

Σ-Δ调制频率合成器【转】2012-08-02 0

-

详解频率合成器高性能架构的实现2019-07-08 0

-

ΣΔ技术在锁相环频率合成器中的应用2009-08-19 577

-

小数分频合成器2008-04-21 953

-

Σ-Δ调制频率合成器2009-05-14 1763

-

ADF4158-直接调制波形产生6.1 GHz小数N分频频率合成器2012-02-03 2267

-

△∑小数频率合成器中的小数分频器设计2016-05-24 582

-

小数分频技术与ADF4193快速开关频率合成器的研究2019-05-24 1907

-

UG-167:针对ADF4153小数N分频PLL频率合成器的评估板2021-03-19 548

-

ADF4159:直接调制/快速波形产生13 GHz小数N分频频率合成器2021-03-20 765

-

ADF4155:整数N/小数N分频PLL频率合成器2021-03-20 608

-

ADF4153:小数N分频频率合成器2021-03-21 586

-

ADF435微波宽带频率合成器资料分享2022-07-23 542

-

将MAX2902与外部频率合成器组合2023-03-03 758

-

AN-1879小数N分频频率合成器2024-09-23 105

全部0条评论

快来发表一下你的评论吧 !