高速信号设计-Via structure

电子说

描述

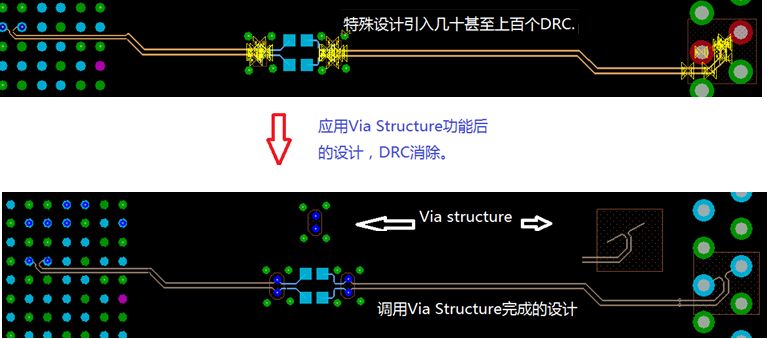

随着PCB上高速信号速率的提升,高速设计方案会在PCB设计中引入比较多的DRC,最常见的是K/L、K/V等DRC。设计者允许这些DRC的存在,但是这些DRC的占比已经超过整板DRC的50%以上,他们的存在会降低ALLEGRO的运行速度,甚至延长某些操作的运行时间(例如:更新DRC,Database check等),还影响投板前的DRC排查效率和质量。Allegro17.2的Via structure 功能,可以帮助设计者去除这些DRC,提升设计效率和设计质量。

步骤一:根据需求创建Via structure

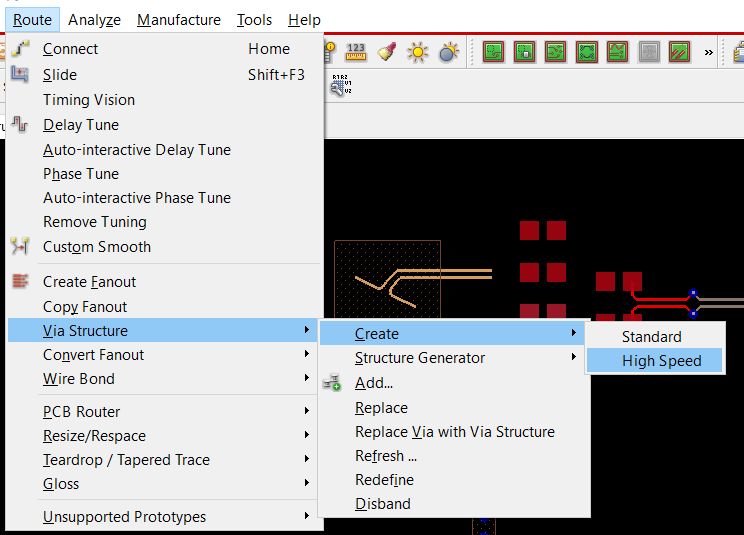

设计者可以根据需求,创建不同的Via structure,Via structure可以包含您所需要的设计对象,例如Via、Shape(包括RKO)、Cline等。Via structure的创建方法很简单,找到如下的命令,按照Command栏的提示即可顺利完成。下面举一些我们已有的例子,仅用于说明使用方法。

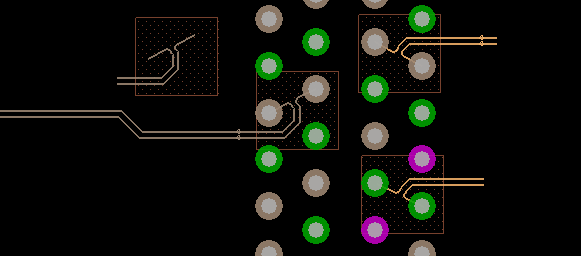

1. 芯片侧的Via structure样例,Via structure可以只是Cline,也可以是Via、shape、Cline的合成体。具体包含的对象,由设计者决定。

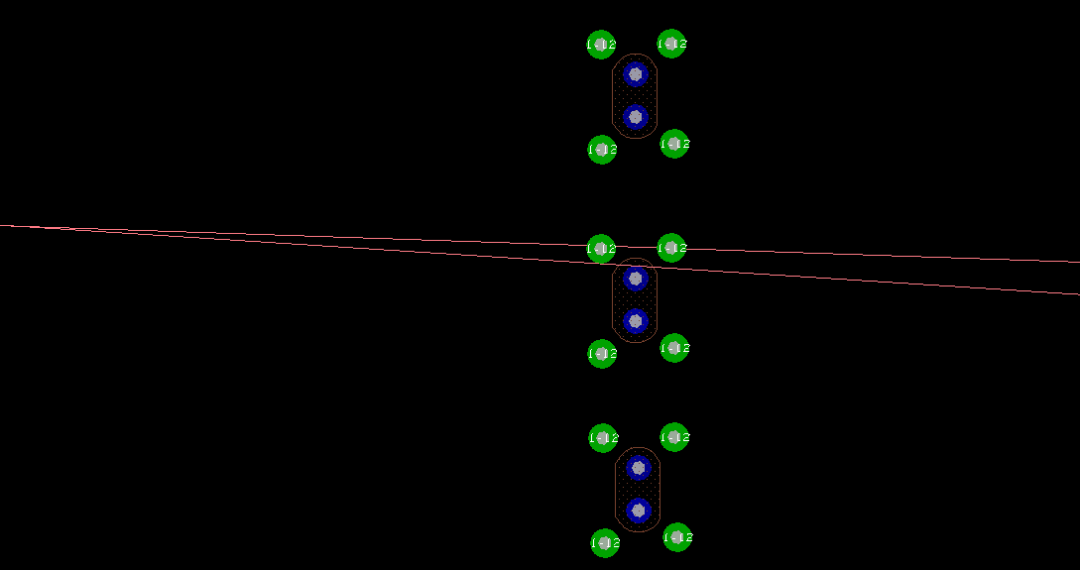

2. 高速布线层切换的Via structure样例。

3. 连接器侧的Via structure样例。可以只包含Cline和您所需的其他对象。

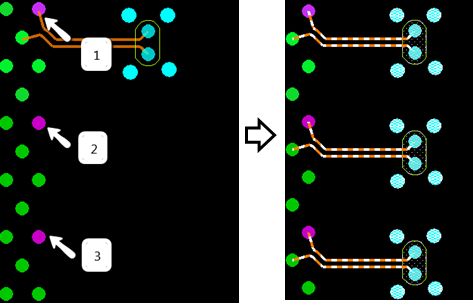

步骤二:在设计中调用Via structure

Via structure定义完成后,我们可以在设计中直接调用,然后将其连接起来,即可完成高速链路的布线。如下的实例中,应用上面提到的几个Via structure样例,完成了一个高速链路的设计。设计完成后,K/L、K/V等报错不再出现,设计变得更加有效,更有利于提升设计质量。

Allegro的Via structure功能,可以帮助设计者消除PCB上为了落实设计需求而引入的合理的DRC。让设计更加高效,高质量,且可以促进高速信号设计的一致性(每次遇到同类设计,都可以直接调用已有的模板)。

-

过孔是什么意思,过孔(via)简介2010-03-16 0

-

原创|高速信号PCB设计处理的通用原则2017-02-07 0

-

详解Via孔的作用及原理2018-12-03 0

-

Via孔的作用和原理2019-06-03 0

-

Via孔的作用及原理分享!2019-09-30 0

-

Structure and Application pf WAV File2009-08-19 777

-

Via孔的作用及原理2009-10-15 1011

-

indirect FN via PM2009-12-22 838

-

pcb上的pad是什么?pcb的via是什么意思?pad及via的用法详解2020-07-24 52386

-

如何区分高速信号和低速信号2022-12-12 7600

-

SystemVerilog中的Packed Structure2022-11-07 2313

-

博文 | USB 4 高速信号布局关键因子 (三 ) : Via Stub2022-09-22 1445

-

Via孔的作用及原理.zip2023-03-01 297

-

BB Via和Micro Via有什么区别2025-01-03 218

全部0条评论

快来发表一下你的评论吧 !