AD8344 400MHz至1.2GHz有源接收混频器技术手册

描述

概述

AD8344是一款高度集成的SiGe有源滤波器,专门针对接收路径下变频进行了优化。该器件的输入范围为400 MHz至1.2 GHz,适合CDMA、GSM和TETRA基础设施设备等众多应用。

AD8344在RF和LO输入端口上均提供一个单端50 Ω输入阻抗。集成的LO驱动器提供LO驱动电平,典型值为0 dBm。

通过与EXRB引脚相连的一个外部偏置电阻,可以优化AD8344的功耗与线性度。AD8344采用+5 V单电源供电,功耗仅为84 mA,省电模式下为500 µA。

AD8344采用高性能SiGe工艺制造,提供节省空间的3 mm x 3 mm、16引脚LFCSP封装,额定温度范围为-40°C至+85°C。

数据表:*附件:AD8344 400MHz至1.2GHz有源接收混频器技术手册.pdf

特性

- RF频率范围:400 MHz至1.2 GHz

- IF频率范围:70 MHz至400 MHz

- 集成的LO驱动器要求0 dBm

- 输入三阶交调截点(IP3):+24dBm

- 输入压缩点(P1dB):+8.5 dBm

- 转换增益:+4.5 dB

- 噪声系数:10.5dB

- 5 V单电源供电,具有省电模式

- 3mm x 3mm、小型LFCSP封装

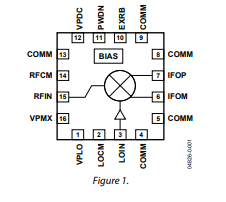

框图

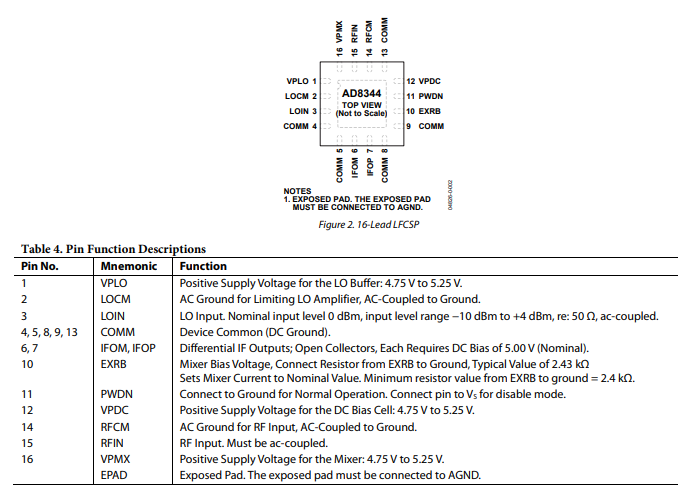

引脚配置描述

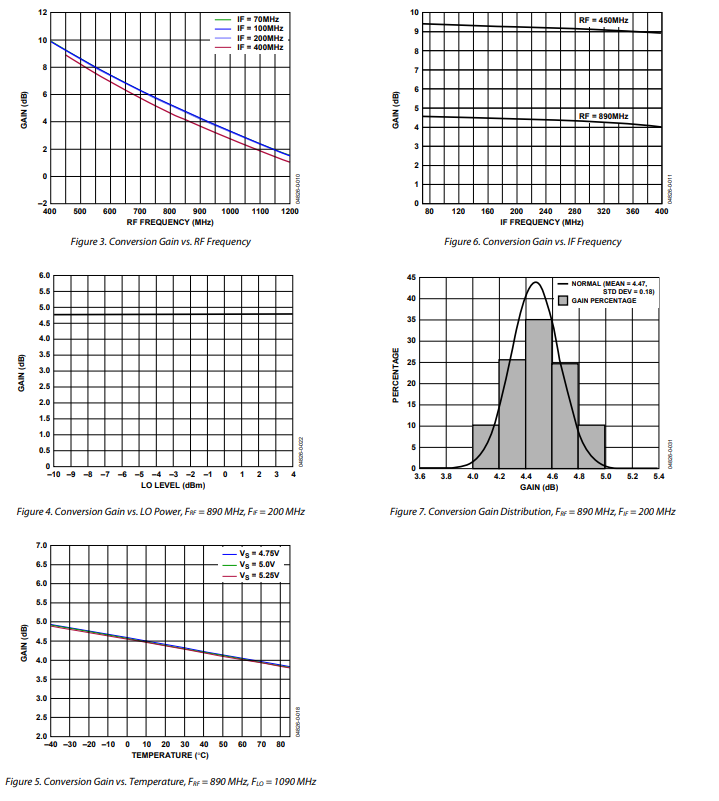

典型性能特征

电路描述

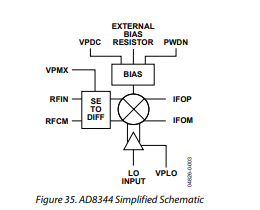

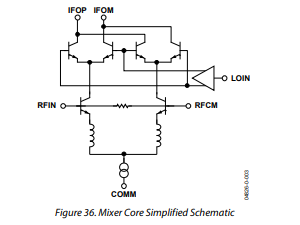

AD8344 是一款下变频混频器,针对 400MHz 至 1.2GHz 的输入频率范围进行了优化。它具有单端 50Ω 射频输入,以及单端 50Ω 本地振荡器(LO)输入。中频输出为差分集电极开路输出。可通过外部电阻的值来调节混频器的最大电流,以优化增益、压缩和互调性能,或用于低功率操作。图 35 展示了混频器的基本模块,包括本振缓冲器、射频电压 - 电流转换器、偏置单元和混频核心。

射频电压到射频电流的转换是通过电感退化差分对实现的。当差分对的一侧交流接地时,另一侧可进行单端驱动。射频输入也可以差分驱动。电压到电流转换器驱动四晶体管开关核心的发射极,该开关核心由放大的本振信号驱动。本地振荡器信号连接到本振输入。

本振输入与外部本振信号之间有三个限幅增益级。第一级将单端本振驱动转换为平衡的差分驱动。差分驱动信号通过另外两个增益级,这确保了在限制信号驱动的同时,仍能保持出色的动态范围和转换性能。这三个本振增益级的输出以本地振荡器频率的速率驱动混频核心内的四个晶体管。混频核心的输出直接取自其集电极开路端。集电极开路输出对中频呈现高阻抗。转换增益直接取决于呈现给这些开路集电极的阻抗。在特性描述中,通过 4:1 阻抗变压器向器件提供 200Ω 负载。

AD8344 还具备掉电功能。在 PWDWN 引脚施加逻辑低电平可使 AD8344 进入掉电模式。PWDWN 引脚置高电平时,器件恢复正常工作。掉电时的功耗低于 10mW。

混频器的偏置由来自 EXRB 引脚的外部电阻设置。该电阻的值直接影响混频器核心的动态范围。此外部电阻绝不能低于 2.4kΩ。若使用低于 2.4kΩ 的电阻,可能会对器件造成永久性损坏。

如图 36 所示,中频输出引脚 IFOP 和 IFOM 直接连接到混频核心中 NPN 晶体管的集电极开路端,因此差分和单端阻抗相对较高,约为几 kΩ。为使 AD8344 混频器核心正常工作,需要在电源电压与这些输出引脚之间进行连接。

AD8344 有三个电源电压引脚:VPDC、VPMX 和 VPLO。这些引脚相互隔离,以尽量减少或消除可能导致杂散信号或降低互端口隔离的寄生耦合路径。因此,这些引脚中的每一个都必须良好旁路,并尽可能靠近 AD8344 进行去耦。

-

MAX2681 400MHz至2.5GHz、低噪声、SiGe下变频混频器技术手册2025-04-01 1374

-

MAX9984 SiGe、高线性度、400MHz至1000MHz下变频混频器技术手册2025-03-31 1256

-

DC910A LT5557EUF | 400MHz至3.8GHz向下混频器, 1.95GHz RF, 240MHz 分立匹配IF2021-05-28 702

-

LTC5577:300 MHz至6 GHz高信号电平有源下变频混频器产品手册2021-05-26 807

-

AD8342:有源接收混频器LF至3 GHz数据表2021-04-21 877

-

AD8344:有源接收混频器,400 MHz至1.2 GHz数据表2021-04-18 770

-

LTC5510:1 MHz至6 GHz宽带高线性度有源混频器数据表2021-04-17 896

-

LT5527: 400MHz 至 3.7GHz、5V 高信号电平下变频混频器 数据手册2021-03-22 867

-

高动态范围有源上变频混频器支持 400MHz 至 2.7GHz 所有 LTE / 蜂窝频段2021-03-21 737

-

LT5557: 400MHz 至 3.8GHz、3.3V 有源下变频混频器 数据手册2021-03-19 839

-

DC1983A,使用LTC5510,1 MHz至6 GHz宽带高线性有源混频器的演示板2019-09-17 2186

-

AD8344 400 MHz 至1.2 GHz 有源接收混频器2019-02-22 653

全部0条评论

快来发表一下你的评论吧 !