LT5527 400MHz 至 3.7GHz、5V高信号电平下变频混频器技术手册

描述

概述

LT5527 有源混频器专为高线性度、宽动态范围下变频器应用而优化。该 IC 包括一个用于驱动双平衡混频器的高速差分 LO 缓冲放大器。RF 和 LO 输入端上的宽带、集成变压器提供了单端 50Ω 接口。差分 IF 输出可提供至差分 IF 滤波器和放大器的便利连接,也可轻松地实现匹配以驱动 50Ω 单端负载 (采用或不采用外部变压器均可)。

RF 输入在 1.7GHz 至 3GHz 的频率范围内被内部匹配至 50Ω,而 LO 输入则在 1.2GHz 至 5GHz 范围内被内部匹配至 5GHz。利用简单的外部匹配处理即可轻松实现两个端口的频率范围扩展。IF 输出进行了部分匹配处理,并可用于高达 600MHz 的 IF 频率。

LT5527 的高集成度较大限度地减少了总体解决方案的成本、电路板占用空间和系统级偏差。

数据表:*附件:LT5527 400MHz 至 3.7GHz、5V高信号电平下变频混频器技术手册.pdf

应用

- 蜂窝、WCDMA、TD-SCDMA 和 UMTS 基础设施

- GSM900 / GSM1800 / GSM1900 基础设施

- 900MHz / 2.4GHz / 3.5GHz WLAN

- MMDS、WiMAX

- 高线性度下混频器应用

特性

- 50Ω 单端 RF 和 LO 端口

- 宽 RF 频率范围:400MHz 至 3.7GHz^*^

- 高输入 IP3:

- 在 900MHz 为 24.5dBm

- 在 1900MHz 为 23.5dBm

- 转换增益:

- 在 900MHz 为 3.2dB

- 在 1900MHz 为 2.3dB

- 集成 LO 缓冲器:低 LO 驱动电平

- 高 LO-RF 和 LO-IF 隔离度

- 低噪声系数:

- 在 900MHz 为 11.6dB

- 在 1900MHz 为 12.5dB

- 外部组件数目非常少

- 使能功能

- 4.5V 至 5.25V 电源电压范围

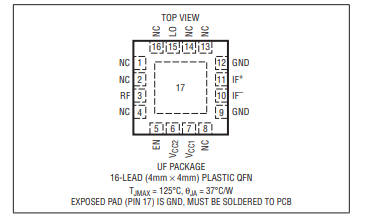

- 16 引脚 (4mm x 4mm) QFN 封装

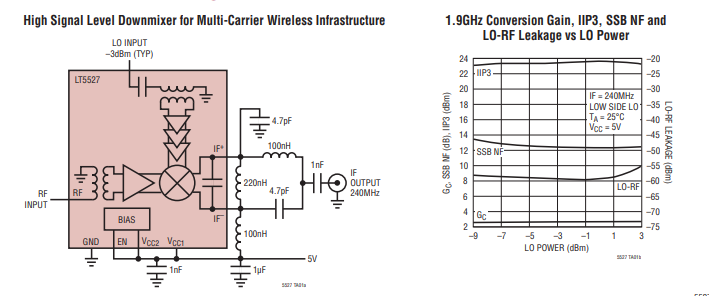

典型应用

引脚图

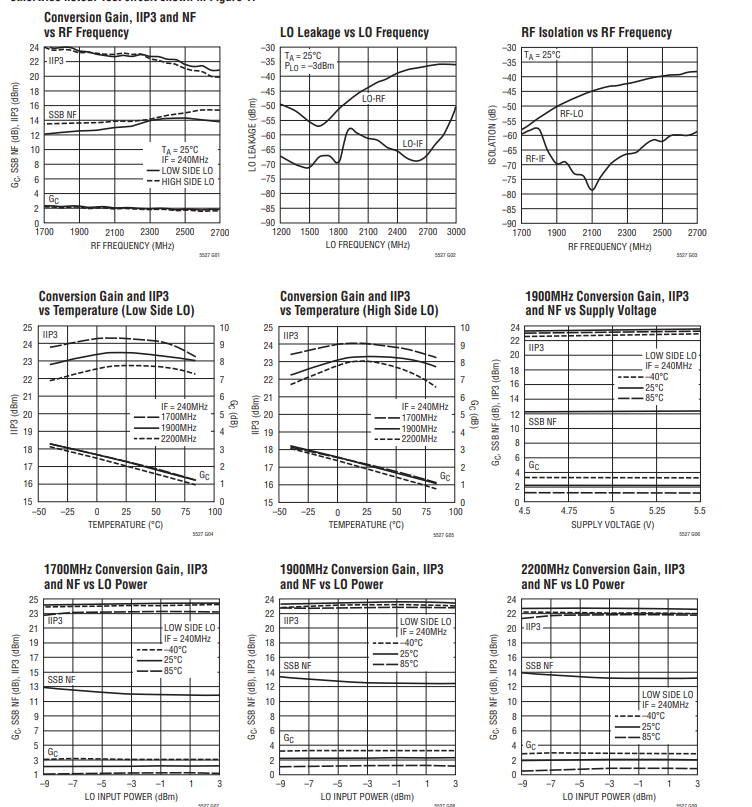

典型交流性能特征

引脚功能

- NC(引脚1、2、4、8、13、14、16) :内部未连接。为改善本振到射频以及本振到中频的隔离效果,这些引脚应在电路板上接地。

- RF(引脚3) :射频信号单端输入引脚。该引脚内部连接到射频输入变压器的初级侧,其直流电阻较低。若射频信号源未进行直流阻断,则必须使用串联隔直电容。射频输入在1.7GHz至3.3GHz范围内内部匹配。通过简单的外部匹配,可在低至400MHz或高达3700MHz的频率下工作。

- EN(引脚5) :使能引脚。当输入使能电压高于3V时,通过引脚6、7、10和11供电的混频器电路被使能。当输入电压低于0.3V时,所有电路均被禁用。典型输入电流在EN = 5V时为50μA,EN = 0V时为0μA。EN引脚不应悬空。在正常工作条件下,EN引脚电压应始终高于VCC至少0.3V,直至启动完成。

- VCC2(引脚6) :偏置电路电源引脚。典型电流消耗为2.8mA。该引脚应外部连接到VCC1引脚,并使用1000pF和1μF电容去耦。

- VCC1(引脚7) :本振缓冲器电路电源引脚。典型电流消耗为23.2mA。该引脚应外部连接到VCC2引脚,并使用1000pF和1μF电容去耦。

- GND(引脚9、12) :接地引脚。这些引脚内部连接到背面接地层,以改善隔离效果。它们应连接到电路板上的射频地,尽管并非旨在替代通过封装背面触点进行的主接地连接。

- IF - 、IF +(引脚10、11) :中频信号差分输出引脚。可能需要进行阻抗变换以匹配输出。这些引脚必须通过阻抗匹配电感、射频扼流圈或变压器中心抽头连接到VCC。

- LO(引脚15) :本地振荡器信号单端输入引脚。该引脚内部连接到本振变压器的初级侧,内部已进行直流阻断。不需要外部隔直电容。本振输入在1.2GHz至5GHz范围内内部匹配。通过简单的外部匹配,可在低至380MHz的频率下工作。

- 裸露焊盘(引脚17) :整个芯片的电路接地返回端。必须焊接到印刷电路板接地层。

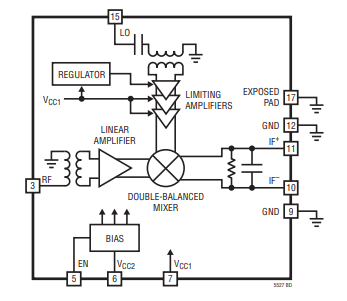

框图

应用信息

引言

LT5527 由一个高线性度双平衡混频器、射频缓冲放大器、高速限幅本振缓冲放大器和偏置使能电路组成。本振注入可使用低边或高边本振信号。中频输出为差分信号。

有两种评估电路可供选择。图 1 所示的标准评估电路采用基于变压器的匹配方式,适用于需要最低本振泄漏和最宽带宽的应用。图 2 所示的第二种评估电路用分立中频巴伦取代了变压器,可降低解决方案的成本和尺寸。分立中频巴伦可提供相当的噪声系数和更高的变频增益,但会导致本振 - 中频泄漏变差以及中频带宽减小。

射频输入端口

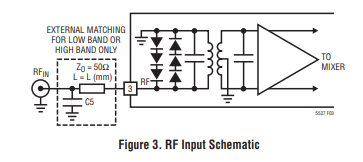

如图 3 所示,混频器的射频输入由一个集成变压器和一个高线性度差分放大器组成。变压器的初级端连接到射频输入引脚(引脚 3)和地。次级端内部连接到放大器的差分输入端。

变压器初级端在内部接地。如果射频源存在直流电压,则必须在射频输入引脚处使用隔直电容。

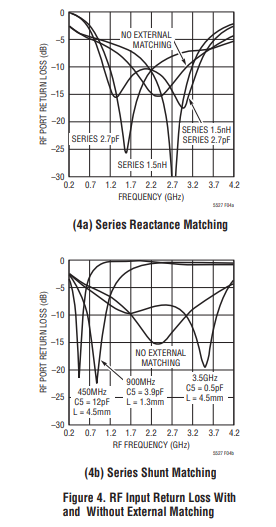

射频输入在 1.7GHz 至 3GHz 范围内内部匹配,在此频率范围内无需外部元件。图 4a 所示的回波损耗,典型值为 10dB。在低端,通过引脚 3 处的 2.7pF 串联电容可将 1.7GHz 回波损耗优化至大于 20dB。同样,2.7GHz 匹配也可得到改善。例如,通过 1.5nH 串联电感可将其提升至大于 30dB。1.5nH/2.7pF 网络可同时优化射频输入的低端和高端,并扩展射频输入带宽至 1.1GHz - 3.3GHz。这三种情况下测量得到的射频输入回波损耗也绘制在图 4a 中。

或者,也可通过添加并联电容(C5 = 12pF,位于评估板上引脚 3 上方 4.5mm 处的 50Ω 输入传输线上)将输入匹配向下移动,低至 450MHz 或向上移动至 3700MHz。450MHz 输入匹配需 C5 = 3.9pF,位于 1.3mm 处。3500MHz 输入匹配则需 C5 = 0.5pF,位于 4.5mm 处。

串联传输线/并联电容匹配拓扑结构使 LT5527 无需修改电路板布局,即可用于多种频率标准。串联传输线可用串联芯片电感替代,以实现更紧凑的布局。

这三种情况(450MHz、900MHz 和 3500MHz)的输入回波损耗绘制于图 4b。为作比较,图 4b 中还绘制了无外部匹配时的输入回波损耗。

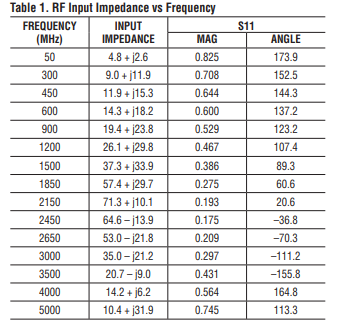

射频输入阻抗以及 S11 与频率的关系(含外部匹配)列于表 1,以引脚 3 为参考。S11 数据可用于微波电路仿真器,以设计定制匹配网络,并模拟电路板级对射频输入滤波器的影响。

本振输入端口

如图 5 所示,混频器的本振输入由一个集成变压器和高速限幅差分放大器组成。这些放大器旨在精确驱动混频器,以实现最高线性度和最低噪声系数。内部隔直电容与变压器初级端相连,无需外部隔直电容。

本振输入在 1.2GHz 至 5GHz 范围内内部匹配,不过由于内部放大器的限制,最大可用频率为 3.5GHz。输入匹配可通过单个并联电容(C4)向下移动,最低可达 750MHz。

本振输入在 750MHz 以下的匹配需要图 5 所示的串联电感(L4)/并联电容网络。图 6 绘制了两个示例,其中 L4 = 3.9nH/C4 = 5.6pF 可实现 650MHz 至 830MHz 的匹配,L4 = 6.8nH/C4 = 10pF 可实现 540MHz 至 640MHz 的匹配。

评估板上未设置 L4 的焊盘,因此电路跟踪需要在引脚 15 附近切割,以便插入 L4。低成本多层芯片电感足以满足 L4 的需求。

对于 1.2GHz 以上的本振频率,最佳本振驱动为 -3dBm,尽管放大器设计用于适应输入功率的几个 dB 变化,而不会导致混频器性能显著变化。在 1.2GHz 以下

-

MAX2681 400MHz至2.5GHz、低噪声、SiGe下变频混频器技术手册2025-04-01 1385

-

MAX2680 400MHz至2.5GHz、低噪声、SiGe下变频混频器技术手册2025-03-31 1304

-

DC795A LT5527EUF | 高线性度下变频混频器, V = 4.5V 至 5.25V2021-05-29 1008

-

DC910A LT5557EUF | 400MHz至3.8GHz向下混频器, 1.95GHz RF, 240MHz 分立匹配IF2021-05-28 703

-

LTC5577:300 MHz至6 GHz高信号电平有源下变频混频器产品手册2021-05-26 810

-

单双和三平衡混频器LT5527相关资料下载2021-04-15 887

-

LT5527: 400MHz 至 3.7GHz、5V 高信号电平下变频混频器 数据手册2021-03-22 872

-

LT5557: 400MHz 至 3.8GHz、3.3V 有源下变频混频器 数据手册2021-03-19 844

-

基于RF混频器的3G无线基站接收器应用2019-07-04 2459

-

LT5527 400MHz 至 3.7GHz、5V 高信号电平下变频混频器2019-02-22 439

-

LT5527型RF混频器在无线基站接收器中的应用2017-11-24 2359

-

LT5527混频器在无线基站接收器中的应用2010-12-06 758

全部0条评论

快来发表一下你的评论吧 !