LT5512 1kHz至3GHz高信号电平有源混频器技术手册

描述

概述

LT5512 是一款有源双平衡混频器 IC,专为高线性度 HF、VHF 和 UHF 应用而优化。 该 IC 包括一个用于驱动混频器的集成 LO 缓冲器放大器和一个用于改善 LO-RF 隔离度的 RF 缓冲器放大器。 内部偏置电路免除了增设精准外部电阻器的需要,并允许采用使能控制 (EN) 引脚来关断器件。

外部匹配的 RF 和 IF 端口使得混频器能够在非常低 (1MHz 以下) 或高达 3GHz 的频率条件下使用。 差分 LO 输入是专为单端或差分输入驱动而设计的。

LT5512 是无源二极管混频器的一种高线性度替代方案。 与具有转换损耗并需要高 LO 驱动电平的无源混频器不同,LT5512 提供了转换增益且所需的 LO 驱动电平低得多。

数据表:*附件:LT5512 1kHz至3GHz高信号电平有源混频器技术手册.pdf

应用

- HF/VHF/UHF 混频器

- 蜂窝/PCS/UMTS 基础设施

- 高线性度混频器应用

- ISM 频段接收机

- 无线医用遥测系统 (WMTS)

特性

- 宽带 RF、LO 和 IF 操作

- 高输入 IP3:

20dBm (30MHz 至 900MHz)

- +17dBm (在 1900MHz)

- 典型转换增益:1dB

- SSB 噪声指数:

- 11dB (在 900MHz)

- 14dB (在 1900MHz)

- 集成 LO 缓冲器:不易受 LO 驱动电平的影响

- 单端或差分 LO 驱动

- 高 LO-RF 隔离度

- 使能功能

- 4.5V 至 5.25V 电源电压范围

- 4mm × 4mm QFN 封装

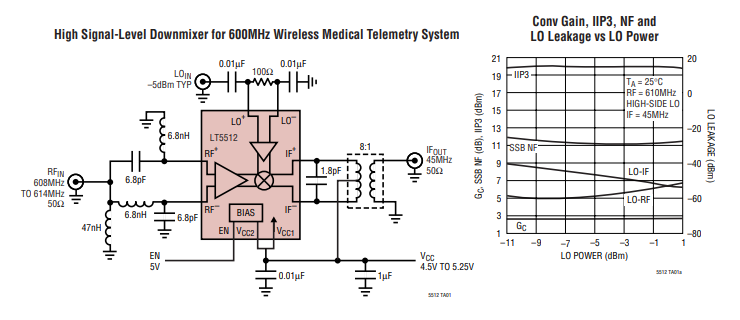

典型应用

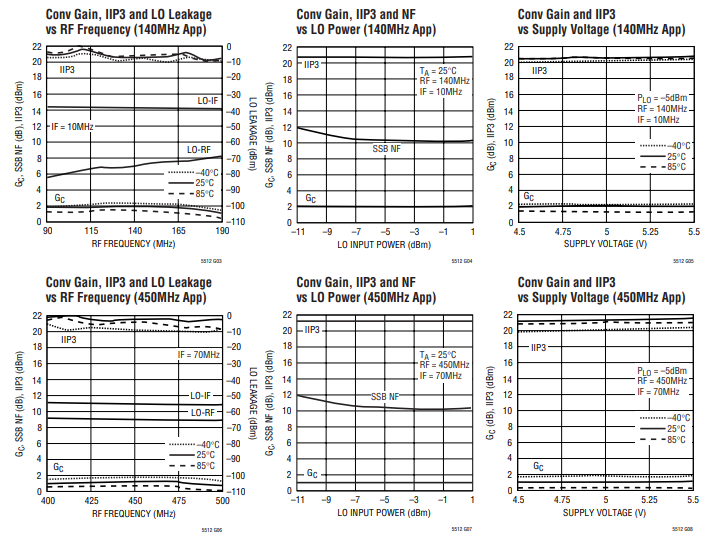

典型交流性能特征

引脚功能

- NC(引脚1、4、8、13、16) :内部未连接。为改善本振到射频以及本振到中频的隔离效果,这些引脚应在电路板上接地。

- RF + 、RF -(引脚2、3) :射频信号差分输入引脚。需用差分信号驱动这些引脚。每个引脚必须连接到能吸收15mA直流偏置电流(总共30mA)的直流地,可通过巴伦的中心抽头或并联电感实现。需要进行阻抗变换,使射频输入匹配50Ω(或75Ω)。

- EN(引脚5) :使能引脚。当输入电压高于3V时,通过引脚6、7、10和11供电的混频器电路被启用。当输入电压低于0.3V时,所有电路均被禁用。使能引脚典型输入电流在EN = 5V时为50μA ,EN = 0V时为0μA。

- VCC1(引脚6) :本振缓冲器电路电源引脚。典型电流消耗为22mA。该引脚应与其他VCC引脚外部相连,并用0.01μF和1μF电容去耦。

- VCC2(引脚7) :偏置电路电源引脚。典型电流消耗为4mA。该引脚应与其他VCC引脚外部相连,并用0.01μF和1μF电容去耦。

- GND(引脚9、12) :接地引脚。这些引脚内部连接到背面接地层,以增强隔离效果。它们应连接到电路板上的射频地,尽管并非用于替代通过封装背面触点进行的主接地连接。

- IF - 、IF +(引脚10、11) :中频信号差分输出引脚。可能需进行阻抗变换以匹配输出。这些引脚必须通过阻抗匹配电感、射频扼流圈或变压器中心抽头连接到VCC。

- LO - 、LO +(引脚14、15) :本地振荡器信号差分输入引脚。也可通过将其中一个引脚经隔直电容连接到射频地,进行单端驱动。这些引脚内部偏置为2V,因此需要隔直电容。需要进行阻抗变换或使用电阻,使本振输入匹配50Ω(或75Ω)。

- GROUND(引脚17,背面触点) :整个芯片的电路接地端。必须焊接到印刷电路板接地层。

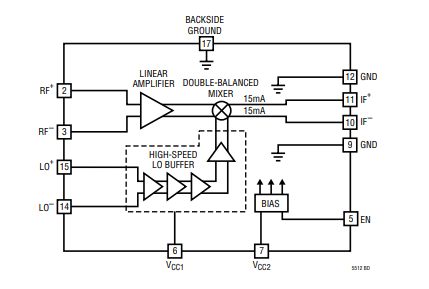

框图

应用信息

LT5512 由双平衡混频器、射频缓冲放大器、高速限幅本振缓冲器以及偏置/使能电路组成。其差分射频、本振和中频端口需外部匹配,这使得混频器可在低至 1MHz 以下或高达 3GHz 的频率下工作。既可用低边本振注入,也可用高边本振注入。

有两种评估电路可供选择。图 1 所示为高频/甚高频/超高频评估电路,图 2 所示为 900MHz 至 2.5GHz 评估电路。相应的演示板布局分别如图 10 和图 11 所示。

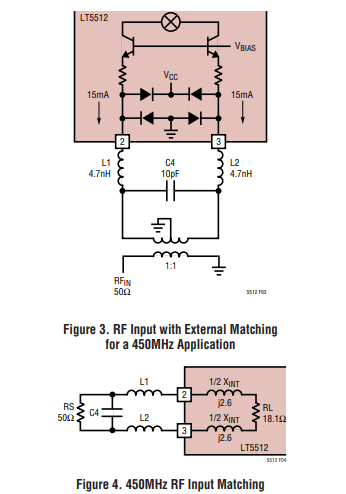

射频输入端口

图 3 展示了差分射频输入的简化原理图,以及 450MHz 应用的相关外部阻抗匹配元件。每个射频输入都需要一个低电阻直流接地回路,能够吸收 15mA 电流。这可通过图 3 所示巴伦的中心抽头实现,或者当射频输入信号从引脚 2 和 3 接地时,使用偏置扼流圈实现。偏置扼流圈的阻抗应足够高,以避免在感兴趣的频率下降低阻抗。

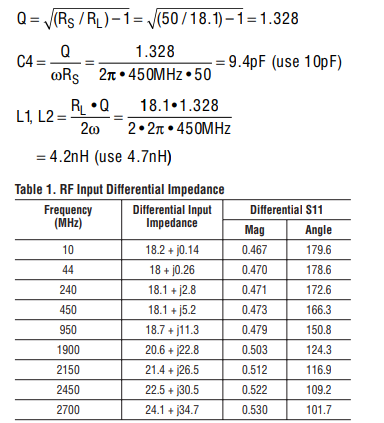

表 1 列出了多个常见射频频率下引脚 2 和 3 之间的差分输入阻抗和差分反射系数。如图 3 和图 4 所示,低通阻抗匹配用于将差分输入阻抗转换为巴伦输入所需的值。以下示例展示了如何为射频输入设计低通阻抗变换网络。

根据表 1,450MHz 时的差分输入阻抗为 (18.1 + j5.2) 。如图 4 所示,5.2Ω 电抗在 18.1Ω 负载电阻两侧各分一半。匹配网络将由与内部电感串联的额外电感,以及与所需 50Ω 源阻抗并联的电容组成。电容(C4)和电感的计算方式如下:

在高频(高于900MHz)情况下,采用相同的匹配技术,但在计算外部电感时,考虑芯片的输入电抗非常重要。如图2所示,高频评估板采用短(2mm)72Ω微带线来实现所需电感,而非使用贴片电感。

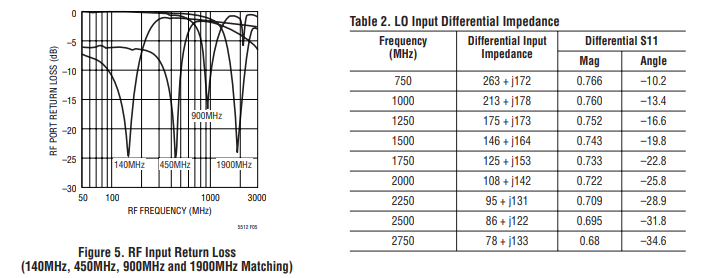

图1和图2展示了45MHz至2.45GHz多个频率的外部匹配参数值。图5绘制了实测射频输入回波损耗。

本振输入端口

本振缓冲放大器由高速限幅差分放大器组成,旨在高线性度驱动混频器四对管。LO + 和LO - 引脚设计用于差分或单端驱动。两个本振引脚内部均偏置为2V直流。

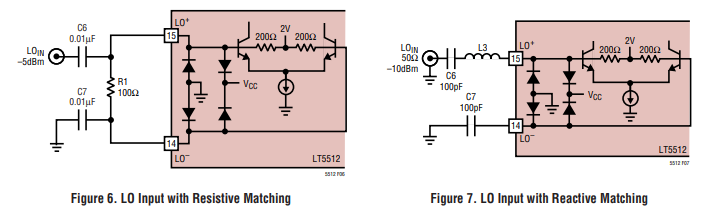

图6展示了本振输入的简化原理图,包含简单电阻性匹配和隔直电容。这是1.5GHz以下本振频率的首选匹配方式。内部(直流)电阻为400Ω。所需驱动电平为150mVrms(典型值),可由50Ω源或更高阻抗源(如PECL)提供。需外部匹配电阻来降低芯片处信号幅度,尽管输入级可承受10dB过载而不显著降低性能。低频评估板上采用电阻性本振端口匹配(见图1)。

在1.5GHz以上,内部电容影响显著,首选使用单个串联电感和隔直电容进行电抗匹配,使输入匹配至50Ω。图7展示了原理图。表2列出了多个频率下的差分输入阻抗和差分反射系数。

-

LT5579 1.5GHz至3.8GHz高线性度上变频混频器技术手册2025-03-31 1274

-

LTC5576 3GHz至8GHz高线性度有源上变频混频器技术手册2025-03-28 1484

-

LTC5553 3GHz至20GHz微波混频器技术手册2025-03-27 1672

-

DC503A LT5512EUF | 高信号电平、下变频混频器(宽IF输出,CATV应用)2021-06-18 840

-

LTC5577:300 MHz至6 GHz高信号电平有源下变频混频器产品手册2021-05-26 804

-

AD8342:有源接收混频器LF至3 GHz数据表2021-04-21 877

-

LTC5510:1 MHz至6 GHz宽带高线性度有源混频器数据表2021-04-17 896

-

单双和三平衡混频器LT5512电子资料2021-04-12 1251

-

LT5511: 高信号电平上变频混频器 数据手册2021-03-22 1206

-

DC1983A,使用LTC5510,1 MHz至6 GHz宽带高线性有源混频器的演示板2019-09-17 2186

-

LT5512 1kHz 至 3GHz 高信号电平有源混频器2019-02-22 640

全部0条评论

快来发表一下你的评论吧 !