晶体管栅极多晶硅掺杂的原理和必要性

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了多晶硅作为晶体管的栅极掺杂的原理和必要性。

晶体管栅极需要多晶硅

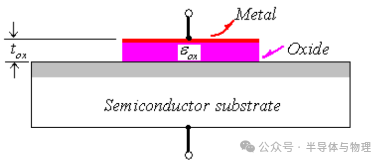

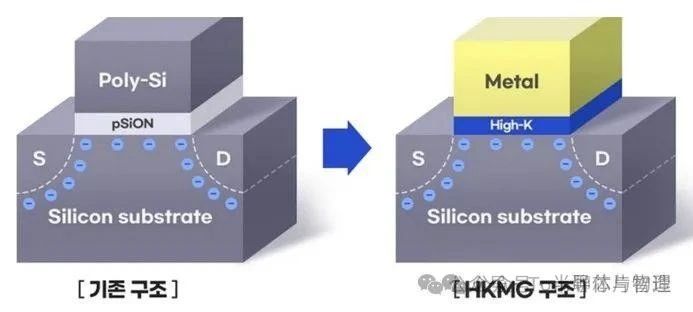

在早期金属-氧化物-半导体场效应晶体管(MOSFET)中,栅极材料曾使用金属(如铝),但随着芯片制程微缩,多晶硅(Poly-Si)逐渐成为主流选择,其核心优势在于:

工艺兼容性

多晶硅可在高温工艺(如氧化、退火)中保持稳定,与二氧化硅(SiO₂)栅介质层形成完美界面,避免金属扩散污染。

阈值电压可调性

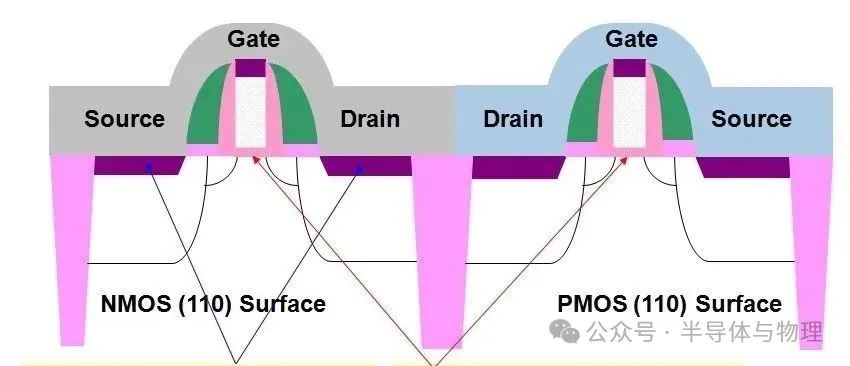

通过掺杂(N型或P型),可精确调控多晶硅的功函数,匹配NMOS/PMOS的阈值电压需求。

自对准工艺

多晶硅可作为掩膜直接参与源漏离子注入,实现栅极与沟道的自对准,避免光刻偏差。

为什么多晶硅栅极需要掺杂?

未掺杂的多晶硅本质上是半导体(电阻率约10⁵Ω·cm),无法有效导电。通过离子注入或原位掺杂引入杂质原子,可将其电阻率降低,满足栅极导电需求。更重要的是,掺杂类型(N型或P型)直接影响晶体管的阈值电压和性能。

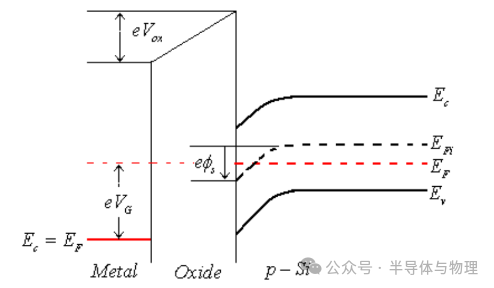

从功函数角度解释N型/P型掺杂的必要性

功函数(Work Function)是材料表面逸出电子所需的最小能量,决定了栅极与半导体沟道之间的能带对齐方式。多晶硅的功函数可通过掺杂调节,以匹配NMOS和PMOS的不同需求。

1.NMOS晶体管(沟道为P型硅)

目标:当栅极施加正电压时,吸引衬底电子在沟道形成反型层(N型),开启晶体管。

掺杂选择:使用N型多晶硅(掺磷或砷),其功函数较低(~4.1eV),与P型硅的价带(~5.0eV)形成较小势垒,降低阈值电压(Vth)。

物理机制:N型多晶硅的费米能级靠近导带,施加正偏压时更容易弯曲能带,触发强反型。

2.PMOS晶体管(沟道为N型硅)

目标:当栅极施加负电压时,吸引排斥沟道电子形成空穴反型层(P型),开启晶体管。

掺杂选择:使用P型多晶硅(掺硼),其功函数较高(~5.2eV),与N型硅的导带(~4.0eV)形成较大势垒,确保PMOS的正常开启。

物理机制:P型多晶硅的费米能级靠近价带,负偏压下能带弯曲更显著,促进空穴积累。

从载流子浓度角度解析掺杂影响

多晶硅的导电性直接由其载流子浓度决定,而载流子浓度由掺杂水平控制:

1.N型多晶硅(NMOS栅极)

掺杂元素:磷(P)或砷(As),浓度约10²⁰cm⁻³。

载流子:自由电子浓度高(~10²⁰cm⁻³),电阻率低(~10⁻⁴Ω·cm)。

作用:确保栅极低电阻,快速响应电压变化;高电子浓度增强栅极对沟道的电场控制。

2.P型多晶硅(PMOS栅极)

掺杂元素:硼(B),浓度约10²⁰cm⁻³。

载流子:空穴浓度高(~10²⁰cm⁻³),电阻率与N型相当。

作用:维持栅极导电性,同时通过空穴补偿沟道区的电子,避免寄生导通。

-

为什么采用多晶硅作为栅极材料2025-02-08 1648

-

多晶硅栅工艺的制造流程2024-11-07 3152

-

多晶硅内掺杂物的扩散效应2023-06-11 2747

-

单晶圆系统的多晶硅沉积方法2022-09-30 2344

-

多晶硅是什么东西_多晶硅属于什么行业2021-02-24 19536

-

FZ多晶硅24吨2020-01-20 1320

-

低温多晶硅的工作原理是什么?2019-09-18 3249

-

多晶硅用途2019-04-11 41078

-

多晶硅上市公司有哪些_国内多晶硅上市公司排名2017-12-18 67295

-

低温多晶硅,低温多晶硅是什么意思2010-03-27 1105

-

多晶硅发射极晶体管,多晶硅发射极晶体管是什么意思2010-03-05 2018

-

什么是多晶硅2009-04-08 3001

-

单晶硅与多晶硅的区别2009-03-04 5015

全部0条评论

快来发表一下你的评论吧 !