一文详解AXI DMA技术

描述

DMA技术

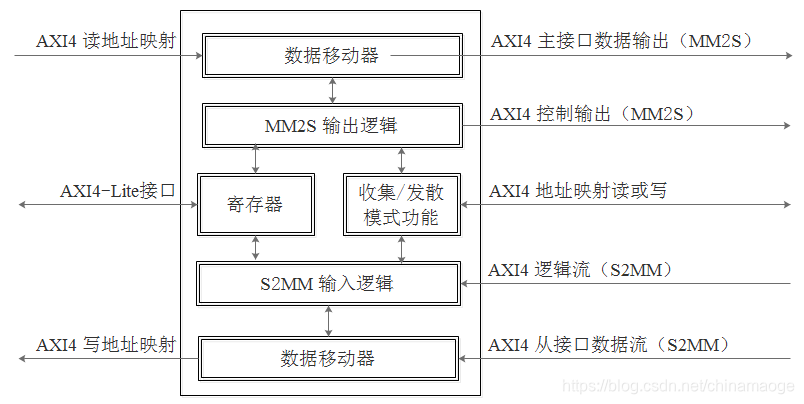

AXI直接数值存取(Drect Memory Access,DMA)IP核在AXI4内存映射和AXI4流IP接口之间提供高带宽的直接内存访问。DMA可以选择分散收集(Scatter Gather,SG)功能还可以将数据移动任务从位于于处理器系统中的中央处理器(CPU)中卸载出来。可以通过一个AXI4-Lite从接口访问初始化、状态和管理寄存器。如图4. 8展现了DMA IP的功能构成核心。

系统内存和传输的目标之间的主要通过高速DMA数据传输,数据之间的流向是AXI4读数据的主端口到AXI4内存映射流(Memory-Mapped To Stream,MM2S),和通过数据流到内存映射(Stream To Memory-Mapped,S2MM)从外设写入到内存中。AXI DMA还支持在分散/聚集模式下,MM2S和S2MM路径上最多16个多通道的数据传输[67]。

Fig4. 8 Core functions of AXI DMA

图4. 8 AXI DMA 核心功能

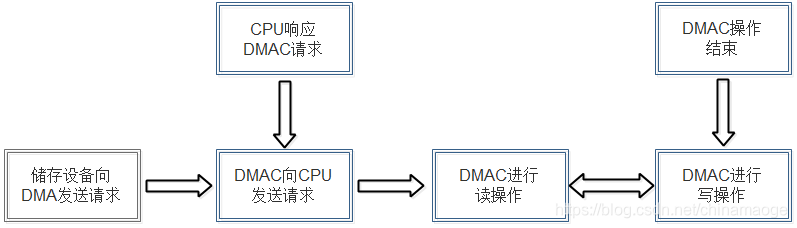

DMA传输数据是不需要CPU进行控制,而是有一个专门的DMA控制器来控制着存储器之间的数据传送或者外部设备与存储器之间的数据交换流程。DMA控制器使用64-bit的AXI主接口,操作以两倍的CPU的时钟速率执行系统内存和PL外围设备之间的DMA数据传输。软件通过控制器的32位APB从接口访问这些寄存器。DMA控制器的基本工作流程如图4. 9所示。

图4. 9 DMAC基本工作流程

Fig4. 9 DMAC basic workflow

源存储设备向DMAC发送任务请求,DMAC在接收到请求后向CPU发出接管总线的权限,CPU把总线控制权释放给DMAC并且开始传输数据,使用FIFO作为一个中介,分别在源端口和目标端口进行读写操作。当数据传输完毕之后产生完成中断信号给CPU,把总线控制权限交还给CPU。

分散/收集(SG)模式下DMA传输

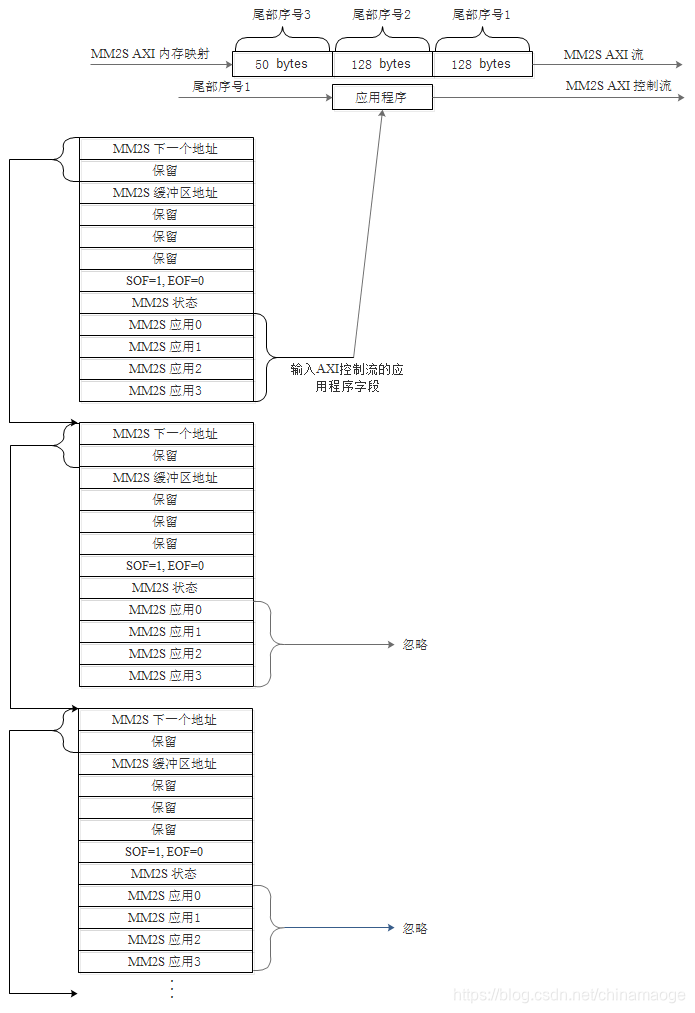

AXI DMA收集和发散模式下使用描述符进行控制数据传输,描述符由8个32-bit基本字和0或5个用户应用程序字组成。描述符将会支持64-bit地址和用户应用程序数据。每个数据帧的开头和结尾的标签都支持多个描述符。完成状态和完成时的中断状态也包括在内。

在开始DMA操作之前,软件应用程序必须设置一个描述符链表。AXI DMA通过获取、处理并更新处理描述符。通过分析描述符,软件应用程序可以读取相关DMA传输的状态,通过在接收(S2MM)通道上获取用户信息来确定传输完成。有了这些信息,软件应用程序可以管理描述符和数据缓冲区。

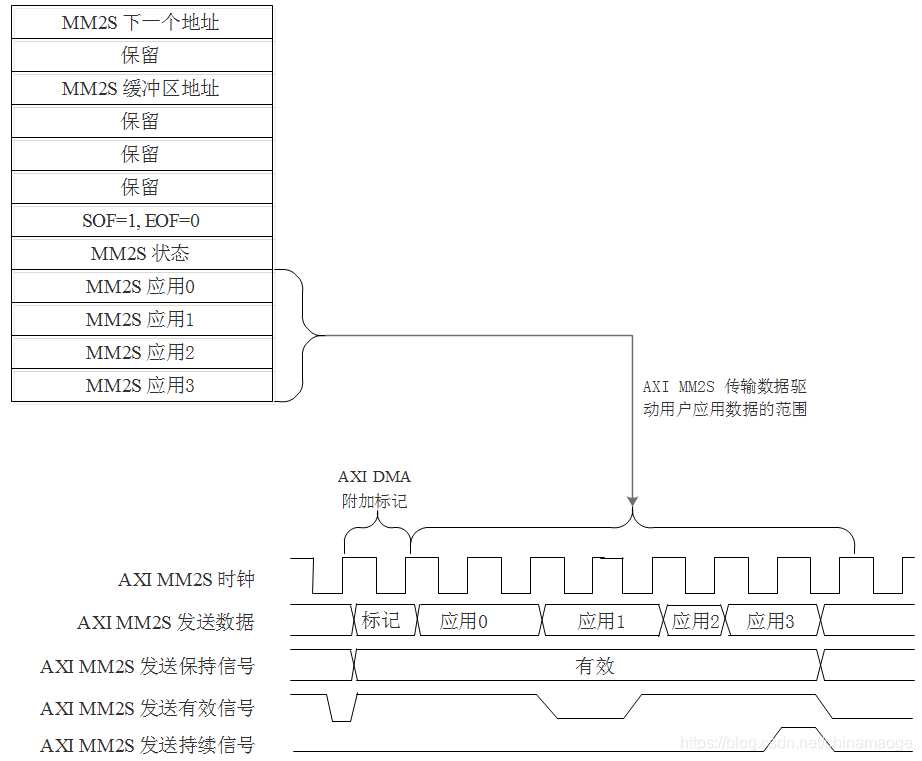

描述符SOF/EOF设置和AXI控制流之间的关系如图4. 10所示。SOF=1的描述符是数据包的开始,并为MM2S方向重置方向。图4. 11显示了描述符用户应用程序字段如何在AXI控制流上显示的示例。AXI DMA向目标设备插入一个标志来指示数据类型。

图4. 10描述符与MM2S流和控制流的关系

Fig4. 10 Detail of Descriptor Relationship to MM2S Stream and Control Stream

图4. 11 MM2S控制流的用户应用字段和时间

Fig4. 11 Example user application field / timing for MM2S control stream

表4.3 MM2S描述符表内容具体解释

Table 4.3 MM2S descriptor content specific explanation

| 地址空间偏移 | 名字 | 描述 |

|

00h 04h 08h 0Ch 10h 14h 18h 1Ch 20h 24h 28h 2Ch |

MM2S下一个地址 (地址)保留 MM2S缓冲区地址 (数据地址)保留 保留 保留 控制 状态 MM2S应用0 MM2S应用1 MM2S应用2 MM2S应用3 |

MM2S指向下一描述符表的地址 前面32-bit作为描述符表的地址保留 MM2S中指向传输数据的地址 前32-bit保留指向传输数据的地址 保留 保留 控制 状态 MM2S应用程序0 MM2S应用程序1 MM2S应用程序2 MM2S应用程序3 |

-

ZYNQ基础---AXI DMA使用2025-01-06 4317

-

AXI DMA详解与应用篇2023-08-10 11029

-

一文详解精密封装技术2022-12-30 2673

-

AXI接口协议详解2022-10-14 2959

-

一文详解DMA2022-10-12 15625

-

Petalinux加速axi-dma内核驱动缓冲区读过程2022-02-16 5520

-

一文详解MPSoC芯片2021-01-07 3253

-

ZYNQ SOC案例开发:AXI DMA使用解析及环路测试2020-12-31 11166

-

ZYNQ中DMA与AXI4总线2020-11-02 5364

-

你必须了解的AXI总线详解2020-10-09 9304

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7634

-

zynq linux AXI DMA传输步骤教程详解2018-07-08 32420

-

Adam Taylor玩转MicroZed系列68:AXI DMA Ⅲ,软件部分2017-02-08 611

-

AMBA_AXI总线详解2014-04-18 1859

全部0条评论

快来发表一下你的评论吧 !