CAN总线控制器设计及测试程序

控制/MCU

描述

在此利用VerilogHDL设计了一款CAN总线控制器,首先根据协议把整个CAN总线控制器划分为接口逻辑管理、寄存器逻辑和CAN核心模块3个模块,然后用Verilog HDL硬件描述语言设计了各个功能模块,并使用Modelsim软件对各个模块的功能进行了仿真,最后使用FPGA芯片对设计的CAN总线控制器验证,并连接了一个包含该FPGA CAN总线控制器的4节点CAN总线网络。测试结果表明所设计的CAN总线控制器能够完成设定的功能。

CAN(Controller Area Network)是由ISO定义的一种串行通信总线,它是一种能有效地支持高安全等级的分布实时控制的新一代网络通信协议,属于现场总线范畴。CAN最早被设计作为汽车环境中微控制器的通讯,在车载各电子控制装置与ECU之间交换信息,形成汽车电子控制网络,目前应用领域已经相当广泛。

近年来,支持CAN协议的芯片不断推出,给CAN总线用户带来了极大的方便。随着我国对现场总线技术需求的增加,CAN总线已经会成为我国最常用的现场总线之一。

基于CAN总线的ECU电子控制单元的开发,也是现在最热门的研究。现在对CAN总线芯片的研究已经不再局限于单一芯片的研究,而是把所有的功能芯片都集中在一块芯片上实现一个完整的ECU的功能。

本项目目的是利用FPGA实现一款支持CAN2.0协议的总线控制器,完成一个通用的能够满足CAN2.0协议的CAN总线控制器软IP核,这样可以在以后的应用中方便的集成到其他系统中去。本文使用VerilogHDL语言,设计了一款支持CAN2.0协议的CAN总线控制器,并利用FPGA芯片在CAN总线网络中对其进行了测试,实现了设计目的。创新点为CAN_Registers设计中寄存器模块、位流处理器的收发部分功能、测试程序、基于该FPGA的CAN总线控制器的节点电路等。

1 CAN总线控制器设计

1.1 CAN控制器设计流程

1.1.1 功能设计

首先对CAN2.0协议进行了深入的分析,掌握了CAN总线协议的各部分内容;而后参照和分析了几种典型的CAN总线控制器的功能;最后选择PHILPS公司生产的CAN总线控制器SJA1000进行进一步的分析,掌握了它的各部分模块的功能。在这些基础上根据需要规划了所设计的CAN总线控制器的功能。

1.1.2 设计描述和功能验证

功能设计完成后,依据功能并参照CAN总线2.0协议,将控制器划分为若干功能模块,明确了各个功能模块的作用。确定模块及其功能之后,用Verilog HDL语言实现了各模块的设计。接着,利用Modelsim对整个设计进行了功能验证。

1.1.3 逻辑综合

功能仿真通过以后,利用QUARTusⅡ对所设计的CAN总线控制器进行逻辑综合,并把其配置到FPGA中。

1.1.4 硬件验证

配置到FPGA中以后,用所设计的基于FPGA的CAN总线控制器作为一个节点,与采用SJA1000作为控制器的节点电路进行了通信测试,验证了所设计的CAN总线控制器的功能。

1.2 CAN总线控制器的整体设计

1.2.1 控制器SJA1000的功能结构

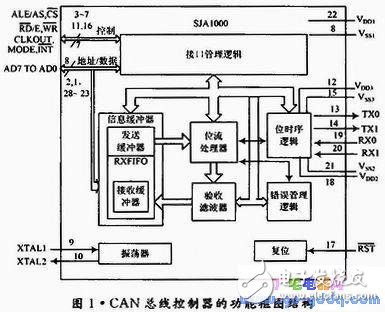

SJA1000是PHILIPS公司于1997年推出的一种独立CAN总线控制器,用于汽车和一般环境中的控制器局域网络。SJA1000主要由以下几个部分构成:接口管理逻辑、发送缓冲器、接收缓冲器、接收滤波器、位数据流处理器、位时序逻辑、错误管理逻。SJA1000是双列直插式集成电路,功能框图如图1所示。

1.2.2 本文中控制器的功能结构

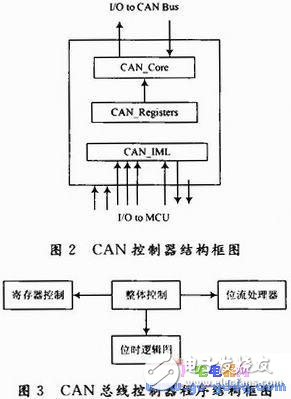

本文设计的CAN控制器参照SJA1000控制器的结构,功能基本框架包含如图2所示的3个功能模块。

CAN_IML是CAN总线控制器接口逻辑,主要功能是解释来自微处理器的命令,控制CAN寄存器的寻址,向微处理器提供中断信息和状态信息。

CAN_Core为CAN协议控制器的核心部分,完成CAN协议中的数据链路层的全部功能以及物理层的部分功能,包括LLC子层的接收滤波、超载通知和恢复管理、MAC子层的数据封装/拆装、帧编码、媒体访问管理、错误检测、错误标定、应答和串行化/解串行化、以及物理层的位编码/解码、位定时和同步。CAN_Registers为一寄存器组,外部微处理器可以通过地址直接访问这些寄存器。根据功能框图,设计了CAN总线控制器的程序结构,如图3所示。

1.3 CAN总线各个功能模块的设计

1.3.1 CAN_IML设计

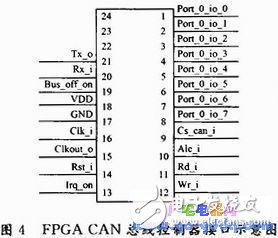

参照SJA1000,设计FPGA CAN总线控制器的接口,如图4所示。

图中Port_0_io_7到Port_0_io_0为地址/数据复合总线。Cs_can_i为片选输入信号。当Cs_can_i为0时允许访问CAN总线控制器。Ale_i为1时,允许对寄存器进行赋值。Rd_i和Wr_i为微处理器的读使能信号和写使能信号。IRQ_on为中断输出信号,用于中断微处理器。Rst_i为复位输入,用于复位CAN接口。Clkout_o为FPGA CAN控制器提供给微处理器的时钟输出信号,时钟分频寄存器可禁止该引脚输出。Bus_off_on控制总线关闭和总线开放接口,Tx_o和Rx_i与收发器相连,向总线发送和接收数据。

1.3.2 CAN_Registers设计

设计的CAN总线控制器的寄存器模块包括以下寄存器:模式寄存器、命令寄存器、状态寄存器、中断寄存器、中断使能寄存器、总线定时寄存器0~1、仲裁丢失捕获寄存器、错误代码捕获寄存器、错误报警限制寄存器、接收错误计数器、发送错误计数器、验收代码寄存器0~3、验收屏蔽寄存器0~3、接收信息计数器和接收/发送缓冲器。

1.3.3 CAN_Core设计

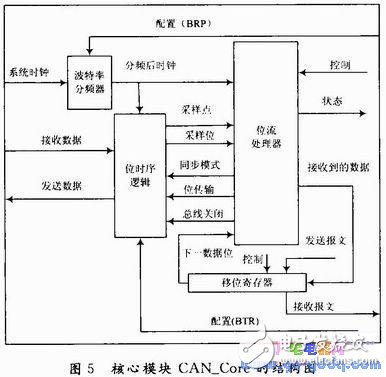

CAN_Core为整个CAN控制器的核心,负责处理CAN的协议。核心模块由4个部分组成,结构如图5所示。

下面简单介绍CAN_Core模块中的位流处理器、位时序逻辑。

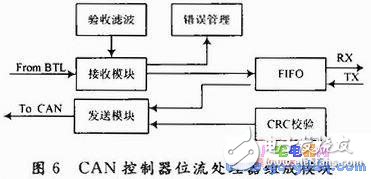

位流处理器是CAN总线控制器中控制数据流的发生器。它还执行总线上的错误检测、仲裁、填充和错误处理等功能。主要有接收模块、发送模块、错误管理模块、CRC校验、验收滤波、FIFO等6个模块组成,如图6所示。其中CRC校验、FIFO、验收滤波在所执行的项目中已经有他人设计完成。

位时序逻辑的设计包括位定时设计、采样点设计、位同步设计3部分。下面以定位时为例介绍其设计。

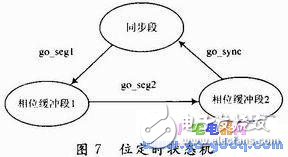

位定时设计 在位定时设计中采用了一个有3个状态的状态机。3个状态分别对应的是同步段和相位缓冲段1以及相位缓冲段2。传播段占用的时间短,在控制上没有特别的意义,仅作为物理层的传播延时,所以没有设计进状态机,位定时部分的状态机设计如图7所示。

接着使用ModelSim软件对所设计的各个模块和整个CAN总线控制器进行了功能仿真,仿真结果表明达到了设计目标。

2 测试验证

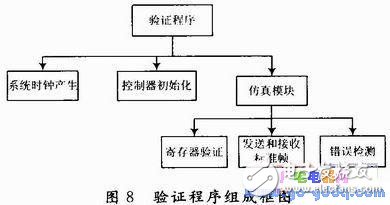

本文最后设计了CAN总线控制器的测试程序,其目的是模拟一块微处理器对CAN总线控制器进行读写操作,从而实现对CAN总线控制器的寄存器访问,完成总线收发功能。在该测试程序编写中,各个功能基本上以任务的形式实现,进行不同的仿真时只需调用相关的任务模块。图8为验证程序的组成框图。

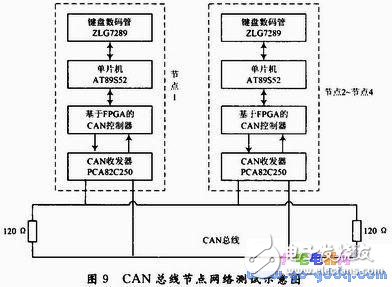

仿真验证完成以后将其HDL CAN总线程序下载到FPGA中进行测试,目标芯片采用Cyclone系列的EP1C6Q240C8,为了验证所设计的FPGA CAN总线控制器,还设计了一款基于该FPGA的CAN总线控制器的节点电路,然后利用所设计的节点电路与其他3个利用SJA1000作为控制器的CAN总线节点进行了通信测试。所有的节点使用AT89S52单片机作为节点微处理器,PCA82C250作为收发器,测试结果表明下载到FPGA中的控制器程序工作正常,实现了预计的CAN总线通讯功能。测试网络示意图如图9所示。

测试时,按动节点1上的开关并将该状态发送到节点2,在节点2上能显示对应的状态,反之也可。同时也可在节点2通过键盘输入某一代码,而在节点1上的数码管上显示相应的结果。该实验结果表明下载到FPGA中的控制器程序工作正常。

3 结语

本项目利用Verilog HDL语言设计了一款CAN总线控制器芯片,并使用ModelSire软件对所设计的CAN总线控制器进行了功能仿真;之后为了验证设计,还编制一个验证程序,并将验证之后的设计配置到了FPGA中;最后用所设计的基于FPGA的CAN总线控制器制作了CAN节点,并与其他采用SJA1000为控制器的CAN节点进行了通讯测试,实现了CAN总线良好的工作,验证了设计的正确性。

- 相关推荐

- 热点推荐

- can总线控制器

-

如何选择CAN总线控制器2024-11-12 1318

-

CAN总线控制器的工作原理2024-09-30 3057

-

用于Hercules微控制器的CAN总线引导加载程序2024-09-19 293

-

CAN总线控制器是什么意思2024-09-03 3220

-

基于FPGA的CAN总线控制器的设计2023-05-18 2329

-

CAN总线控制器程序的仿真与测试2022-07-28 2416

-

怎样去设计CAN总线控制器sJAl000驱动程序?计2021-04-27 1662

-

基于DSP_FPGA与CAN总线的跟踪控制器设计2017-10-21 841

-

CAN总线控制器SJA1000的初始化程序设计2016-05-06 879

-

基于Verilog HDL语言的CAN总线控制器设计及验证2012-07-31 8899

-

基于CAN总线的家庭控制器的设计与实现2009-11-07 897

-

以8051微控制器和82527独立CAN总线控制器为核心组成2009-07-17 634

-

基于CAN总线的客房通信控制器的设计2009-06-13 822

-

CAN总线控制器Verilog代码2008-05-20 1343

全部0条评论

快来发表一下你的评论吧 !