基于AD650单片式V/F变换器的接口设计

控制/MCU

描述

目前,A/D转换器随着速度及精度的提高,价格愈趋昂贵,给实际应用带来困难。但在某些场合被测信号的变化是缓慢的,这时转换速度就不成为主要问题。此时,可以采用低速的双积分式A/D芯片,如ICL7135(国产型号5G7135)是4又1/2位,分辨率为1/40 000,精度相当于14位二进制的A/D转换器;MC14433(国产型号5G14433)是3丢位,分辨率为5/10 000。5G7135与5G14433都采用双斜率工作方式,所以具有很高的抗工频干扰能力。但其转换速率较低,为2~10次/秒。如果转换速率要求在20次/秒以上或更高,则无现成的双积分A/D转换集成电路。从原理上讲可以用积分器、比较器、计数器构成速度较高的高精度A/D,但由于受器件性能的限制,如电压比较器的有限增益和有限转换速率等,实现起来比较困难。兼顾价格与转换精度的另一种有效方法是,采用V/F技术构成高精度的A/D转换器。近几年由于集成电路技术的发展,V/F芯片价格下降,技术指标进一步提高,特别是单片式的V/F芯片在各行业中得到广泛的应用。AD650是高精度型的单片式V/F变换器,它与单片机结合可以构成分辨率高、转换速率高于20次/秒的A/D转换器。

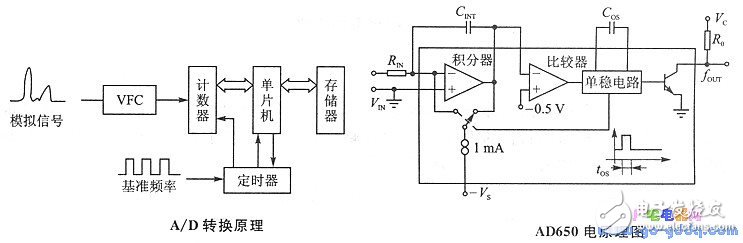

1.VFC与单片机的模/数转换的基本原理

如图1所示,转换前,单片机首先对计数器及定时器清零,预置计数及定时初值;随后通过定时控制端及计数控制端,使定时器及计数器同时开始工作;到一定时间后,定时器溢出端发出信号,单片机检测到该信号后,停止计数器工作,并把计数结果送入存储器中。这样便完成了一次模/数转换。VFC输出的矩形波的频率与其输入电压成线性关系,计数器的计数值等于VFC输出频率乘以定时器时间,而定时器时间可以通过单片机来精确控制。所以此种方法的转换精度主要取决于VFC的精度。

2.AD650与单片机接口的硬件设计

AD650是电荷平衡式单片V/F变换器,图2为其电原理图。

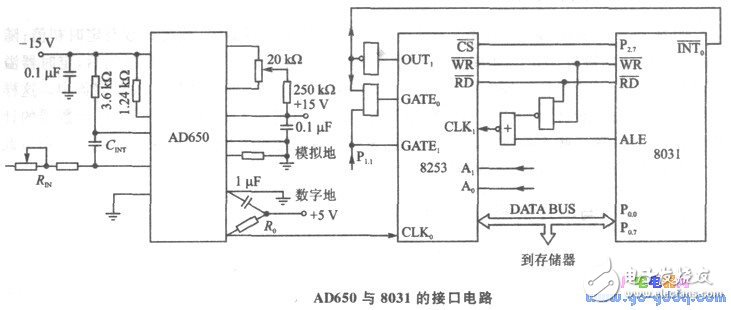

AD650的接线不很复杂,仅须选择4个元件的数值:输入电阻RIN、定时电容Cos、逻辑电阻Ro及积分电容CINT。下面介绍选取原则。

Ro:根据TTL逻辑电平,晶体管T在导通时约有0.4 V管压降。为保证有足够的负载能力,希望流过Ro的电流为8 mA。这样R。便近似为0.5 V/8 mA=62.5Ω,一般取1kΩ。如选1MHz为满量程频率,则必须采用500 Q左右的上拉电阻,以获得足够短的上升时间。

RIN与COs:这两个参数决定了满刻度频率及相适应的输入信号电压范围。RIN与Cos的关系是非线性的。满度频率为1 MHz、输入信号为0~10 V时,Cos可选51 pF,RIN为16.2 kΩ。

CINT:大多数情况下,CINT的最佳值按下式计算得出:

1 MHz时,CINT仍取1000 pF为宜。

模/数转换所用的定时器及计数器选用Intel公司生产的8253芯片来实现。它内部有三个独立的可预置数的16位递减计数器。每个计数器都有一个时钟输入端CN、一个门控输入端GN、一个输出端ON。时钟输入端用于输入时钟脉冲或事件计数脉冲,计数器的值在时钟脉冲的下降沿变化,门控端可以送入控制或复位信号。计数器减到零时,由输出端送出标志信号。

图3为接线图,AD650的输出接8253计数器O的CN端,计数器1作定时器用。8253的数据线与8031的BUS直接相连,Ai、Ao接8031的地址锁存器74LS373的输出。存储器的分配采用线选法,即8253片选端CS(反相)接8031的P2.7端。由此可知,计数器0的地址为7FFCH,计数器1的地址为7FFDH,计数器地址为7FFEH,方式控制寄存器端口为7FFFH。

3.软件设计

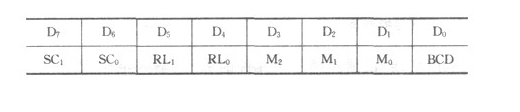

软件主要包括两部分:一部分是初始化程序;另一部分是取数程序。8031的初始化包括中断系统的初始化、堆栈指针的设置等,本文从略。8253在使用前须向其方式控制器写入方式控制字,控制字的格式如下表所列。

控制字的格式表

SC1、SCo组合选择计数器,同时为高电平时非法;RLi、RLo控制读出/装入方式.4种方式依次为:①计数器中的数据锁存到缓冲器,在此方式下可以进行“飞读”而不影响计数操作;

②选计数器的低8位字节;③选计数器的高8位字节;④对计数器分两次操作,先低8位字节,后高8位字节。M2、Mi、Mo选择计数器的工作方式,8253的每个计数器均有6种工作方式,包括定时计数方式、可编程单次脉冲方式、频率产生器方式、方波发生器方式、软件触发选通方式和硬件触发选通方式。BCD控制二进制计数或是二一十进制计数。

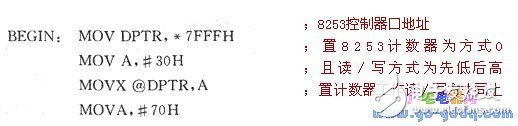

假设要求A/D精度为14位二进制,AD650选满刻度频率为500 kHz,则定时器定时值应为:214 /0.5×106= 32. 77 ms。

8031选用6 MHz晶振,经ALE、WR、RD逻辑组合产生的1 MHz的脉冲信号作为计数器1的时钟输入到CLK1端。因须定时32. 77 ms,所以计数器1的初值应预置为(16 384×2)10=8000H,工作于方式0,计数结束。OUTi翻转使计数器O停止工作,并申请中断或接受查询,将计数器O的计数结果取反后送入存储器待处理。取反的原因是8253采用减法计数方式。

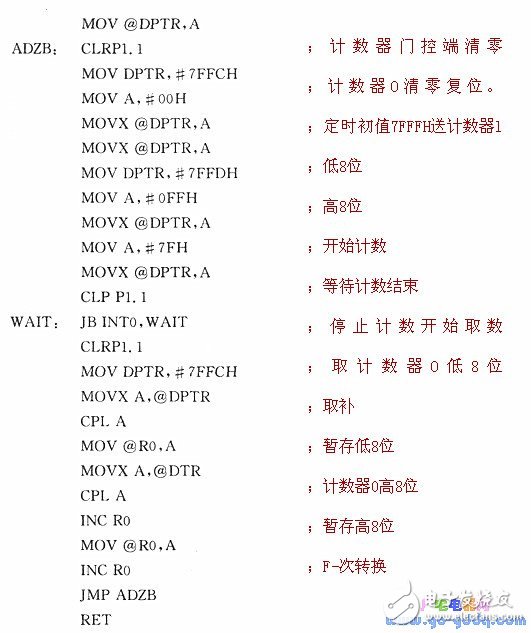

下面是8253初始化及取数子程序:

4.几点说明

①V/F芯片AD650具有精度高,温度特性好,线性度高等优点,它与单片机的接口也较简单,编程方便。外接定时电容Cos,可控制输出满度频率为10 kHz、100 kHz、500 kHz、1 MHz四档,为电路设计提供很大方便。由本模/数转换器的工作原理可知:一定的模入电压,其转换结果的位数随计数时间而增加,因此用户可按要求在16位内自己编程选择模/数结果的位数。当满度频率为500 kHz时,分辨率为12~16位的定时时间分别为:8. 19 ms、16. 38 ms、32. 76 ms、65. 52 ms、131. 04 ms。此时,本A/D转换速度比一般双积分A/D转换要高5倍以上。

②本A/D转换器具有较强的噪声抑制能力。因为计数值等于待转换电压对计数时间的积分,所以转换结果(即计数值)是计数时间内待转换电压的平均值。这样,大的尖峰脉冲干扰就被平均掉,不会出现很大误差。

另外,若选计数时间为工频周期的整数倍.则可有效地抑制串模工频干扰。从理论上讲,若计数时间是待转换电压中噪声信号周期的整数倍,则其抑制能力是无限的。计数时间是由软件控制的,可十分方便地按抑制最严重的周期性噪声确定。

③当AD650满度输出频率为1 MHz时,须采取一些特殊措施,如将模拟地与数字地隔离,增加去耦电路,对偏置电压进行自动调整等。

-

用于AC/DC变换器应用的新型650V GaNFast半桥IC2023-06-19 20340

-

AN-279:使用AD650电压/频率转换器作为频率/电压转换器2021-04-24 1577

-

承受650V电压的实现低功耗的PWM型AC/DC变换器2020-06-05 2269

-

Boost-Buck光伏接口变换器控制策略研究2019-06-03 2615

-

AD650 电压频率和频率电压转换器2019-02-22 1262

-

基于STM32F051控制的LLC谐振变换器设计2018-01-25 2764

-

AD650模拟地PCB设计问题2016-01-25 3110

-

U/F变换器和F/U变换器2011-11-10 3750

-

28V-25V电压变换器2009-09-14 712

-

单片晶控变换器2009-09-12 533

-

利用AD650压频转换器设计频压转换器2009-06-11 1427

-

AD650电压频率与频率电压转换器2009-04-29 1606

-

V/F变换器电路图2009-04-11 2797

-

AD650(TD650)中文资料pdf2008-04-02 3737

全部0条评论

快来发表一下你的评论吧 !