芯片制造中的多晶硅介绍

描述

文章来源:半导体与物理

原文作者:jjfly686

本文主要介绍芯片制造中的多晶硅。

多晶硅(Poly- Si)

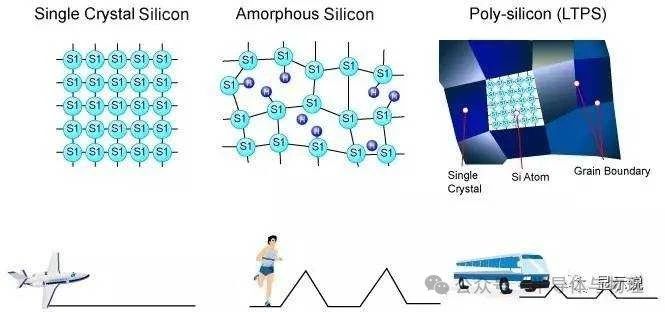

多晶硅(Polycrystalline Silicon,简称Poly)是由无数微小硅晶粒组成的非单晶硅材料。与单晶硅(如硅衬底)不同,多晶硅的晶粒尺寸通常在几十到几百纳米之间,晶粒间存在晶界。

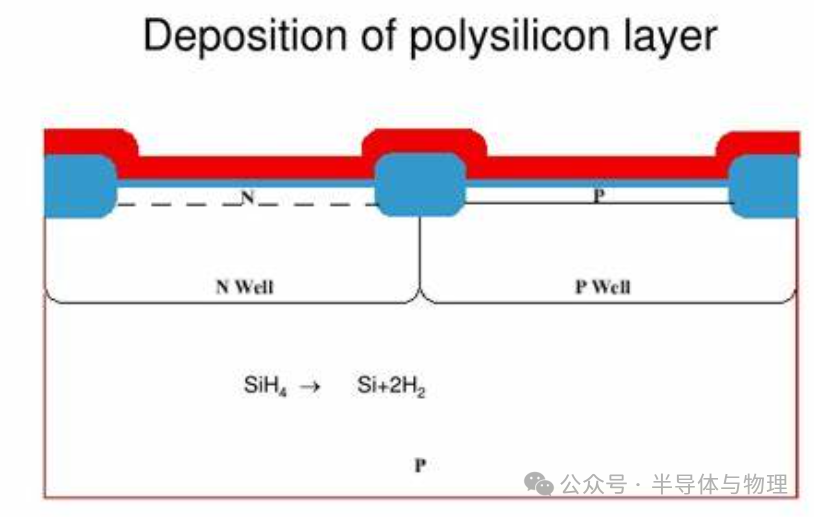

多晶硅的合成方法:LPCVD工艺

低压化学气相沉积是制备多晶硅的主流技术,其核心是通过硅烷(SiH₄)热分解生成硅原子并沉积成膜。

SiH4→Si+2H2↑

低温(<600℃)生成非晶硅,高温(>600℃)形成多晶硅。反应腔压力维持在0.1-1 Torr(低压环境提升薄膜均匀性)。

P型与N型多晶硅的合成

多晶硅的导电类型通过掺杂实现,分为P型(掺硼)和N型(掺磷/砷),工艺方法包括离子注入和原位掺杂:

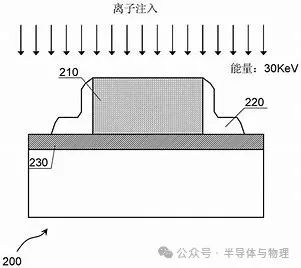

离子注入(主流技术)

N型掺杂:注入磷(P⁺)或砷(As⁺),剂量1×10¹⁵–1×10¹⁶ cm⁻²,能量10-50 keV;

P型掺杂:注入硼(B⁺),剂量与能量类似;

退火激活:快速热退火(RTA,900-1000℃)修复晶格损伤,激活杂质原子。

原位掺杂(LPCVD中同步掺杂)

气体掺杂:在SiH₄中混入PH₃(N型)或B₂H₆(P型),直接沉积掺杂多晶硅;

优势:避免注入损伤,但掺杂均匀性控制难度较高。

多晶硅在芯片制造中的核心作用

晶体管栅极材料

在栅绝缘介质上沉积多晶硅→掺杂→刻蚀成形→高温退火。掺杂后电阻率低至10⁻⁴ Ω·cm,传递控制信号;通过N/P型掺杂调节功函数(N-Poly用于NMOS,P-Poly用于PMOS)。

图案转移硬掩膜层

在刻蚀深槽或高深宽比结构时,多晶硅的硬度(莫氏硬度6.5)可保护底层材料。沉积500 nm多晶硅层;光刻定义图案;干法刻蚀多晶硅(Cl₂/HBr等离子体);以多晶硅为掩膜刻蚀下层介质/金属。

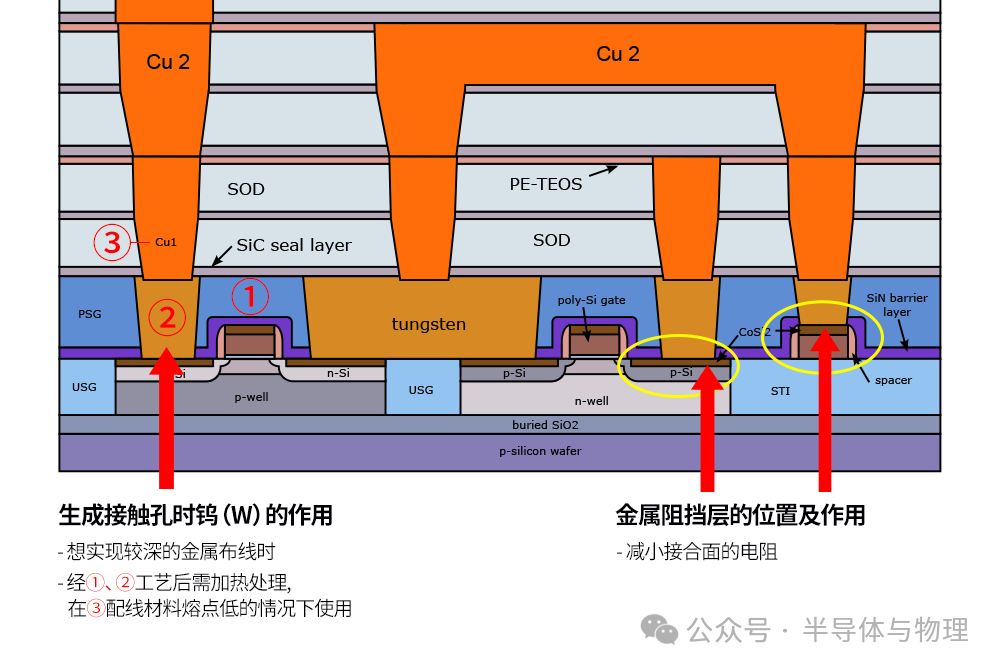

中段工艺(MEOL)接触连接点

在多晶硅与金属(如钨、钴)之间形成低阻接触。在接触孔中沉积掺杂多晶硅,作为金属与硅衬底的过渡层,减少肖特基势垒;在浅沟槽隔离(STI)区域用多晶硅连接相邻器件。

导电层与功函数调控

在FinFET中,多晶硅与High-K介质(如HfO₂)结合,通过掺杂类型和浓度调节阈值电压。N型多晶硅功函数≈4.1 eV,匹配NMOS沟道;P型多晶硅功函数≈5.2 eV,适配PMOS需求。

-

多晶硅在芯片制造中的作用2025-07-08 2791

-

LPCVD方法在多晶硅制备中的优势与挑战2025-04-09 1927

-

多晶硅的用途包括哪些2024-01-23 17248

-

多晶硅是什么东西_多晶硅属于什么行业2021-02-24 18970

-

FZ多晶硅24吨2020-01-20 1256

-

低温多晶硅的工作原理是什么?2019-09-18 3167

-

多晶硅原料是什么2019-04-11 38670

-

多晶硅太阳能电池结构_多晶硅太阳能电池原理2018-01-30 27554

-

多晶硅上市公司有哪些_国内多晶硅上市公司排名2017-12-18 67142

-

低温多晶硅,低温多晶硅是什么意思2010-03-27 1035

-

多晶硅产业发展浅析2009-12-14 718

-

什么是多晶硅2009-04-08 2872

-

单晶硅与多晶硅的区别2009-03-04 4895

全部0条评论

快来发表一下你的评论吧 !