芯片制造中的High-K材料介绍

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了High-K材料的物理性质、制备方法及其应用。

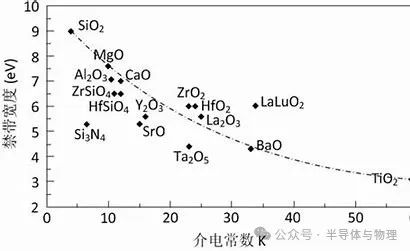

High-K材料(高介电常数材料)是介电常数显著高于传统二氧化硅(SiO₂,k=3.9)的绝缘材料,主要用于替代栅极介质层和电容介质层。随着芯片制程进入纳米级,传统SiO₂因厚度过薄(<2 nm)引发严重的量子隧穿效应,导致漏电流激增和功耗失控。High-K材料的引入,可在相同电容下增加物理厚度(如HfO₂的k=25,厚度可达SiO₂的3-6倍),从而抑制漏电流并提升器件可靠性。

常见High-K材料及其物理性质

| 材料 | 介电常数(k) | 热稳定性 | 应用场景 |

|---|---|---|---|

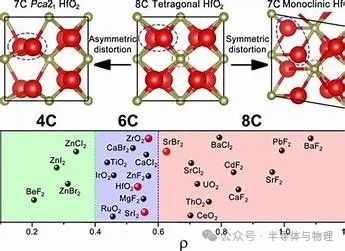

| HfO₂ | 20-25 | 易结晶 | 逻辑器件栅介质、DRAM电容 |

| ZrO₂ | 25-30 | 易结晶 | DRAM电容、存储介质 |

| TiO₂ | 30-80 | 易结晶 | 实验性栅介质 |

| HfSiON | 15-20 | >1000℃ | 高温兼容的栅介质层 |

| HfO₂-ZrO₂复合 | 30-50 | 高 | DRAM电容 |

HfO₂因兼具高k值和热稳定性,成为主流选择;HfSiON(氮氧化铪硅)通过掺氮优化界面态密度,常用于高温工艺。

ALD工艺合成HfO₂与HfSiON

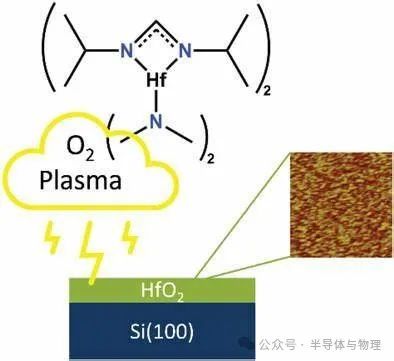

原子层沉积(ALD)是制备High-K薄膜的核心技术,可实现原子级厚度控制与三维结构保形性。

HfO₂的ALD合成

前驱体:四(乙基甲基胺基)铪(TEMAHf)或HfCl₄作为铪源,去离子水(H₂O)或臭氧(O₃)为氧源。

TEMAHf+H2O→HfO2+副产物气体(如NH3)

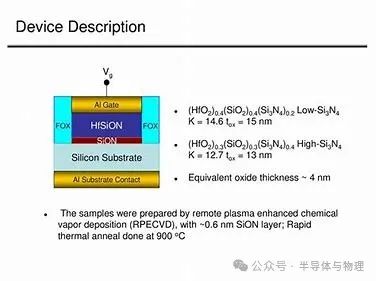

HfSiON的ALD合成

交替使用Hf前驱体(如TEMAHf)、硅源(如SiH₄或硅烷衍生物)及氮源(NH₃等离子体)。通过调节硅/氮的沉积比例,优化薄膜的k值和界面特性。例如,掺氮可减少氧空位缺陷,提升热稳定性。

High-K材料在芯片制造中的应用

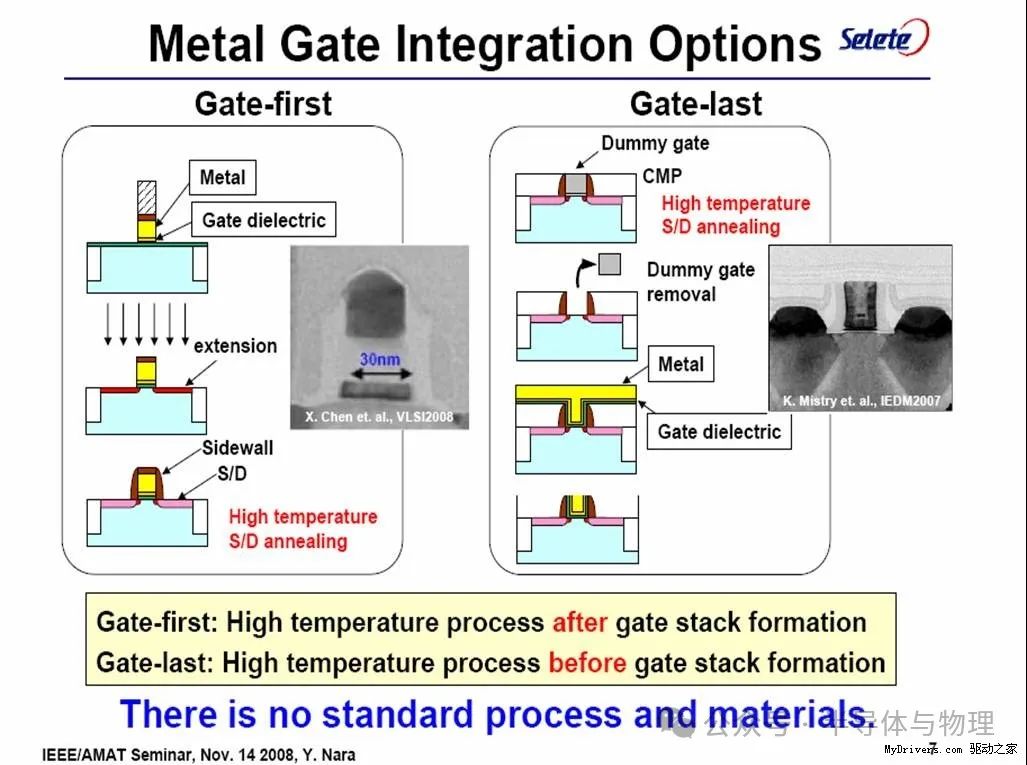

先栅HKMG工艺中的HfSiON

栅极在源漏注入前形成,需耐受高温退火(>1000℃)。HfSiON因高热稳定性与Si衬底兼容,常与多晶硅栅结合,用于45 nm及以上制程。降低等效氧化层厚度(EOT),同时抑制硼穿透(PMOS中常见问题)。

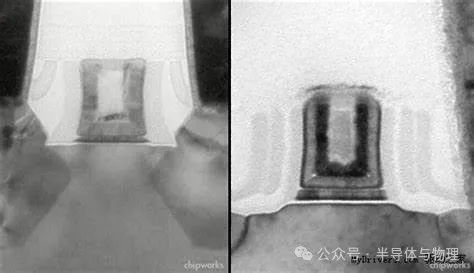

后栅HKMG工艺中的HfO₂

先形成多晶硅伪栅,完成高温工艺后替换为金属栅(如TiN)。HfO₂与金属栅(如TiN/Al)结合,用于22 nm以下FinFET制程。避免高温对金属栅的损伤,实现更薄EOT(<1 nm)和更低漏电流。

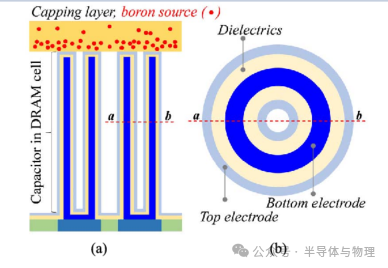

DRAM电容中的HfO₂与ZrO₂

在DRAM单元电容中,High-K材料(如HfO₂/ZrO₂堆叠)可大幅提升电容容量。

-

芯片制造中的半导体材料介绍2025-04-15 2372

-

芯片制造中的二氧化硅介绍2025-04-10 5546

-

Low-K材料在芯片中的作用2025-03-27 5129

-

集成电路制造工艺中的High-K材料介绍2025-03-12 3268

-

High-k栅极堆叠技术的介绍2024-12-28 2273

-

高K金属栅极的结构、材料、优势以及工艺流程2024-11-25 6979

-

高K介质(High-k Dielectric)和替代金属栅(RMG)工艺介绍2023-01-11 14020

-

精密划片机:半导体材料在芯片生产制造过程中的关键性作用2022-07-26 3414

-

芯片制造中的几种关键材料及其代表企业盘点2021-03-22 22753

-

【存储器】IC芯片制造流程介绍2018-06-14 3858

-

集成电路制造工艺升级的过程中,晶体管微缩会终结吗?2018-03-12 7298

-

什么是本体偏压/次临界漏电 (ISUBTH)/High-k2010-03-05 868

全部0条评论

快来发表一下你的评论吧 !