LTC6955超低抖动7.5GHz 11输出扇出缓冲器系列技术手册

描述

概述

LTC6955 是一款具有十一个输出的高性能超低抖动扇出时钟缓冲器。它的 4 引脚并行控制端口允许多种输出设置(3 个和 11 个之间的任意个输出)以及完全关断。利用该并行端口还能够反转交流输出的输出极性,从而简化采用顶部和底部板布线的设计。

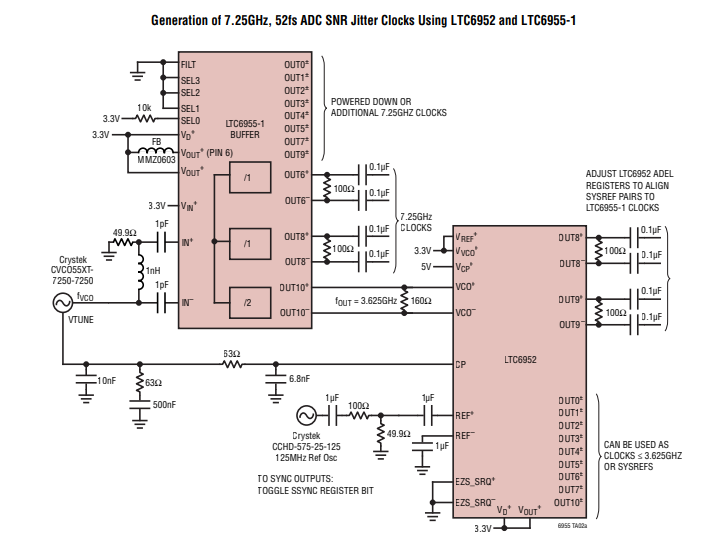

每个 CML 输出都可在直流至 7.5GHz 的频率范围内运行。LTC6955-1 用一个二分频器替代一个输出缓冲器,使其可以驱动 Linear Technology 的 LTC6952 或 LTC6953 以生成 JESD204B 子类 1 SYSREF 信号。这些 SYSREF 可以与 LTC6955-1 中的超低抖动器件时钟(能够以高达 7.5GHz 的频率运行)配对。

数据表:*附件:LTC6955超低抖动7.5GHz 11输出扇出缓冲器系列技术手册.pdf

应用

- 高性能数据转换器时钟

- SONET、光纤通道、GigE 时针分配

- 低偏斜/抖动时钟和数据扇出

- 无线和有线通信

- 单端到差分转换

特性

- LTC6955:11 输出缓冲器

- LTC6955-1:10 个缓冲输出和一个 ÷2 输出

- 附加输出抖动 ~45fs RMS(ADC SNR 方法)

- 附加输出抖动 < 5fs RMS(集成带宽 = 12kHz 至 20MHz,f = 7.5GHz)

- 十一个超低噪声 CML 输出

- 适用于多输出配置的并行控制

- 工作结温范围为 –40°C 至 125°C

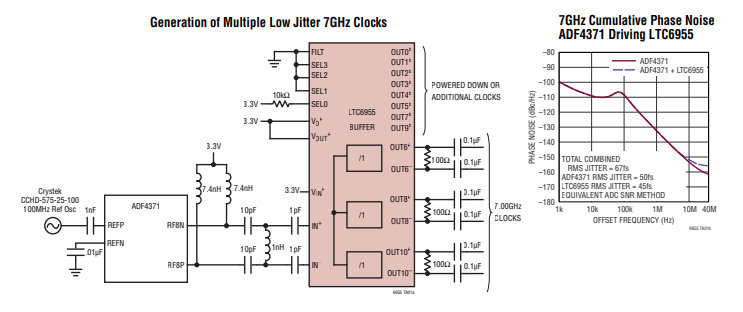

典型应用

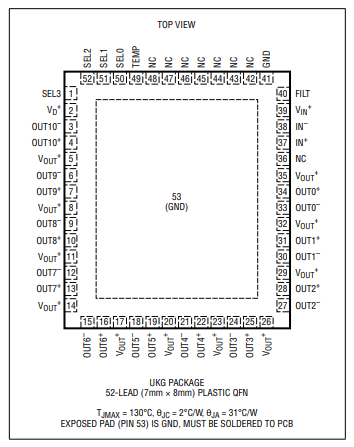

引脚配置

引脚功能

- SEL3、SEL2、SEL1、SEL0(引脚1、52、51、50) :并行端口控制位。这些CMOS输入用于控制输出配置。更多详情请参见“工作原理”部分。

- Vp⁺(引脚2) :3.15至3.45V并行端口正电源引脚。该引脚应使用0.1μF陶瓷电容尽可能靠近引脚直接旁路至接地层。

- Vout⁺(引脚5、8、11、14、17、20、23、26、29、32、35) :3.15至3.45V输出正电源引脚。每个引脚都应使用0.01μF陶瓷电容尽可能靠近引脚直接旁路至接地层。

- OUT10⁺、OUT10⁻(引脚3、4) :输出信号。输出经过缓冲,并在这些引脚上以差分形式呈现。每侧输出具有50Ω(典型值)的输出电阻(100Ω差分)。传输线的远端通常端接100Ω电阻,连接到输出端。对于LTC6955,此输出是输入的未分频版本,与其他输出相同。对于LTC6955 - 1,此输出是输入频率除以2的版本,只有单个信号。更多详情请参见“工作原理”和“应用信息”部分。

- OUT9⁺、OUT9⁻(引脚6、7) :输出信号。输出经过缓冲,并在这些引脚上以差分形式呈现。每侧输出具有50Ω(典型值)的输出电阻(100Ω差分)。传输线的远端通常端接100Ω电阻,连接到输出端。此输出是输入的未分频版本。

- OUT8⁺、OUT8⁻(引脚9、10) :与OUT9相同。

- OUT7⁺、OUT7⁻(引脚12、13) :与OUT9相同。

- OUT6⁺、OUT6⁻(引脚15、16) :与OUT9相同。

- OUT5⁺、OUT5⁻(引脚18、19) :与OUT9相同。

- OUT4⁺、OUT4⁻(引脚21、22) :与OUT9相同。

- OUT3⁺、OUT3⁻(引脚24、25) :与OUT9相同。

- OUT2⁺、OUT2⁻(引脚27、28) :与OUT9相同。

- OUT1⁺、OUT1⁻(引脚30、31) :与OUT9相同。

- OUT0⁺、OUT0⁻(引脚33、34) :与OUT9相同。

- NC(引脚36) :内部未连接。建议将此引脚连接到接地焊盘(引脚53)。

- IN⁺、IN⁻(引脚37、38) :输入信号。置于这些引脚上的差分信号由低噪声放大器缓冲,并馈送到内部分配路径和输出端。这些自偏置输入具有250Ω(典型值)的差分电阻,有助于阻抗匹配。它们可通过使用“应用信息”部分中的匹配电路以单端方式驱动。

- VIN⁺(引脚39) :3.15至3.45V输入电路正电源引脚。此引脚应使用0.01μF陶瓷电容尽可能靠近引脚直接旁路至接地层。

- FILT(引脚40) :输入滤波器控制引脚。接地时,输入不经过滤波。接V⁺时,输入经过滤波,以改善低转换速率输入信号的噪声性能。更多详情请参见“工作原理”部分。

- GND(引脚41) :负电源(接地)。此引脚应通过多个过孔直接连接到接地层。

- NC(引脚42、43、44、45、46、47、48) :未连接。这些引脚应保持开路或连接到GND。

- TEMP(引脚49) :温度测量引脚。启用后,此引脚输出温度测量二极管电压。更多详情请参见“工作原理”部分。

- GND(裸露焊盘53) :负电源(接地)。封装的裸露焊盘必须直接焊接到PCB焊盘。PCB焊盘图案应具有多个通往接地层的散热过孔,以实现低接地电感和低热阻。

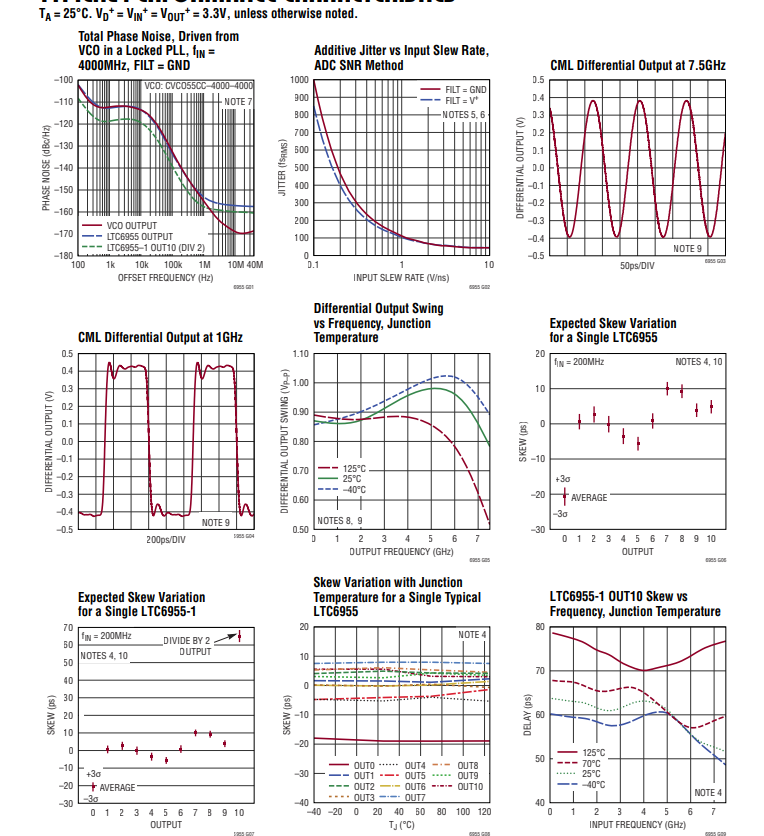

典型性能特征

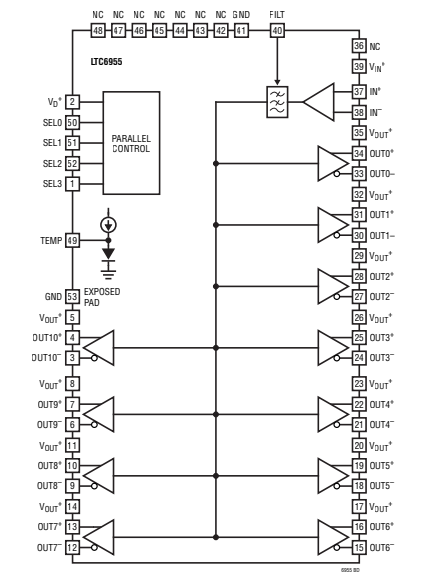

框图

引言

LTC6955可用于任何需要多个相同时钟频率输出的应用场景。在数据转换器时钟应用中,它尤其有效,因为在这类应用中,为避免对数据转换器的噪声性能产生负面影响,通常需要超低抖动。

输入

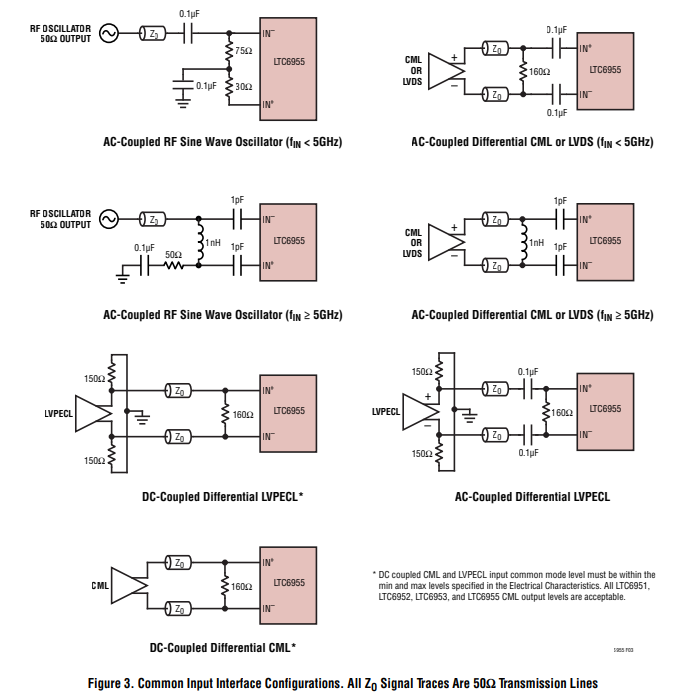

如图1所示,LTC6955的输入缓冲器频率范围为直流至7.5GHz。该缓冲器具有片内部分差分输入端接,阻值为250Ω,这为用户在需要时添加外部匹配网络提供了一定灵活性。图3展示了推荐的差分输入信号接口类型。

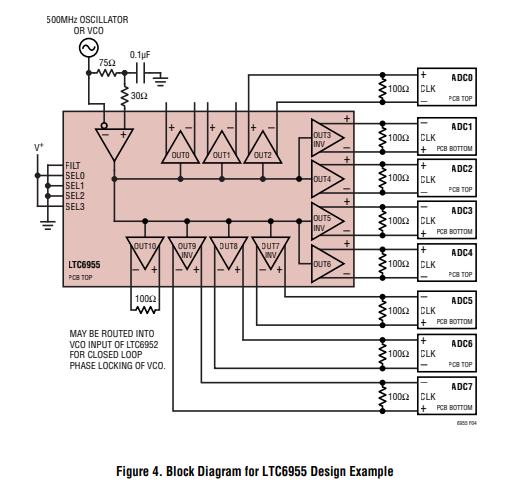

这个设计示例中,单个LTC6955驱动由八个模数转换器(ADC)组成的系统。假设印刷电路板(PCB)布局限制要求四个ADC位于电路的顶部,另外四个位于底部。这意味着LTC6955应理想地为顶部的ADC提供四个同相时钟,为底部的ADC提供四个反相时钟。参考表2,SEL编码9可提供所需的输出数量和极性,即使会有一个备用输出处于激活状态。图4展示了该系统的框图。需要注意的是,即使处于激活状态的输出未被使用,也应端接100Ω电阻。

应用电路

-

ZL40294B:面向PCIe Gen6的超低附加抖动时钟扇出缓冲器2025-09-28 526

-

LMK00105 超低抖动LVCMOS扇出缓冲器与电平转换器技术文档总结2025-09-15 823

-

德州仪器LMKDB11xx超低抖动时钟缓冲器技术解析2025-09-04 772

-

具有通用输入的LMK00101超低抖动LVCMOS扇出缓冲器/电平转换器数据表2024-08-22 317

-

如何测量扇出缓冲器中的附加抖动2022-11-21 573

-

测量扇出缓冲器中的附加抖动2022-11-04 588

-

超低附加抖动时钟缓冲器的主要技术特点2022-05-07 1892

-

LTC6955:超低抖动、7.5 GHz、11输出扇出缓冲器系列数据表2021-05-27 798

-

测量扇出缓冲器中的附加抖动怎么计算?2021-05-06 1179

-

HMC7043:高性能、3.2 GHz、14输出扇出缓冲器数据表2021-04-28 1415

-

UG-892:评估HMC7043高性能、3.2 GHz、14输出扇出缓冲器2021-04-27 967

-

AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整2021-03-21 902

-

LTC6955 超低抖动 7.5GHz 11 输出扇出缓冲器系列2019-02-15 599

-

扇出缓冲器中的附加抖动测量2018-09-13 1487

全部0条评论

快来发表一下你的评论吧 !