LTC6952具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz PLL技术手册

描述

概述

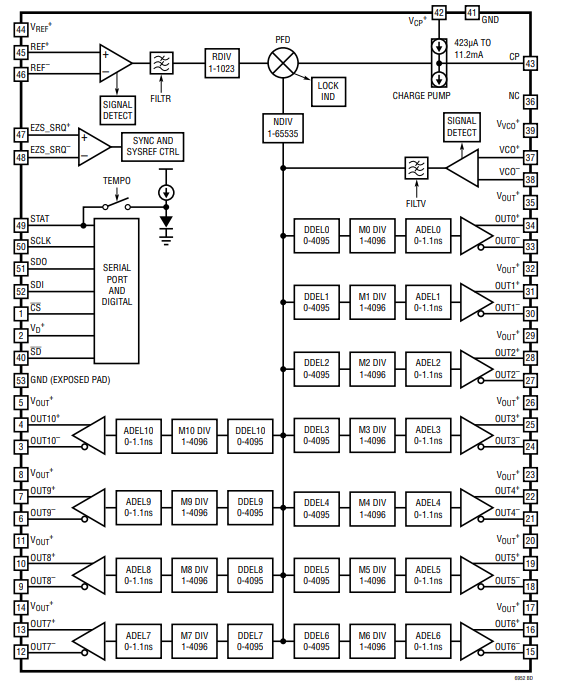

LTC6952 是一款高性能、超低抖动 JESD204B/C 时钟生成和分配 IC。该器件包括一个锁相环 (PLL) 内核,由基准分频器、具有锁相指示器的相位频率检波器 (PFD)、超低噪声充电泵和整数反馈分频器构成。LTC6952 的 11 个输出可配置为最多 5 个 JESD204B/C subclass 1 器件时钟/SYSREF 对以及一个通用输出,或者就是 11 个面向非 JESD204B/C 应用的通用时钟输出。每个输出都有自己的可单独编程分频器和输出驱动器。所有输出也可以采用单独的粗略半周期数字延迟和精细模拟时间延迟实现同步,并设定为精确的相位对齐。

对于需要 11 个以上总输出的应用,可以使用 EZSync 或 ParallelSync 同步协议将多个 LTC6952 连接在一起。

数据表:*附件:LTC6952具有11个输出并支持JESD204B JESD204C协议的超低抖动、4.5GHz PLL技术手册.pdf

应用

- 高性能数据转换器时钟

- 无线基础设施

- 测试和测量

特性

- JESD204B/C,子类 1 SYSREF 信号生成

- 低噪声整数 N PLL

- 附加输出抖动 < 6fs

RMS- (集成带宽 = 12kHz 至 20MHz,f = 4.5GHz)

- 附加输出抖动 65fs

RMS(ADC SNR 方法) - EZSync ^™^ 、ParallelSync^™^ 多芯片同步

- –229dBc/Hz 归一化带内相位本底噪声

- –281dBc/Hz 归一化带内 1/f 噪声

- 11 个独立低噪声输出,具有可编程粗数字延迟和精细模拟延迟

- 灵活的输出可以用作套件时钟或 SYSREF 信号

- 基准输入频率达 500MHz

- LTC6952Wizard^™^ 软件设计工具支持

- 工作结温范围为 –40ºC 至 125°C

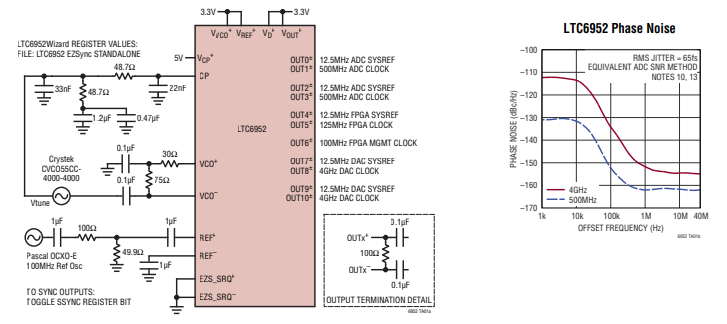

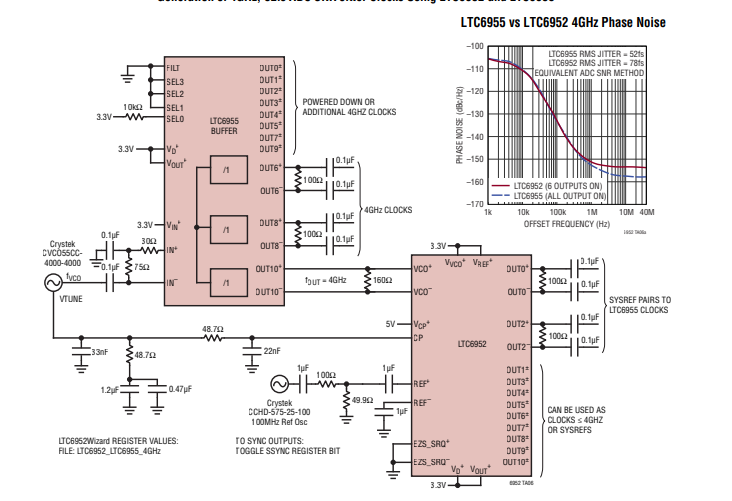

典型应用

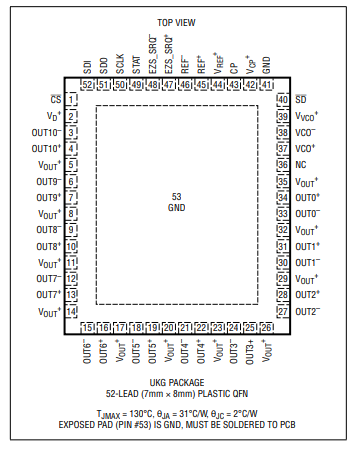

引脚图

框图

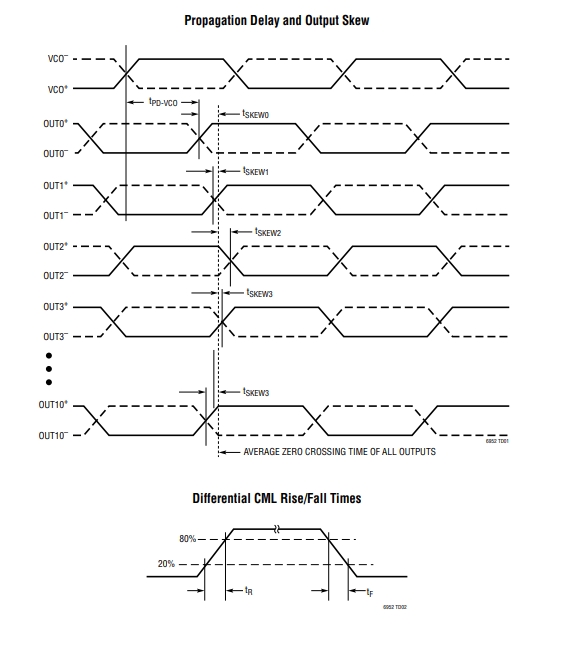

时序图

应用电路

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

JESD204B的系统级优势2018-09-18 2403

-

JESD204B串行接口时钟的优势2019-06-19 3733

-

带JESD204B输出的14位170Msps双通道ADC2019-06-20 2866

-

JESD204C的标准和新变化2021-01-01 3026

-

JESD204B协议有什么特点?2021-04-06 2111

-

如何采用系统参考模式设计JESD204B时钟2022-11-18 778

-

JESD204B协议介绍2022-11-21 943

-

LTC6952 具有 11 个输出和 JESD204B/JESD204C 支持的超低抖动 4.5GHz PLL2019-02-22 541

-

LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持数据表2021-04-22 1185

-

LTC6953:超低抖动、4.5 GHz时钟分配器,带11个输出和JESD204B/JESD204C支持数据表2021-05-19 1109

-

理解JESD204B协议2022-11-04 968

-

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet2023-10-16 72

-

从JESD204B升级到JESD204C时的系统设计注意事项2024-09-21 1065

-

JESD204B使用说明2024-12-18 3048

-

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册2025-04-16 1329

全部0条评论

快来发表一下你的评论吧 !