AD9576双通道PLL、异步时钟发生器技术手册

描述

概述

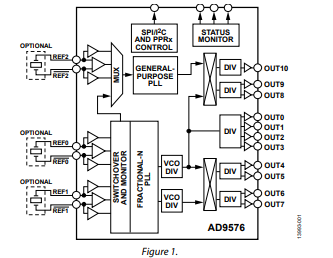

AD9576具有多路输出时钟发生器功能,内置两个具有灵活频率转换功能的专用锁相环(PLL)内核,经过优化可用作整个系统的稳定异步时钟源,通过监控冗余晶体(XTAL)输入并实现这些输入之间的自动切换,可在频率容差范围内延长工作寿命,同时将开关感应瞬变降至低点。小数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现较高的网络性能,而整数N分频PLL提供通用型时钟,可用作CPU和现场可编程门阵列(FPGA)参考时钟。

数据表:*附件:AD9576双通道PLL、异步时钟发生器技术手册.pdf

AD9576利用引脚短接为其11路输出时钟在众多可用上电就绪配置中进行选择,只需将外部上拉或下拉电阻连接到适当的引脚编程读取器引脚(PPRx)即可。通过这些引脚可以控制内部分频器,以建立所需的频率转换、时钟输出功能和输入参考功能。这些参数还可以通过串行端口接口(SPI)进行手动配置。

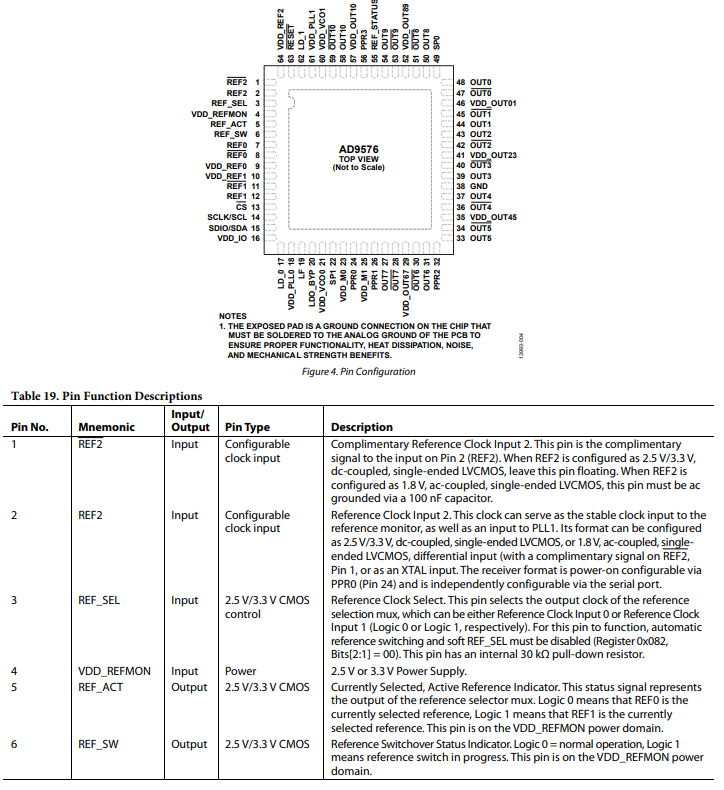

AD9576采用64引脚、9 mm × 9 mm LFCSP封装,只需2.5 V或3.3 V单电源供电。工作温度范围为−40°C至+85°C。

每个OUTx输出都是差分输出,并包含两个引脚:OUTx和OUTx。为简单起见,术语OUTx是指包含这两个引脚的功能输出模块。

应用

- 以太网线路卡、交换机和路由器

- 基带单元

- SATA和PCI Express

- 低抖动、低相位噪声时钟产生

- 异步时钟产生

特性 - 单通道、低相位噪声、完全集成的VCO/小数N分频PLL内核

- VCO范围:2375 MHz至2725 MHz

- 集成环路滤波器(需要单个外部电容)

- 2路差分、XTAL或单端参考输入

- 参考监控功能

- 自动冗余XTAL切换

- 最小瞬态、平滑切换

- 典型RMS抖动

- <0.3 ps(12 kHz至20 MHz,整数N分频转换)

- <0.5 ps(12 kHz至20 MHz,小数N分频转换)

- 输入频率

- 8 kHz、1.544 MHz、2.048 MHz和10 MHz至325 MHz

- 通过引脚短接实现预设频率转换(PPRx)

- 采用25 MHz输入参考

- 24.576 MHz、25 MHz、33.33 MHz、50 MHz、70.656 MHz、100 MHz、125 MHz、148.5 MHz、156.25 MHz、161.1328 MHz、312.5 MHz、322.2656 MHz、625 MHz或644.5313 MHz

- 采用19.44 MHz输入参考

- 50 MHz、100 MHz、125 MHz、156.25 MHz、161.1328 MHz或644.5313 MHz

- 采用30.72 MHz输入参考

- 25 MHz、50 MHz、100 MHz、125 MHz或156.25 MHz

- 采用25 MHz输入参考

- 单通道、完全集成的通用型VCO/整数N分频PLL内核

- VCO范围:750 MHz至825 MHz

- 集成环路滤波器

- 独立重复参考输入或采用小数N分频PLL有效参考输入工作

- 输入频率:25 MHz

- 通过引脚短接实现预设频率转换(PPRx)

- 25 MHz、33.33 MHz、50 MHz、66.67 MHz、100 MHz、133.33 MHz、200 MHz或400 MHz

- 多达3路基准时钟输出

- 11对可配置差分输出

- 输出驱动格式

- 3路输出:HSTL、LVDS、HCSL、1.8 V CMOS、2.5 V/3.3 V CMOS

- 8路输出:HSTL、LVDS或1.8 V CMOS

- 输出驱动格式

- 2.5 V或3.3 V单电源供电

框图

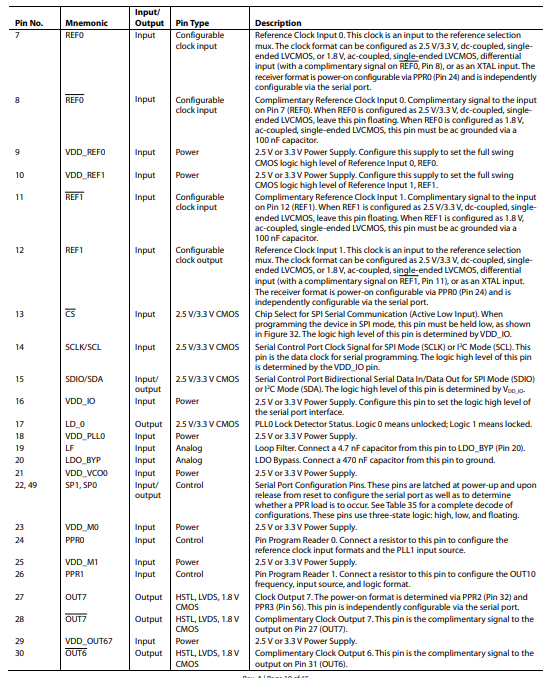

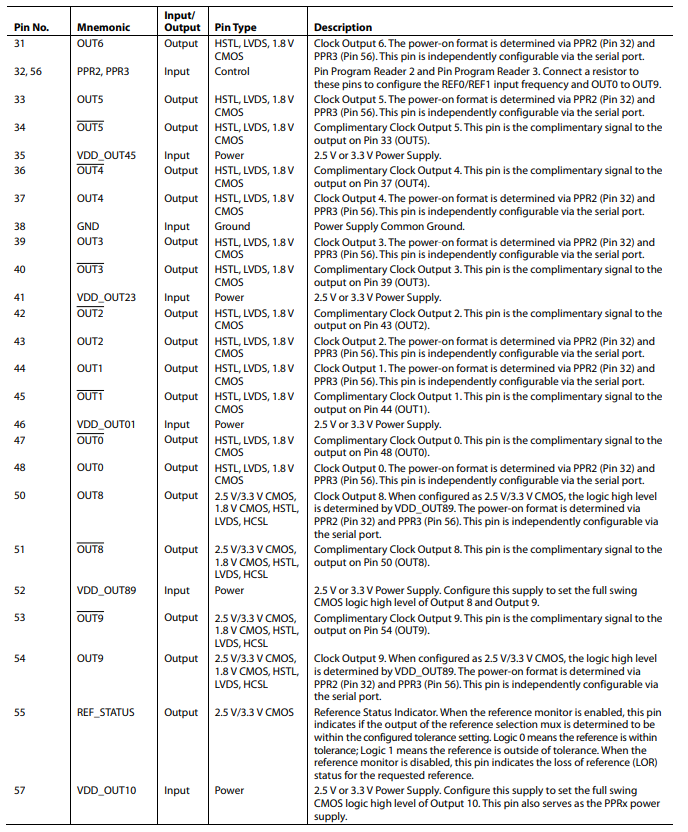

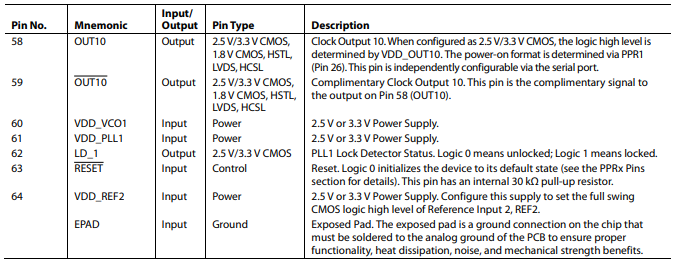

引脚配置描述

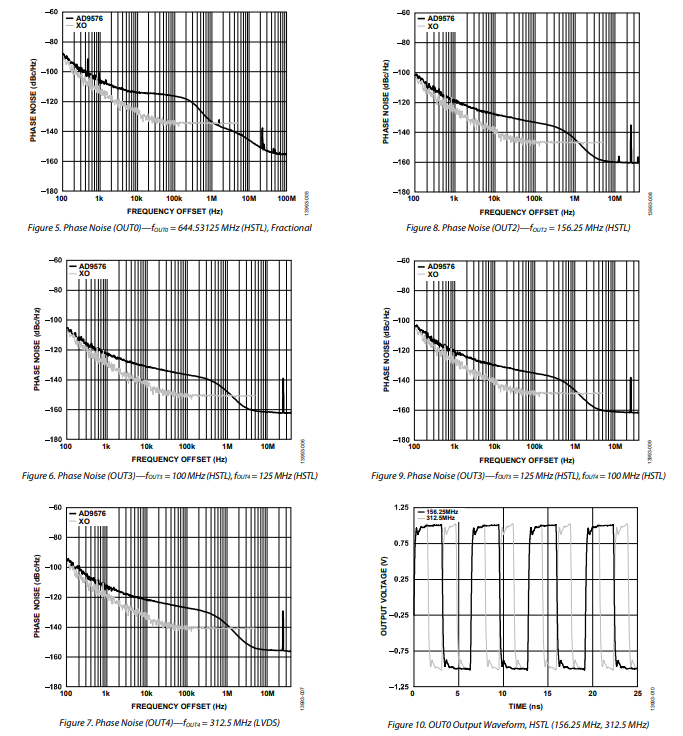

典型性能特征

操作理论

概述

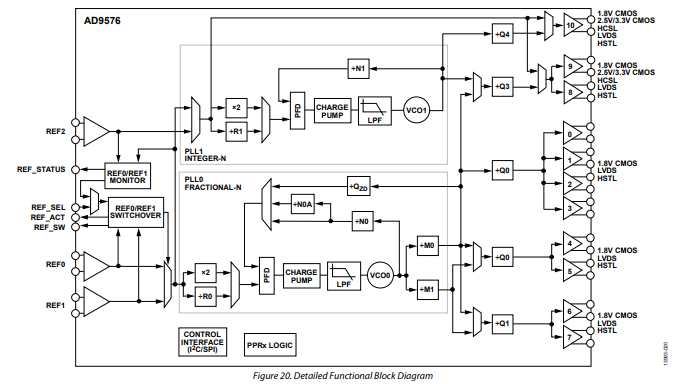

图20展示了AD9576的框图。AD9576采用2.5V或3.3V单电源供电,是一款完全可编程、随时可用的双输出时钟芯片,通过串行端口接口(SPI)进行控制。两个并行通道分别由一个高性能分数N型锁相环(PLL0)和一个通用整数N型锁相环(PLL1)构成。

AD9576有三个参考输入(REF0至REF2)。每个输入接收器都支持差分或单端输入配置。REF0和REF1驱动参考切换多路复用器(mux)。输出多路复用器的输出选择REF0或REF1来驱动PLL0的输入,并作为PLL1参考选择多路复用器的监控时钟,同时监控参考切换多路复用器的输出时钟频率。REF2支持8kHz、10MHz、19.44MHz、25MHz和38.88MHz的频率,而REF0和REF1支持8kHz、1.544MHz、2.048MHz、10MHz至325MHz的频率。不过,PLL1相位和PFD频率限制为25MHz,50MHz是唯一允许作为PLL1输入的参考频率。

AD9576提供多达11个输出通道时钟(OUT0至OUT10)。OUT0至OUT7由PLL0驱动,分为三组:OUT0至OUT3、OUT4和OUT5、OUT6和OUT7 。每组中的每个输出可单独配置,但会生成相同的输出频率。这些输出支持LVDS、HSTL或1.8V LVCMOS输出格式。

OUT8和OUT9有三个潜在的时钟源:PLL1参考选择多路复用器的输出、PLL0的输出或PLL1的输出。这些输出可单独配置,但必须共享相同的时钟源,因此也具有相同的输出频率。OUT10由PLL1的输出或参考选择多路复用器的输出驱动。这三个输出支持LVDS、HSTL、HCSL、1.8V CMOS和2.5V/3.3V CMOS(摆幅由电源电平决定)输出格式。

参考输入

AD9576具有灵活的PLL参考输入电路,提供三种工作模式:单端输入、完全差分输入或外接晶体输入。REF0、REF1和REF2输入接收器的工作模式可通过PPR0引脚或寄存器0x080和寄存器0x081(见表45)进行选择和控制。寄存器0x080和寄存器0x081允许REF0和REF1的工作模式完全独立于参考输入。

-

AD9576:高性能双PLL异步时钟发生器的深度解析2026-03-23 271

-

Texas Instruments PLL1707和PLL1708:低抖动多时钟发生器的卓越之选2026-02-10 376

-

德州仪器PLL1707和PLL1708:低抖动多时钟发生器的卓越之选2026-02-04 211

-

CDCM9102低噪声双通道100MHz时钟发生器数据表2024-08-22 458

-

时钟发生器由哪些部分组成?锁相环pll的特点是什么?2023-10-13 2575

-

时钟发生器AD9516-0技术手册2022-01-25 1005

-

AD9576:双锁相环异步时钟发生器数据表2021-05-16 954

-

AD9576 IBIS Model2021-03-10 880

-

用于评估AD9576时钟倍频器异步时钟发生器的评估板AD9576/PCBZ2019-02-25 3469

-

AD9576 双通道PLL、异步时钟发生器2019-02-22 771

-

评估低抖动PLL时钟发生器的电源噪声抑制性能2009-09-18 1913

全部0条评论

快来发表一下你的评论吧 !