AD9530集成5.4 GHz VCO的4路CML输出、低抖动时钟发生器技术手册

描述

概述

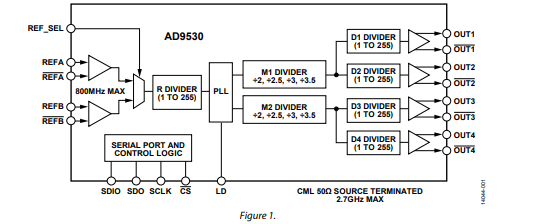

AD9530是一款针对40 Gbps/ 100 Gbps OTN应用的完全集成式PLL和分配器件,支持时钟清零和频率转换。 内部PLL可锁定至两个参考频率之一以生成最高达2.7 GHz的四个离散输出频率。

AD9530集成了内部5.11 GHz至5.4 GHz、超低噪声压控振荡器(VCO)。 所有四个输出均从内部VCO进行单独分频,并使用两个高速VCO分频器(Mx分频器)和四个独立的8位通道分频器(Dx分频器)。 高速VCO分频器提供2、2.5、3、和3.5固定分频,提供宽覆盖范围的可能输出频率。 AD9530配置用于小于15 kHz的环路带宽以便衰减基准电压源噪声。

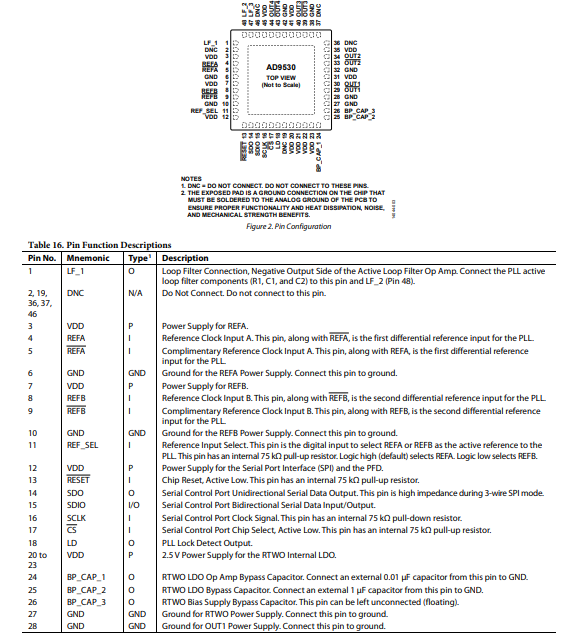

AD9530提供48引脚LFCSP封装,采用典型2.5 V单电源供电。

AD9530的工作温度范围为−40°C至+85°C的扩展工业温度范围。

数据表:*附件:AD9530集成5.4 GHz VCO的4路CML输出、低抖动时钟发生器技术手册.pdf

应用

- 40 Gbps/100 Gbps光传输网络(OTN)线路端时钟

- 高速模数转换器(ADC)和数模转换器(DAC)时钟

- 数据通信

特性 - 完全集成式超低噪声锁相环(PLL)

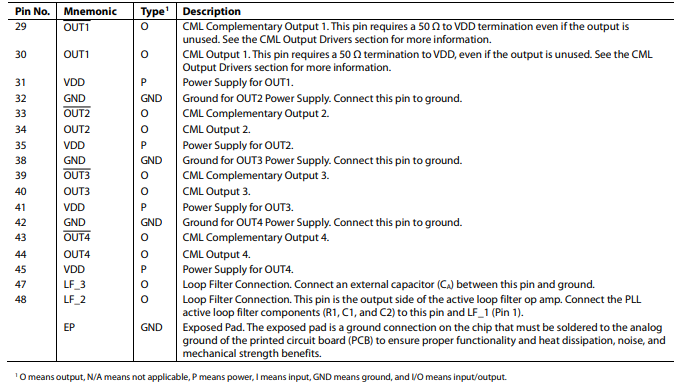

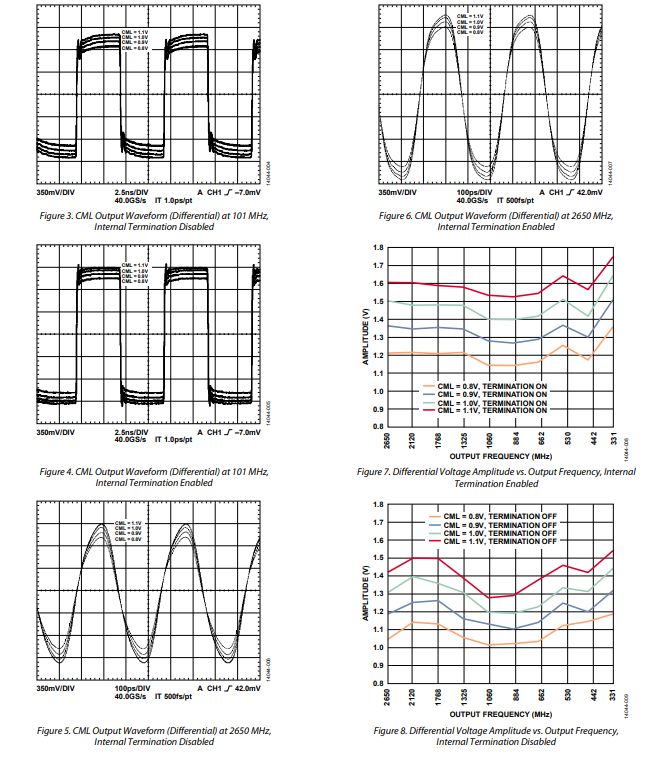

- 4个差分、2.7 GHz共模逻辑(CML)输出

- 带可编程内部端接选项的2个差分基准电压输入

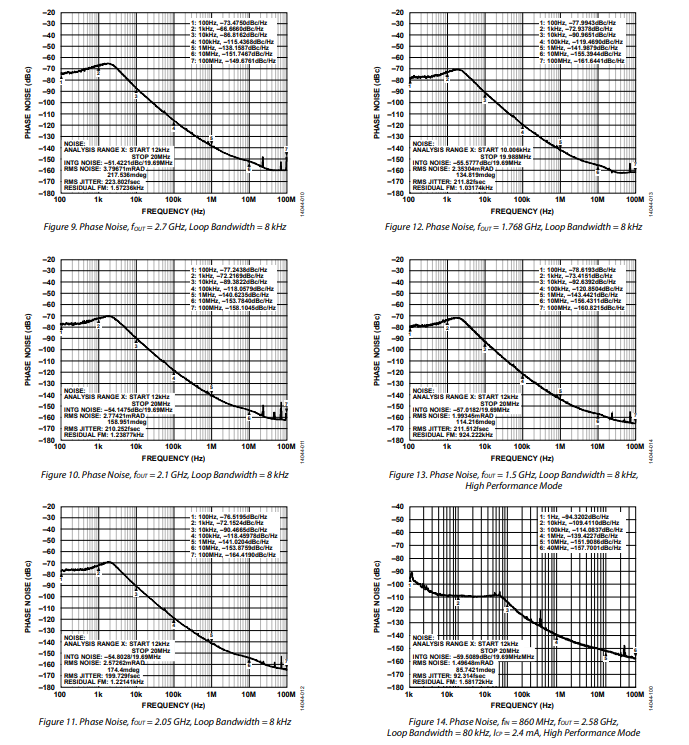

- 绝对抖动小于232 fs rms(12 kHz至20 MHz),具有非理想基准电压和8 kHz环路带宽

- 绝对抖动小于100 fs rms(12 kHz至20 MHz),具有80 kHz环路带宽和低抖动输入参考时钟

- 支持适合抖动衰减应用的低环路带宽

- 手动切换

- 采用典型2.5 V单电源供电

- 48引脚、7 mm × 7 mm LFCSP封装

框图

引脚配置描述

典型性能特征

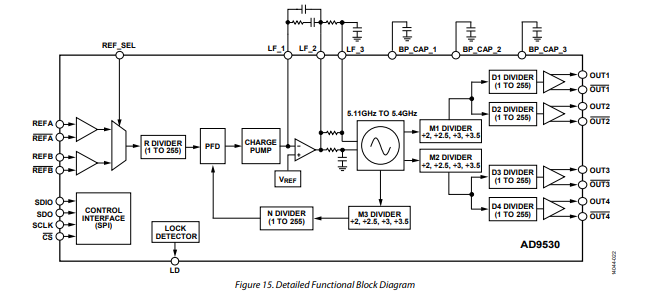

操作原理详细功能框图

AD9530 是一款全集成的整数 N 型锁相环(PLL),具有超低噪声的内部 5.11 GHz 至 5.4 GHz 压控振荡器(VCO),能够产生小于 232 fs(均方根,12 kHz 至 20 MHz)抖动的两路正交信号,参考信号为非相干信号。AD9530 适用于 40 Gbps 和 100 Gbps 光传输网络(OTN)应用,这些应用对转换器和专用集成电路(ASIC)时钟的规格要求严格。

AD9530 集成了片上锁相环、内部压控振荡器,以及四个具有集成驱动器的输出通道和共模逻辑(CML)驱动器。锁相环包含一个部分内部有源环路滤波器,这需要少量外部组件来实现环路带宽低于 15 kHz,以抑制参考相位噪声。

AD9530 的四个输出具有独立的分频器,可生成高达 2.7 GHz 的四个不同频率。

锁相环配置

锁相环的配置是通过对各种设置进行编程来实现的,包括 R 分频器、N 分频器、M3 分频器、电荷泵电流,以及压控振荡器的组合。这些设置与环路滤波器共同决定了锁相环的带宽和稳定性。

锁相环的成功运行和令人满意的性能在很大程度上取决于适当的内部锁相环设置和环路滤波器。ADIsimCLK 是一款免费软件,有助于设计和探索 AD9530 的功能特性,包括锁相环和滤波器的设计。

鉴频鉴相器(PFD)

鉴频鉴相器接收来自 R 分频器输出和反馈分频器路径的输入,产生一个与两者之间的相位和频率差成正比的输出。它包含一个可调节延迟元件,用于控制反冲脉冲的宽度。该脉冲可确保鉴频鉴相器中不存在死区,从而实现相位和频率噪声的最小化。

鉴频鉴相器的最大允许输入频率在表 5 中有具体规定。

电荷泵(CP)

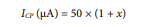

电荷泵由鉴频鉴相器控制。鉴频鉴相器监测两个输入之间的相位和频率关系,并使电荷泵相应地充电或放电,对作为环路滤波器一部分的积分节点进行操作。经过积分和滤波的 CP 电流被转换为一个电压,该电压驱动调谐节点,使压控振荡器朝着目标频率上升或下降。电荷泵电流可进行 52 步编程,每步对应电流增加 50 μA。

通过以下公式计算电荷泵电流 (I_{CP}:

其中 x 是写入寄存器 0x025 第 5:0 位的值。

-

详解AD9530:低抖动时钟发生器的卓越之选2026-03-23 162

-

CDCM61002两路输出、集成VCO、低抖动时钟发生器数据表2024-08-22 944

-

AD9520-4:12集成1.6 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器2021-05-07 898

-

AD9522-4:12集成1.6 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器2021-04-29 780

-

AD9530:4 CML输出、低抖动时钟发生器,集成5.4 GHz压控振荡器数据表2021-04-24 850

-

AD9520-1:12集成2.5 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器2021-04-18 739

-

AD9523-1:低抖动时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册2021-03-21 754

-

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO2021-03-19 729

-

用于评估AD9530 2.7 GHz时钟发生器的评估板AD9530/PCBZ2019-02-26 2141

-

AD9530 集成5.4 GHz VCO的4路CML输出、低抖动时钟发生器2019-02-15 575

-

MAX3624 低抖动、精密时钟发生器,提供四路输出2009-09-18 993

-

MAX3625A 低抖动、精密时钟发生器,提供三路输出(应用2009-08-13 1187

全部0条评论

快来发表一下你的评论吧 !