LTC6951具集成型VCO的超低抖动、多输出时钟合成器技术手册

描述

概述

LTC 6951 是一款具一个全集成型 VCO 的高性能、低噪声锁相环 (PLL)。低噪声 VCO 未使用外部组件,并且在没有外部系统支持的情况下在内部校准至正确的输出频率。

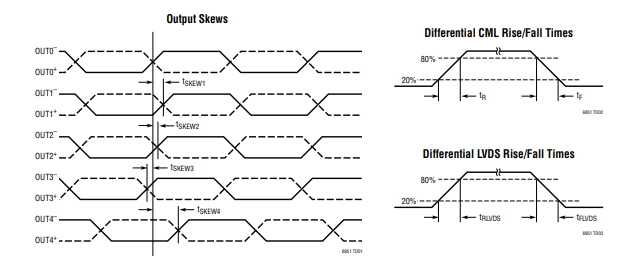

时钟发生部分提供了 5 个基于 VCO 前置分频器信号的输出,并具有用于每个输出的个别分频器。四个输出具有非常低噪声、低偏斜 CML 逻辑信号。第五个输出是低噪声 LVDS。所有的输出可实现同步并采用可编程延迟设定至精准的相位对齐。

如果任何期望的输出频率位于 2.5GHz 至 2.7GHz、1.66GHz 至 1.8GHz、或 1.25GHz 至 1.35GHz 的范围内,那么选择 LTC6951-1。对于所有其他的频率则选择 LTC6951。

数据表:*附件:LTC6951具集成型VCO的超低抖动、多输出时钟合成器技术手册.pdf

应用

- 高性能数据转换器计时

- 无线基础设施

- 测试和测量

特性

- 集成VCO的低噪声整数N分频PLL

- 输出抖动

- 90fs RMS(12kHz至20MHz)

- 115fs RMS(ADC SNR方法)

- 本底噪声 = –165dBc/Hz (250MHz)

- EZSync ^™^ 、ParallelSync ^™^ 多芯片同步

- 用于JESD204B/JESD204C的SYSREF产生,子类1

- 输出频率范围:

- 1.95MHz至2.5GHz(LTC6951)

- 2.1MHz至2.7GHz(LTC6951-1)

- 归一化带内相位本底噪声:–229dBc/Hz

- 归一化带内1/f噪声:–277dBc/Hz

- 五个独立的、低噪声输出

- 基准输入频率高达425MHz

- LTC6951Wizard ^™^ 软件设计工具支持

- 工作结温范围:-40°C至105°C

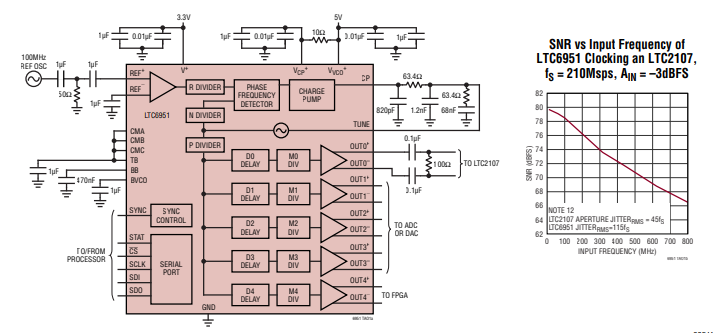

典型应用

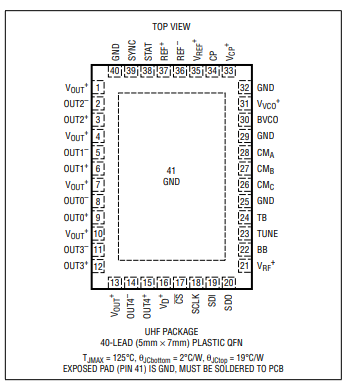

引脚配置

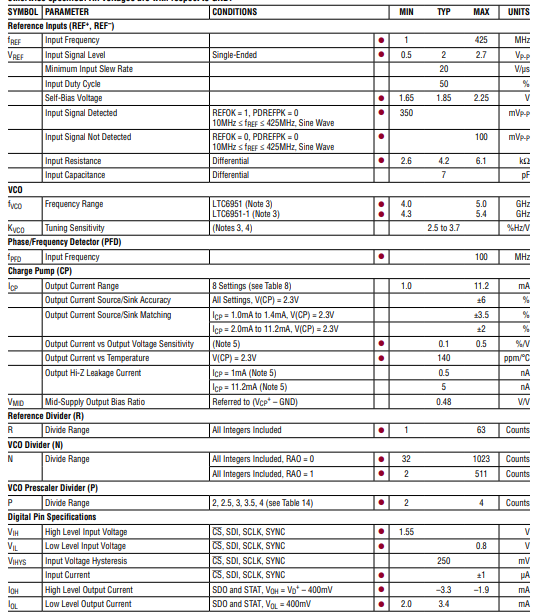

电特性

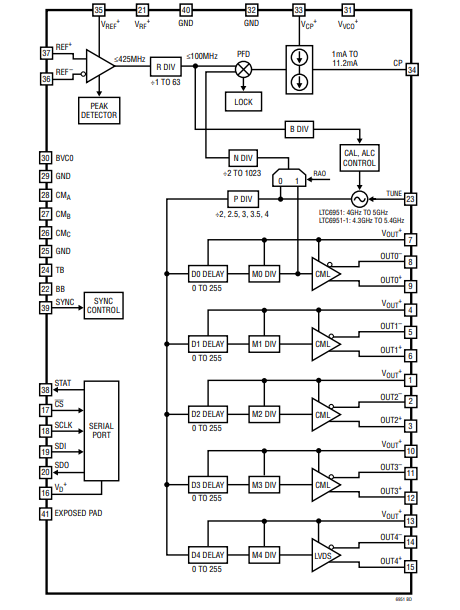

框图

时序图

工作原理

LTC6951 是一款高性能整数 N 型锁相环(PLL),配备低噪声压控振荡器(VCO)。其多输出时钟发生器集成了凌力尔特公司(Linear Technology)专有的 EZSync 和 ParallelSync 技术,可实现跨多个输出和多个芯片的同步。通过结合其极低的带内相位噪声和出色的 VCO 噪声特性,该器件能够实现卓越的集成抖动性能。

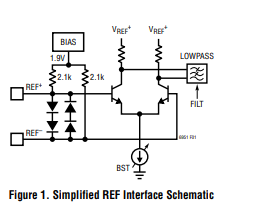

参考输入缓冲器

锁相环的参考频率以差分方式施加到引脚 REF⁺ 和 REF⁻ 上。这些高阻抗输入是自偏置的,必须通过 1μF 电容进行交流耦合(简化示意图见图 1)。或者,可通过将 REF⁻ 引脚旁路到地,并在 REF⁺ 引脚施加参考频率来实现单端输入。如果单端信号大于 2.7Vₚ₋ₚ,则使用 470pF 电容作为接地旁路。

必须向 REF⁺ 输入引脚施加高质量信号,因为它们为整个锁相环提供参考频率基准。为实现器件的带内相位噪声性能,需向 50Ω 输入施加至少 6dBm 的方波信号,或施加至少 0.5Vₚ₋ₚ 且斜率至少为 20V/μs 的方波信号。图 2 展示了针对不同参考类型的推荐接口。

通过串行端口寄存器可提供其他选项,以进一步优化应用。FILT 位控制参考输入缓冲器的低通滤波器,应根据 fREF 设置该位,以限制参考信号噪声。只有在 FILT 位设置正确的情况下,才能达到 LNORM 归一化带内相位噪声基准。表 1 给出了推荐设置。方波输入应设置为“0”。

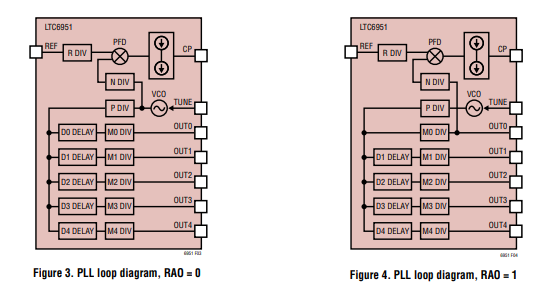

参考对齐输出(RAO)

RAO 位(寄存器 h03)控制锁相环(PLL)的基本配置。图 3 为 PLL 环路图,当 RAO 位设置为 “0” 时,五个输出中的所有相位都将同步,并可相对于彼此进行延迟,但不会与参考输入对齐。

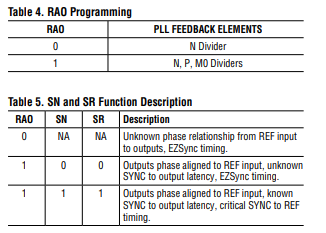

如图 4 所示,需要在单个基础上或跨多个 LTC6951 将输出与参考输入对齐的系统,可将 RAO 位设置为 “1”,以实现整个 PLL 配置。此时,P 分频器和 M0 分频器成为整体 PLL 反馈元件的一部分。表 4 详细说明了在 PLL 反馈元件与 RAO 位设置不同的情况下,P 分频器和 M0 分频器的差异。只有当 N 分频器输出的上升沿与 R 分频器输出的上升沿一致时,输出才会与参考时钟对齐。

当 RAO 设置为 “1” 时,SR 位和 SN 位将被激活,除了能够将输出与已知且可重复的参考输入延迟对齐外,还能为输出提供已知且可重复的延迟。图 5 展示了 SR 位的工作原理,图 11 展示了 SN 位的工作原理。表 5 简要描述了芯片同步功能。有关多芯片同步示例,请参见 “并行同步多芯片” 信息部分,了解编程示例和输出定时图。

-

LTC6951:超低抖动多输出时钟合成器的卓越之选2026-03-26 241

-

LTC6951:集成压控振荡器数据表的超低抖动多输出时钟合成器2021-05-19 1056

-

DC1959B-D具有集成VCO的超低噪声和杂散小数N分频合成器2019-07-19 1331

-

DC1705C-D是一款具有集成VCO的超低噪声和伪整数N频率合成器2019-07-18 2725

-

DC1959B-C是具有集成VCO的超低噪声和杂散小数N分频合成器2019-07-17 2130

-

集成VCO的2000 MHz超低噪声PLL时钟合成器AD9517-3A/PCBZ评估板2019-03-05 2046

-

采用LTC6946超低噪声和杂散整数N频率合成器,集成VCO的演示板DC1705B-A2019-02-28 2833

-

具有集成VCO,时钟分频器和多达24个输出的超低噪声PLL时钟合成器AD9522-4/PCBZ2019-02-22 2534

-

LTC6951 具集成型 VCO 的超低抖动、多输出时钟合成器2019-02-15 790

-

具分配电路的超低抖动 2MHz 至 2700MHz 时钟合成器2016-03-23 1509

-

超低抖动时钟合成器的设计挑战2009-04-21 1082

全部0条评论

快来发表一下你的评论吧 !