LTC6954低相位噪声、三路输出时钟分配分频器/驱动器技术手册

描述

概述

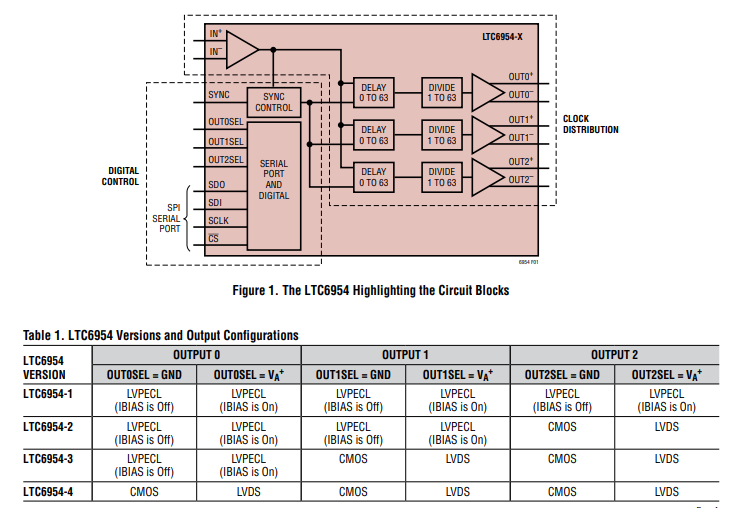

LTC6954属于极低相位噪声时钟分配器件系列。每个器件具有三个输出,且每个输出具有可单独编程的分频器和延迟性能。该系列有四款产品,分别具有不同的输出逻辑信号类型:

LTC6954-1:三个LVPECL输出

LTC6954-2:两个LVPECL和一个LVDS/CMOS输出

LTC6954-3:一个LVPECL和两个LVDS/CMOS输出

LTC6954-4:三个LVDS/CMOS输出

数据表:*附件:LTC6954低相位噪声、三路输出时钟分配分频器 驱动器技术手册.pdf

每个输出都可单独编程,以将输入频率除以1至63内的任何整数并将每个输出延迟0至63个输入时钟周期。输出占空比始终为50%,无论分频数如何。LVDS/CMOS输出通过OUTxSEL引脚跳线可选以提供LVDS逻辑输出或CMOS逻辑输出。

LTC6954还采用凌力尔特公司的EZSync系统,每次可实现出色的时钟同步和对齐功能。

所有器件设置均通过一个SPI兼容串行端口控制。

应用

- 为高速、高分辨率ADC、DAC和数据采集系统提供时钟

- 低抖动时钟分配

特性

- 低噪声时钟分配:适合于高速 / 高分辨率 ADC 计时

- 附加抖动 < 20fs

RMS(12kHz 至 20MHz) - 附加抖动 < 85fs

RMS(10Hz 至奈奎斯特频率) - 1.8GHz 最大输入频率 (LTC6954-1 - 当 DELAY = 0 时)

- 1.4GHz 最大输入频率 (LTC6954-1 - 当 DELAY > 0 时;LTC6954-2、3、4)

- 可兼容 EZSync^™^ 时钟同步

- 三个独立的低噪声输出

- 可提供 4 种输出组合

- 三个独立的可编程分频器覆盖了从 1 至 63 的所有整数

- 三种独立的可编程延迟覆盖了从 0 至 63 的所有整数

- -40°C 至 105°C 的结温范围

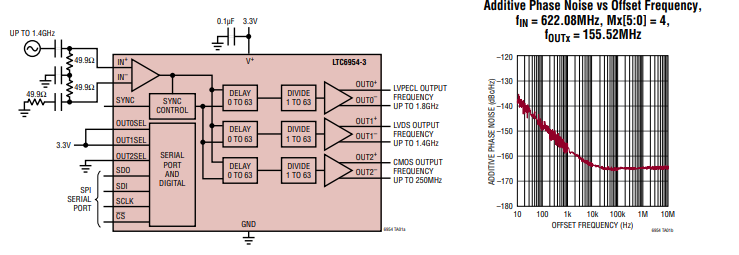

典型应用

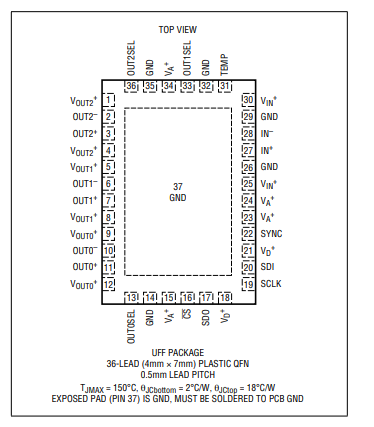

引脚图

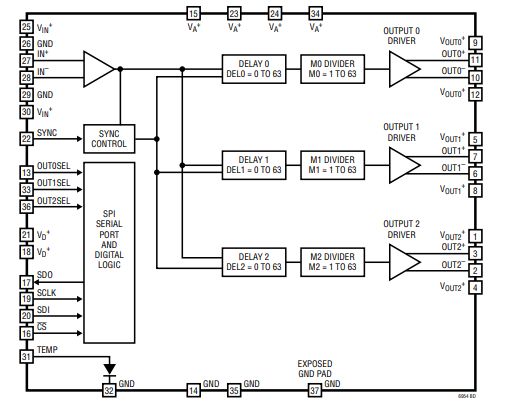

框图

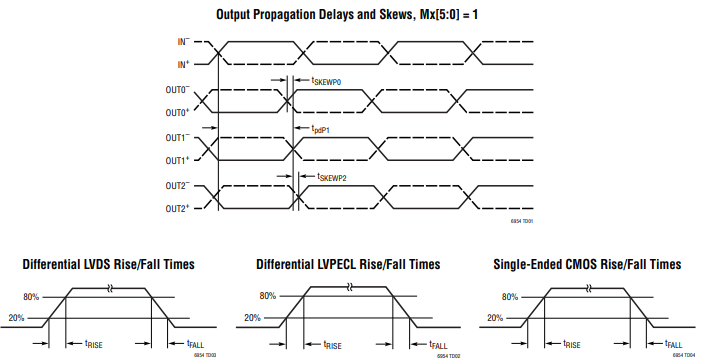

时序图

工作原理

LTC6954 简介

LTC6954 是一系列低相位噪声时钟分配器件。每个器件提供三个输出,每个输出都配有可编程频率分频器和延迟模块。该系列有四个型号,其输出逻辑信号类型有所不同:

- LTC6954 - 1 :三个低压正射极耦合逻辑(LVPECL)输出

- LTC6954 - 2 :两个 LVPECL 输出和一个低压差分信号/互补金属氧化物半导体(LVDS/CMOS)输出

- LTC6954 - 3 :一个 LVPECL 输出和两个 LVDS/CMOS 输出

- LTC6954 - 4 :三个 LVDS/CMOS 输出

如图 1 所示,LTC6954 由两个不同的电路部分组成:多输出时钟分配部分和数字控制部分。

LTC6954 的时钟分配部分接收一个输入信号,最高可达 1.4GHz(对于 LTC6954 - 1,当 DELx = 0 时为 1.8GHz),并在输出引脚上生成三个输出信号。输出信号逻辑类型取决于 LTC6954 的器件版本,以及 OUTxSEL 输出模式选择引脚的连接方式。图 1 展示了所有四个版本、每个版本可用的输出类型,以及 OUTxSEL 引脚连接对输出的影响。

LVPECL 逻辑输出能够在高达 1.4GHz 的频率下工作(对于 LTC6954 - 1,当 DELx = 0 时为 1.8GHz )。将 OUTxSEL 引脚连接到 V_{A}^{+} 电源可启用输出缓冲器的内部有源偏置。将此引脚连接到地则会禁用该内部电路。

LVDS/CMOS 输出可以是 CMOS 逻辑类型,也可以是 LVDS 逻辑类型,具体取决于 OUTxSEL 引脚的连接配置。将 OUTxSEL 引脚接地,可将输出配置为 CMOS 逻辑输出,其运行频率最高可达 250MHz。将 OUTxSEL 引脚连接到 V_{A}^{+} 电源,可将输出配置为 LVDS 逻辑输出,当 LVCSx 设置为 0 时(仅在远端终端时),运行频率最高可达 800MHz;当 LVCSx 设置为 1 时(两端都终端时),运行频率最高可达 1400MHz。有关更多详细信息,请参考“操作”和“应用信息”部分。

无论 LTC6954 的器件版本和输出逻辑配置如何,三个输出均各自可编程,可通过 1 至 63 之间的任意整数对输入频率进行分频,并可将任意输出延迟 0 至 63 个输入时钟周期。对于占空比为 50% 的输入信号,无论分频数值是多少,输出占空比始终为 50%。

数字控制部分包含一个完全兼容串行外设接口(SPI)的串行控制总线、三个输出模式选择引脚(OUT0SEL、OUT1SEL 和 OUT2SEL),以及 EZSync 时钟同步(SYNC)功能。大多数器件设置和工作模式都通过 SPI 总线进行控制。

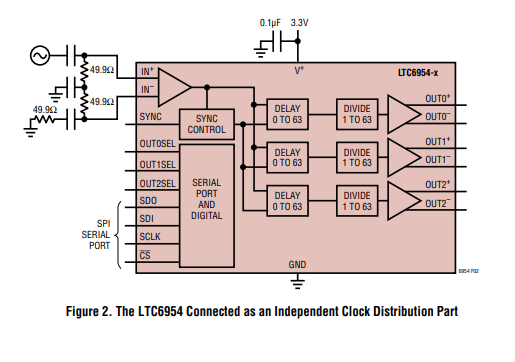

为将功耗降至最低,LTC6954 的许多部分在不使用时都可以断电。如图 2 所示,LTC6954 可用作独立的时钟分配部件。时钟分配部分的任何未使用输出均可断电。

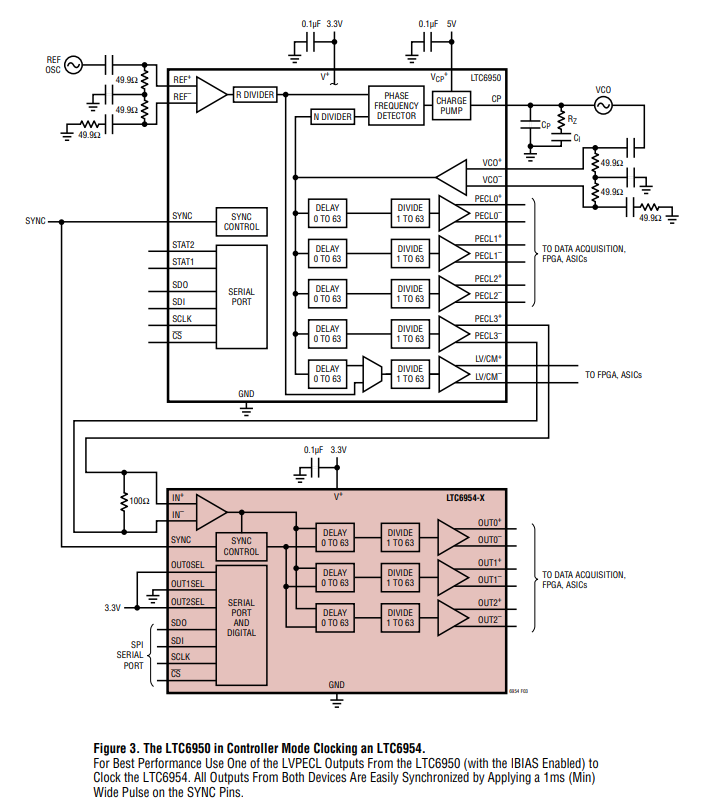

图 3 突出显示了 LTC6954 的一个示例。此示例展示了单个 LTC6954 器件,但 LTC6954 的每个输出都可以驱动一个独立的 LTC6954 器件,以支持多达五个 LTC6954 器件。轻松使用的 EZSync 时钟同步功能确保所有器件的所有输出的边沿始终保持一致对齐。有关 EZSync 工作原理的更多详细信息,请参见“EZSync 时钟输出同步”部分。

-

jf_47282988

2025-09-02

0 回复 举报你好,请问一下有后面详细的中文翻译资料吗 收起回复

jf_47282988

2025-09-02

0 回复 举报你好,请问一下有后面详细的中文翻译资料吗 收起回复

-

深入剖析 LTC6954:高性能时钟分配器的卓越之选2026-03-26 191

-

LTC6957系列:低相位噪声的双输出缓冲器/驱动器/逻辑转换器2026-01-07 370

-

AD9513 800MHz时钟分配IC,分频器,延迟调整,三路输出技术手册2025-04-15 1232

-

LTC6957低相位噪声、双输出缓冲器/驱动器/逻辑转换器技术手册2025-04-10 1401

-

LTC6954:低相位噪声、三输出时钟分布分频器/驱动器数据表2021-05-19 943

-

LTC6954 GUI2021-03-24 773

-

AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出2021-03-21 979

-

采用LTC6954-4低相位噪声三路输出时钟分配器/驱动器的演示电路DC1954A-D2019-02-21 2179

-

LTC6954 低相位噪声、三路输出时钟分配分频器 / 驱动器2019-02-15 660

-

超低抖动时钟分配解决方案 整合了 EZSync多芯片同步2015-11-24 5531

-

Hi-Fi三路有源分频器2009-11-27 2033

全部0条评论

快来发表一下你的评论吧 !