AD9528提供14路LVDS/HSTL输出的JESD204B/JESD204C时钟发生器技术手册

描述

概述

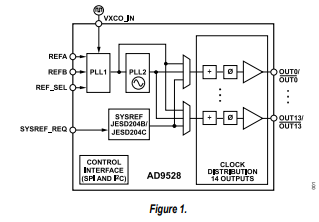

AD9528是一款双级PLL,集成JESD204B/JESD204C SYSREF发生器,可用于多器件同步。第一级锁相环(PLL) (PLL1)通过减少系统时钟的抖动,从而实现输入基准电压调理。第二级PLL (PLL2)提供高频时钟,可实现来自时钟输出驱动器的较低积分抖动以及较低宽带噪声。外部VCXO提供PLL2所需的低噪声基准电压,以满足苛刻的相位噪声和抖动要求,实现可以接受的性能。片内VCO的调谐频率范围为3.450 GHz至4.025 GHz。集成的SYSREF发生器输出单次、N次或连续信号,并与PLL1和PLL2输出同步,以便对齐多个器件的时间。

数据表:*附件:AD9528提供14路LVDS HSTL输出的JESD204B JESD204C时钟发生器技术手册.pdf

AD9528产生最高频率为1.25 GHz的六路输出(输出0至输出3、输出12和输出13),以及最大频率高达1 GHz的八路输出。每一路输出均可配置为直接从PLL1、PLL2或内部SYSREF发生器输出。14路输出通道的每一路都包含一个带数字相位粗调功能的分频器,以及一个模拟微调相位延迟模块,允许全部14路输出具有时序对齐的高度灵活性。AD9528还可用作灵活的双通道输入缓冲器,以便实现14路器件时钟和/或SYSREF信号的分配。启动时,AD9528直接向输出12和输出13发送VCXO信号,用作启动就绪时钟。

注意在整篇数据手册中,双功能引脚名称通过适用的相关功能来引用。

应用

- 高性能无线收发器

- LTE和多载波GSM基站

- 无线和宽带基础设施

- 医疗仪器

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟;支持JESD204B/JESD204C

- 低抖动、低相位噪声时钟分配

- 自动测试设备(ATE)和高性能仪器仪表

特性

- 14路输出,可配置为HSTL或LVDS

- 最大输出频率

- 6路输出高达1.25 GHz

- 8路输出高达1 GHz

- 取决于压控晶体振荡器(VCXO)频率精度(启动频率精度:<±100 ppm)

- 每路输出均提供专用的8位分频器

- 粗调延迟: 63个步长为RF VCO分频器输出频率一半的步进,不受抖动影响

- 微调延迟: 15个步进,分辨率为31 ps

- 典型输出间偏斜: 20 ps

- 针对奇数分频器设置提供占空比校正

- 输出12和输出13,上电时VCXO输出

- 绝对输出抖动: <160 f

S(122.88 MHz时)

12 kHz至20 MHz积分范围 - 数字锁频检测

- SPI和I^2^C兼容型串行控制端口

- 双PLL架构

- PLL1

- 利用外部VCXO实现参考输入时钟清零

- 鉴相器速率:最高110 MHz

- 冗余参考输入

- 自动和手动参考切换模式

- 恢复式和非恢复式切换

- 保持模式支持参考丢失检测

- VCXO提供的低噪声LVDS/HSTL输出可用于射频/中频(RF/IF)频率合成器

- PLL2

- 鉴相器速率:最高275 MHz

- 集成低噪声VCO

- PLL1

框图

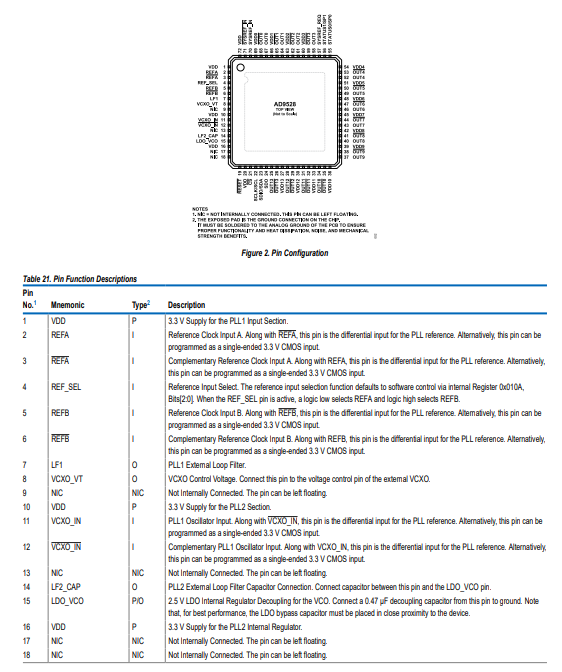

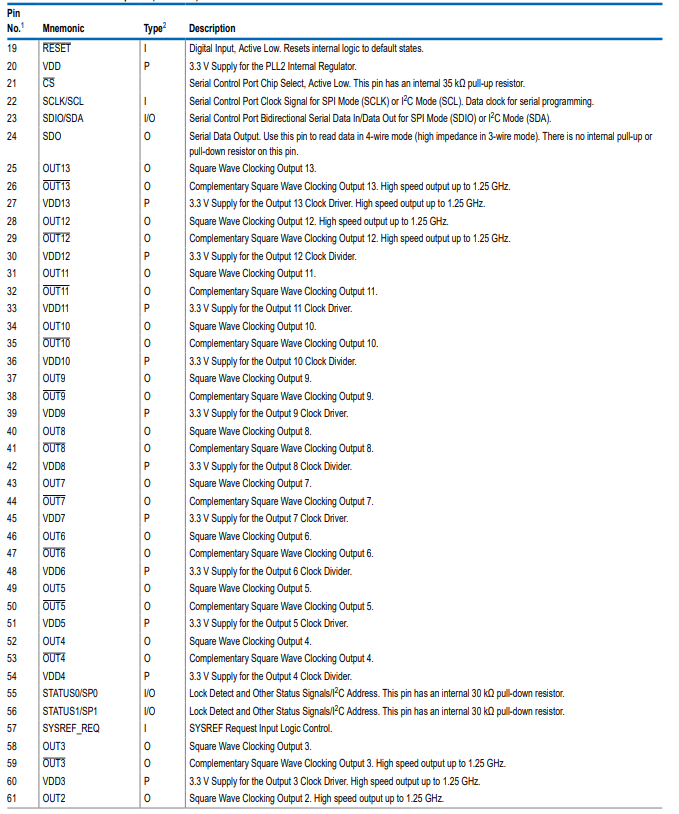

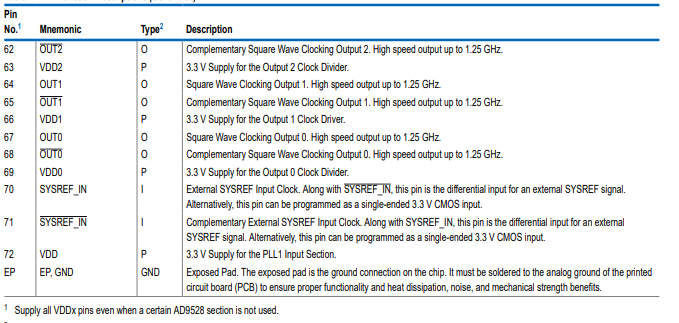

引脚配置描述

典型应用电路

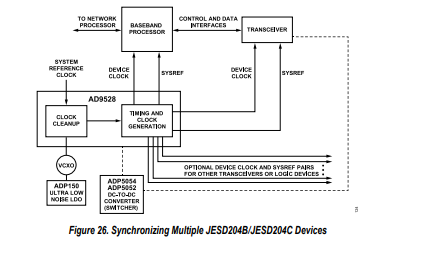

AD9258 能够同步多个符合 JESD204B/JESD204C 标准(联合电子设备工程委员会标准)的器件。图 26 展示了 AD9258 同步系统参考时钟的过程。AD9528 首先对系统参考时钟进行净化处理,然后在双环模式下将其倍频至更高频率。AD9528 的时钟分配功能用于为系统中所有周边的 JESD204B/JESD204C 器件提供时钟并使其同步。

器件初始化和校准流程图

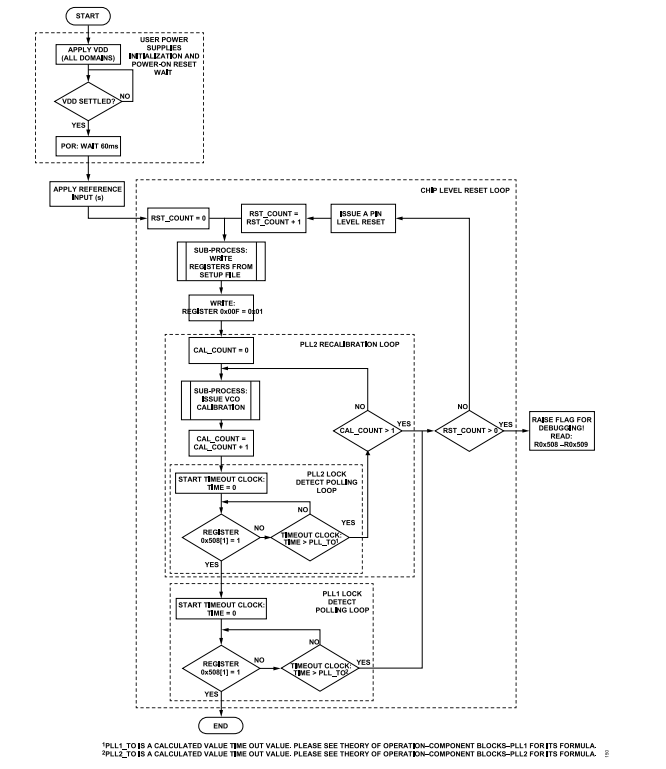

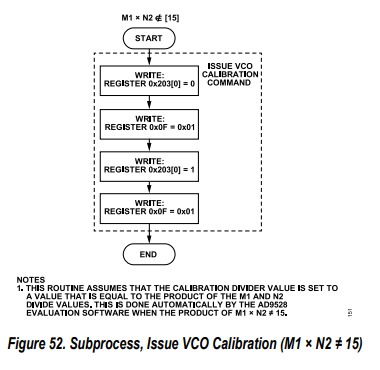

本节中的流程图展示了使用评估软件生成的设置文件(.stp)时,AD9528 典型的初始化例程,以及为实现稳健的系统启动而设计的校准例程。

图 51、图 52、图 53 和图 54 假定以下条件:压控振荡器(VCO)具有 ±100 ppm 的拉偏范围,且使用设置文件进行可靠的频率转换。这些流程图并非无限循环,芯片级复位循环的计数变量(RST_COUNT)和 PLL2 重新校准循环的计数变量(CAL_COUNT)是用于为循环设置计数上限的计数变量,这些变量仅适用于初始化过程。

-

AD9680 JESD204B接口的不稳定会导致较大的电流波动,怎么解决?2025-04-15 3135

-

JESD204B的系统级优势2018-09-18 2403

-

串行LVDS和JESD204B的对比2019-05-29 3169

-

JESD204标准解析2019-06-17 3391

-

JESD204B串行接口时钟的优势2019-06-19 3733

-

JESD204C的标准和新变化2021-01-01 3026

-

如何去实现JESD204B时钟?2021-05-18 3130

-

JESD204B协议介绍2022-11-21 943

-

JESD204B时钟发生器14输出ad9528数据表LVDS技术2017-10-19 1760

-

LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持数据表2021-04-22 1185

-

AD9528:具有14个LVDS/HSTL输出的JESD204B时钟发生器数据表2021-05-13 1075

-

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet2023-10-16 72

-

从JESD204B升级到JESD204C时的系统设计注意事项2024-09-21 1065

-

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册2025-04-16 1329

-

AD9528:高性能JESD204B/JESD204C时钟发生器的深度解析2026-03-23 167

全部0条评论

快来发表一下你的评论吧 !