AD9578双通道PLL精密频率合成器技术手册

描述

概述

AD9578是一款可编程频率合成器,可用于高性能电信、网络、数据存储、串行器/解串器(SERDES)和物理层(PHY)应用中的抖动衰减和异步时钟应用。 该器件集成两个能以超过0.1 ppb的精度提供任何频率的抖动PLL,每一个均带有两个独立的输出驱动器,总共四路可编程输出,提供极高的灵活性和抖动性能。 每路输出均独立可编程,提供高达919 MHz的频率,且典型rms抖动值低于410 fs(12 kHz至20 MHz),采用紧凑型低成本基频模式晶体(XTAL),具有稳定的供应链。 AD9578采用整数频率合成,可实现低至290 fs的rms抖动。

数据表:*附件:AD9578双通道PLL精密频率合成器技术手.pdf

AD9578封装采用出厂可编程默认上电配置。 上电后,包括输出频率在内的全部设置均可通过快速SPI重新配置。

AD9578的架构允许其用作数字控制振荡器(NCO)。 因此,用户可以使用快速SPI总线动态改变频率。FPGA和其他器件可以利用此功能来实现具有可配置环路带宽的数字PLL,用于抖动衰减应用、锁定至紧凑型稳定基准电压源的精密可驯时钟或数控精密时序应用,比如网络时序和IEEE 1588应用等。 SPI总线工作频率高达50 MHz,实现快速FPGA环路的同时让多器件共享同一个总线。AD9578还可用于多速率精密应用中,比如视频广播或OTN。 ADI公司提供用于数字PLL应用的HDL FPGA代码。

应用

- 基于FPGA的抖动衰减和低抖动PLL

- 精密可驯时钟和时钟频率合成器

- 多速率时钟频率合成器

- 光学: OTN/SDH/SONET

- 视频广播: 3G SDI、HD SDI、SDI

- 网络与存储: 以太网/SAS/光纤通道

- 无线基础设施: OBSAI/CPRI

- 工业: IEEE 1588

- 数控振荡器(NCO)

特性

- 任意输出频率的精密频率合成

- 11.8 MHz至 919 MHz

- 频率分辨率超过0.1 ppb

- 超低rms抖动(12 kHz至20 MHz)

- 使用整数频率合成:<300 fs rms

- 使用小数频率合成:<405 fs rms

- 双基准电压输入支持LVPECL、LVDS、1.8 V LVCMOS、基频模式AT切割晶体(22 MHz至54 MHz)或基准电压源时钟(20 MHz至60 MHz)

- 数字(NCO)频率控制l

- 动态可牵引输出频率实现基于FPGA的PLL(提供HDL)

- 快速串行外设接口(SPI)总线写入速度高达100 MHz

- 可即时更改频率

- 集成双PLL,采用7 mm × 7 mm紧凑型封装

- 可代替多个大型时钟IC、PLL、扇出缓冲器、晶体振荡器(XO)和压控晶体振荡器(VCXO)

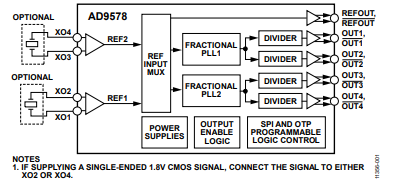

简化功能框图

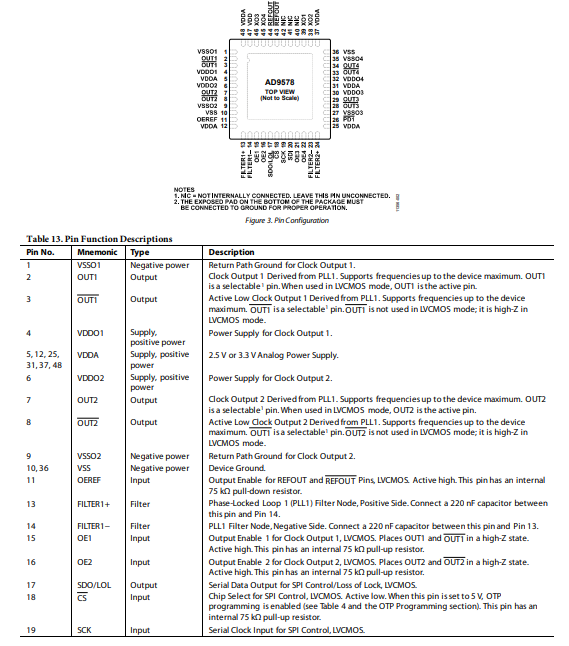

引脚配置描述

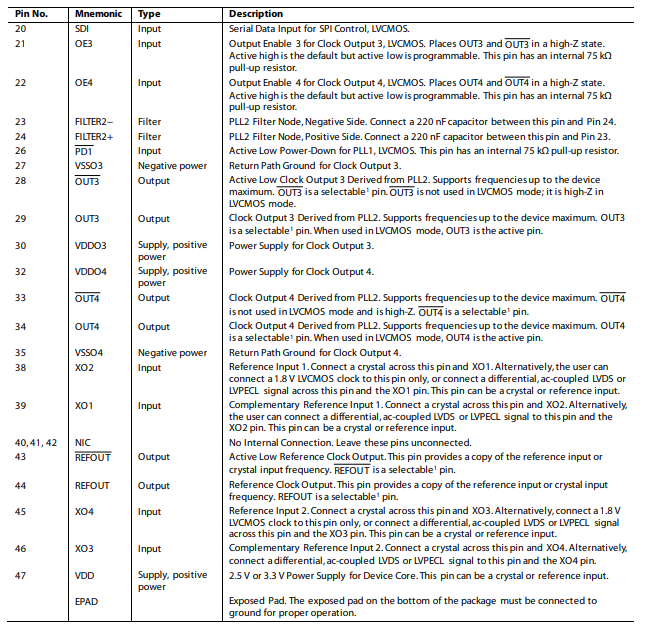

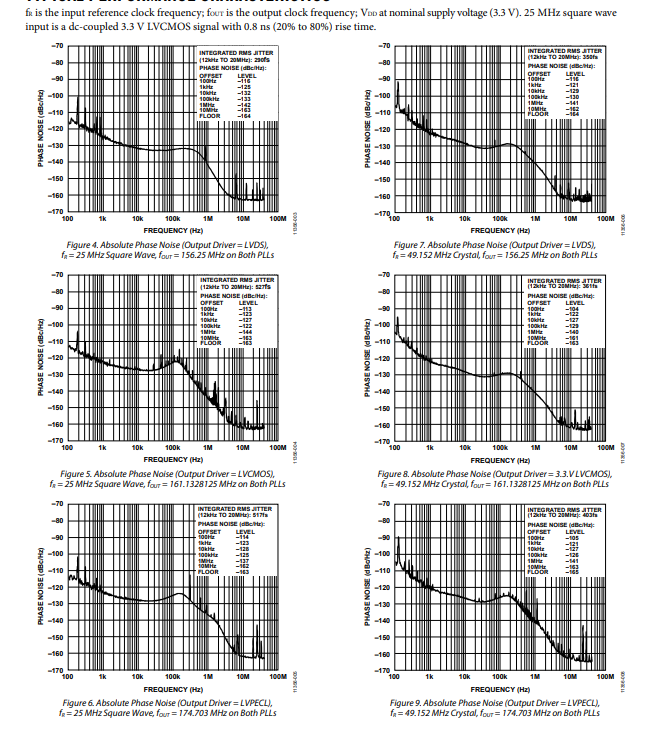

典型性能特征

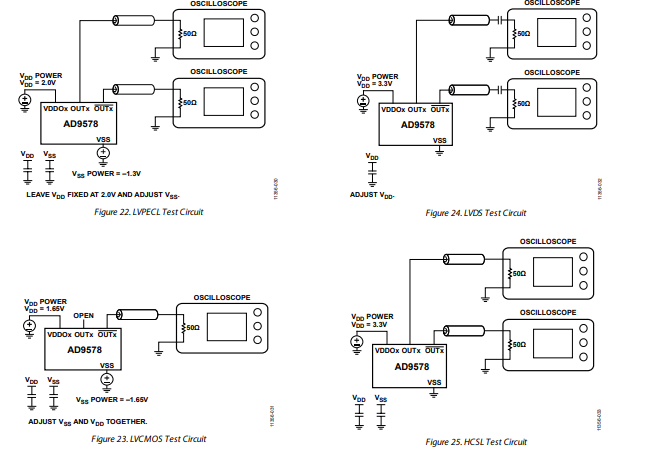

测试设置和配置电路

操作理论

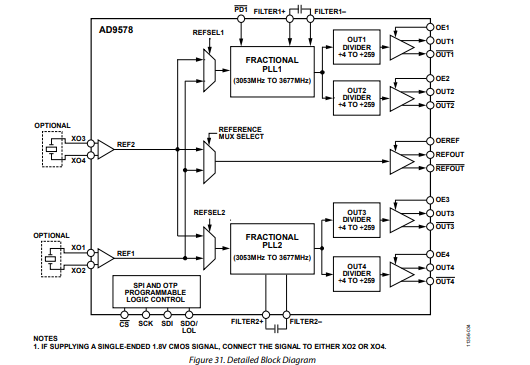

AD9578 是一款双合成器,具备四个可编程输出。两个锁相环(PLL),可采用晶体或外部参考输入频率,能产生多达四种独特的输出频率。每个输出上的输出格式标准包括低压互补金属氧化物半导体(LVCMOS)、低压差分信号(LVDS)、低压正射极耦合逻辑(LVPECL)和高速电流模式逻辑(HCSL)。晶体输入具有低功耗休眠模式,并且 AD9578 提供可编程增益和负载电容。此外,可将内部基准时钟用作任一或两个锁相环的参考时钟。晶体或外部参考频率可按需选用。

锁相环独立运行,但可共享输入参考(若需要)。存在三种操作模式可供选择:整数模式、分数模式和比率模式。整数模式能提供最低噪声,并具备类似传统整数锁相环的整体数字分频器。分数模式采用 8 位整数部分和 28 位小数部分,从而实现基于 0.1 ppm 或更佳的频率分辨率的频率合成。旋转波振荡器(RTWO)可在 3053 MHz 至 3677 MHz 的速率下运行,以实现分数模式,同时允许用户指定反馈分频器的比率(以一个整数除以另一个整数的形式表示)。每个压控振荡器(VCO)上有两个输出,频率范围为 750.8 MHz 至 259.2 MHz,还包含 4.5 模式下的频率间隔。任何输出频率通过 11.8 MHz 和 919 MHz 的分频可产生频率误差为 0.1 ppb 或更佳的频率。

该器件具备额外特性,包括低相位噪声、小频率步进下输出频率的平滑变化,以及通过串行外设接口(SPI)进行控制。AD9578 可通过 SPI 进行配置,也可通过 SPI 命令进行组合编程,用户可对其进行全面控制。AD9578 具备默认功率配置,可在开机时自动编程。所有设置均可在加电后通过 SPI 重新编程。

典型情况下,锁相环带宽设置为 300 kHz,锁相环跟踪并将参考相位噪声乘以晶体输入提供的多个低相位噪声参考,从而在输出相位噪声接近载波时实现低相位噪声。选择参考时,确保参考输入的相位噪声足够低,以满足系统噪声要求。

-

基于DDS的频率合成器设计介绍2019-07-08 3030

-

如何利用FPGA设计PLL频率合成器?2019-07-30 4556

-

什么是PLL频率合成器?2019-09-17 5343

-

1.3GHz双通道频率合成器2009-09-02 799

-

DDS PLL短波频率合成器设计2009-09-07 626

-

多通道频率合成器应用得益于精密频率合成技术2009-12-24 1475

-

采用PLL的频率合成器电路图2009-07-20 1385

-

双锁相环精密合成器ad9578数据表2017-10-19 910

-

AD9578 双通道PLL精密频率合成器2019-02-15 566

-

UG-161:PLL频率合成器评估板2021-03-20 1029

-

ADF4212L:双低功耗PLL频率合成器数据表2021-04-22 808

-

ADF4206/ADF4208:双射频PLL频率合成器数据表2021-04-26 832

-

AD9578:双锁相环精密合成器数据表2021-05-13 780

-

pll频率合成器工作原理与pll频率合成器的原理图解释2023-02-24 11788

-

ADF4212L双通道、低功耗PLL频率合成器技术手册2025-04-27 1117

全部0条评论

快来发表一下你的评论吧 !