AD9554-1四路PLL、四通道输入、四通道输出多服务线路卡自适应时钟转换器技术手册

描述

概述

AD9554-1是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。 AD9554-1产生的输出时钟可以与多达四路外部输入参考时钟同步。 DPLL可以降低与外部参考时钟相关的输入时间抖动或相位噪声。 借助数字控制环路和保持电路,即使所有参考输入都失效,AD9554-1也能持续产生低抖动输出时钟。

AD9554-1的工作温度范围为−40℃至+85℃工业温度范围。如需该器件的单DPLL版本,请参考AD9557或AD9559。

数据表:*附件:AD9554-1四路PLL、四通道输入、四通道输出多服务线路卡自适应时钟转换器技术.pdf

应用

- 网络同步,包括同步以太网和SDH至OTN映射/解映射

- 清除基准时钟抖动

- 最高达到OC-192的SONET/SDH时钟,包括FEC

- Stratum 3保持、抖动清除及相位瞬态控制

- 无线基站控制器

- 有线基础设施

- 数据通信

- 专业视频设备

特性 - 在保持模式下稳定性支持GR-1244 Stratum 3

- 支持平稳的参考切换,几乎不会干扰输出相位

- 支持Telcordia GR-253抖动产生、转换和容差,适用于SONET/SDH至OC-192系统

- 支持ITU-T G.8262同步以太网从时钟

- 支持ITU-T G.823、G.824、G.825和G.8261

- 自动/手动保持和参考切换

- 自适应时钟可动态调整反馈分频器,用于OTN映射/解映射应用

- 四通道数字PLL架构,带四个基准输入电压(单端或差分)

- 4x4交叉点允许任意基准输入驱动任意PLL

- 输入参考频率范围:2 kHz至1000 MHz

- 参考验证和频率监控:2 ppm

- 可编程设置输入参考的切换优先级

- 20位可编程输入参考分频器

- 4路差分时钟输出,每个差分对均可配置为HCSL、LVDS兼容或LVPECL兼容

- 输出频率范围:430 kHz至941 MHz

- 数字PLL集成可编程18位整数和24位小数反馈分频器

- 可编程环路带宽:0.1 Hz至4 kHz

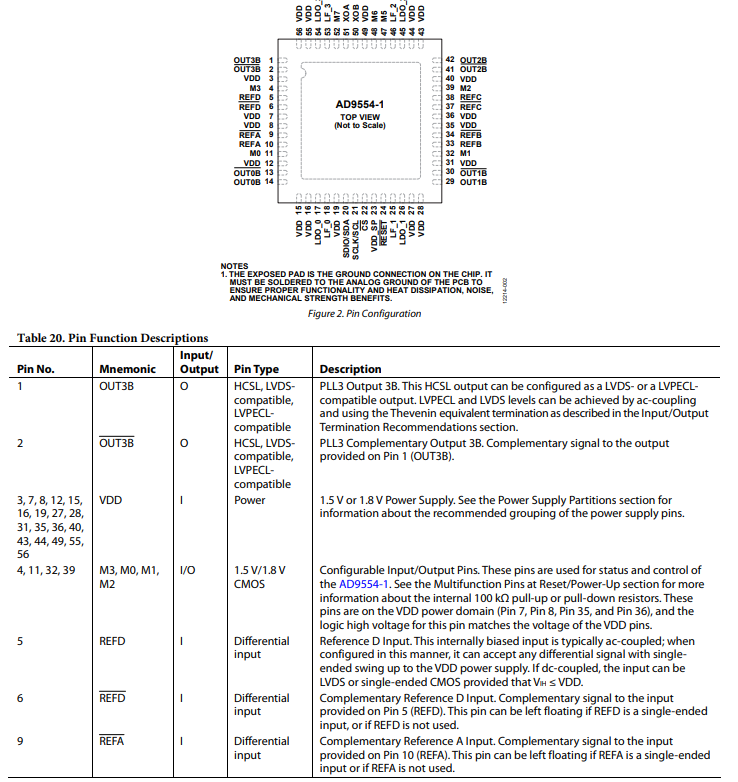

- 56引脚(8 mm x 8 mm) LFCSP封装

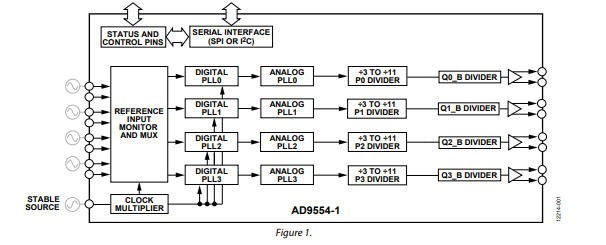

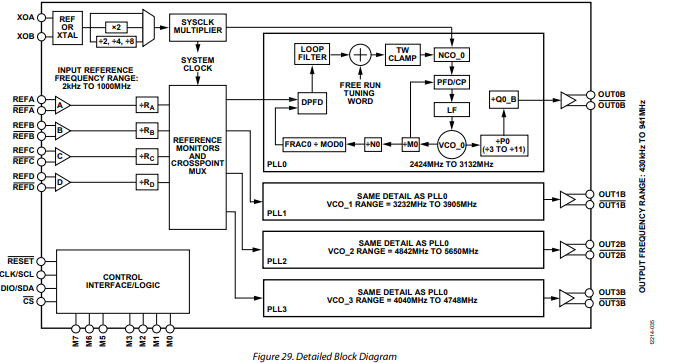

框图

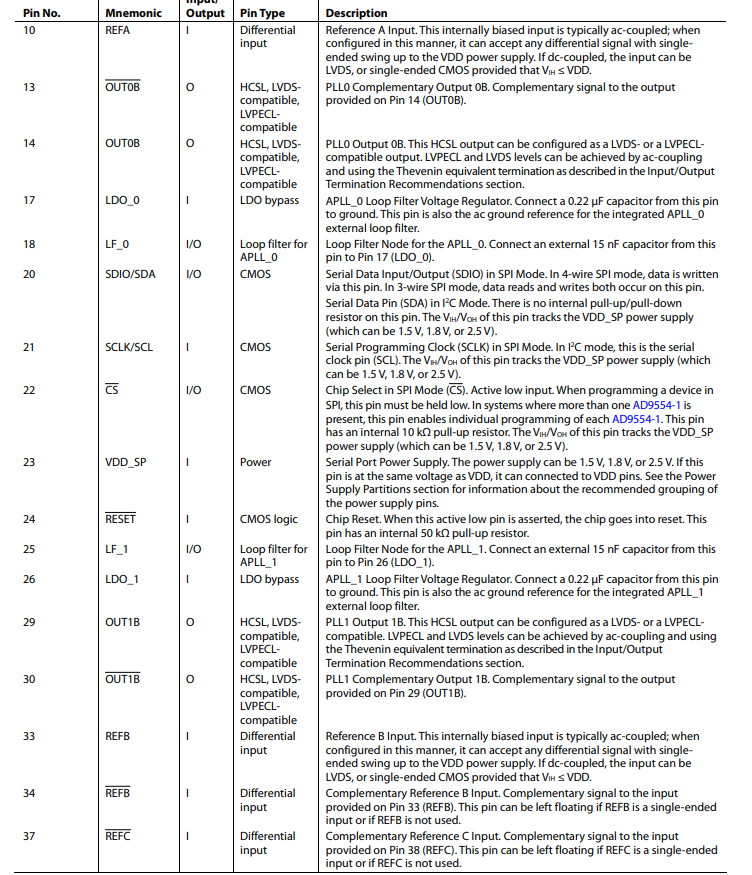

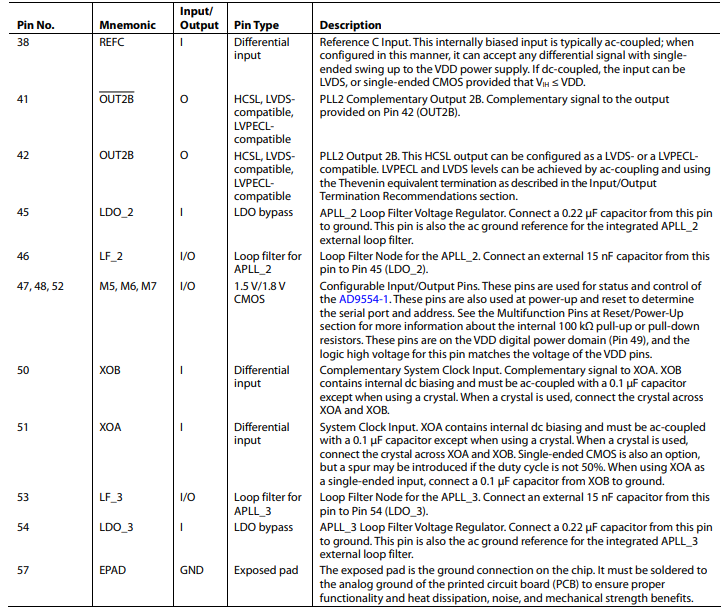

引脚配置描述

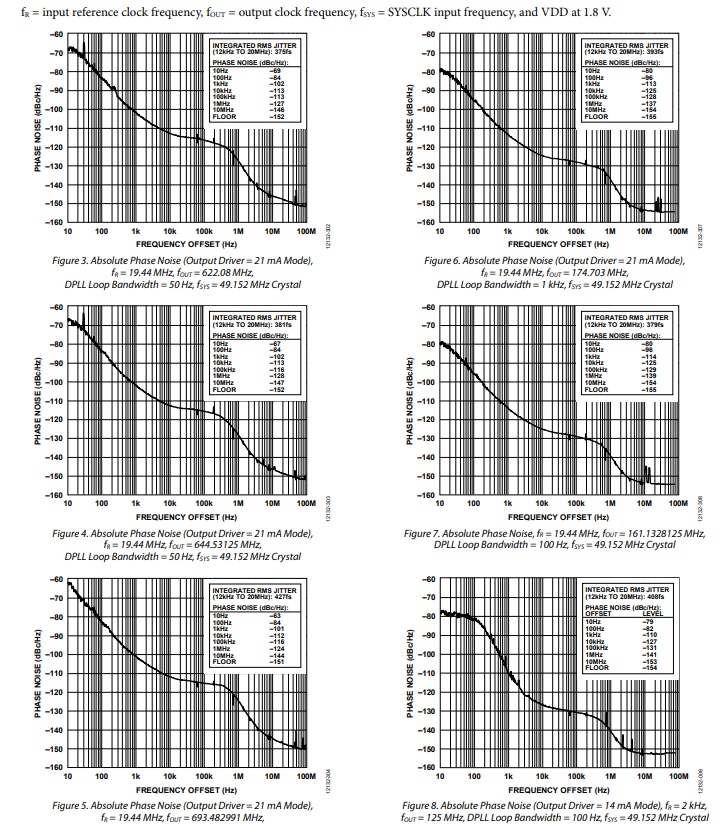

典型性能特征

操作理论

AD9554 - 1 提供的时钟输出与所选(活动)参考信号的相位和频率直接相关,但其抖动特性由系统时钟、数字控制振荡器(DCO)和模拟输出锁相环(APLL)决定。AD9554 - 1 可被视为 AD9557 的四个副本封装在一起,具有 4:4 交叉点控制的参考输入。AD9554 - 1 支持多达 4 个参考输入,输入频率范围从 2 Hz 到 1000 MHz。该器件的核心是四个数字锁相环(DPLL)。每个 DPLL 都有一个可编程数字积分器环路滤波器,可大幅减少从活动参考信号转移到输出的抖动,并且这四个 DPLL 完全相互独立运行。

AD9554 - 1 具备手动和自动备用功能。在备用模式下,只要系统时钟存在,AD9554 - 1 就会持续提供输出,输出频率为输出频率在备用条件之前的时间平均值。该器件还提供手动和自动参考切换功能,当活动参考信号降级或完全失效时可进行切换。AD9554 - 1 还具有自适应时钟功能,允许用户在 DPLL 锁定时动态更改 DPLL 分频比。

AD9554 - 1 包含一个系统时钟乘法器、四个 DPLL 和四个 APLL。输入信号首先进入 DPLL,DPLL 执行抖动清除操作,并将大部分频率传递给 APLL。每个 DPLL 都配备一个 30 位至 31 位的 DCO,可在 283 MHz 至 345 MHz 的范围内生成信号。DCO 的输出进入 APLL,APLL 将信号倍频至 2.4 GHz 至 5.6 GHz,然后将该信号发送到时钟分配部分,该部分由一个 P 分频器与 10 位通道分频器(1 分频至 1024 分频)级联组成。

XOA 和 XOB 输入为系统时钟提供参考。这些引脚可接受 10 MHz 至 268 MHz 范围内的参考时钟,或直接连接在 XOA 和 XOB 输入两端的 10 MHz 至 50 MHz 晶体。系统时钟为频率监视器、DPLL 和内部切换逻辑提供时钟。

AD9554 - 1 的每个 APLL 都有一个差分输出驱动器。每个输出驱动器都有一个专用的 10 位可编程后置分频器。每个差分驱动器的工作频率高达 1.25 GHz,采用 HCSL 驱动器,内部有 58 Ω 终端电阻,具有三种驱动强度:

- 14 mA 模式用于 HCSL 和交流耦合 LVDS。用作 LVDS 兼容驱动器时,必须进行交流耦合,并在差分对两端跨接一个 100 Ω 电阻。

- 28 mA 模式产生电压摆幅,与 LVPECL 兼容。如果需要 LVPECL 信号电平,设计者必须交流耦合 AD9554 - 1 输出。

- 21 mA 模式介于上述两种设置之间。

AD9554 - 1 还包括一个去阻尼控制功能,允许用户通过周期性写入实际电平以及所需的初始电平(先出(FIFO))来动态调整 AD9554 - 1 的每个输出频率,以匹配用户系统上的实际电平。

-

四通道示波器2014-08-26 15069

-

在Multisim平台中使用四通道示波器问题2018-11-21 13065

-

多业务线卡自适应时钟转换器评估板AD9554/PCBZ2019-02-22 1799

-

BTS721L1四通道开关转换器相关资料下载2021-04-26 1866

-

AD9144,AD9148,AD9177的四通道输出都可以四路同步输出吗?2023-12-01 666

-

MAX9530 四通道NTSC/PAL解码器和四通道音频编码2010-10-02 2178

-

四通道PWM输出实验2017-07-30 1482

-

AD9554 四路PLL、四通道输入、八通道输出多服务线路卡自适应时钟转换器2019-02-15 2721

-

ADAU1978:四通道模数转换器(ADC)2021-03-19 1272

-

ADAU1979:四通道模数转换器(ADC)2021-03-20 1331

-

AD9557:双路输入多服务线路卡自适应时钟转换器2021-03-21 658

-

AD9554-1:四路PLL、四路输入、多服务线路卡自适应时钟转换器产品手册2021-05-08 688

-

AD9559:双PLL、四输入、多服务线路卡自适应时钟转换器产品手册2021-05-26 697

-

AD9554四路PLL、四通道输入、八通道输出多服务线路卡自适应时钟转换器技术手册2025-04-10 1210

-

AD9554:高性能多服务线路卡自适应时钟转换器2026-03-23 150

全部0条评论

快来发表一下你的评论吧 !