LTC6957低相位噪声、双输出缓冲器/驱动器/逻辑转换器技术手册

描述

概述

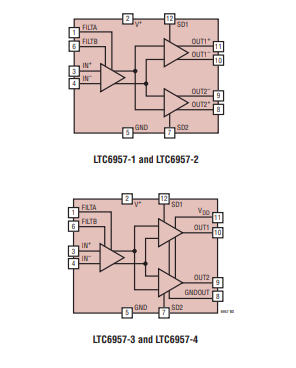

LTC 6957-1 / LTC6957-2 / LTC6957-3 / LTC6957-4 是一个非常低相位噪声、双输出 AC 信号缓冲器 / 驱动器 / 逻辑电平转换器系列。输入信号可以是一个正弦波或任何逻辑电平 (≤ 2V P-P )。该系列包括以下 4 个具有不同输出逻辑信号类型的成员:

LTC6957-1:LVPECL 逻辑输出

LTC6957-2:LVDS 逻辑输出

LTC6957-3:CMOS 逻辑,同相输出

LTC6957-4:CMOS 逻辑,互补型输出

数据表:*附件:LTC6957低相位噪声、双输出缓冲器 驱动器 逻辑转换器技术手册.pdf

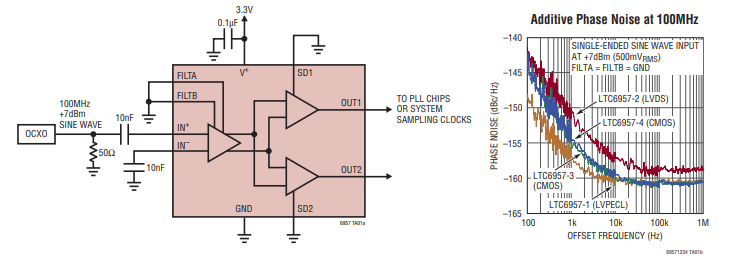

LTC6957 将以极低的附加噪声进行任何逻辑信号的缓冲和分配,不过,在把正弦波信号转换为逻辑电平方面,该器件相比于同类产品确实更胜一筹。初始放大级具有可选的低通滤波,以较大限度地抑制噪声,同时仍然对信号实施放大以增加其摆率。当采用缓慢摆率的输入信号 (例如:一个典型的 10MHz 正弦波系统基准) 时,该输入级滤波 / 噪声限制特别有助于提供相位噪声尽可能低的信号。

应用

- 系统基准频率分配

- 高速 ADC、DAC、DDS 时钟驱动器

- 军事和安全无线电

- 低噪声定时触发器

- 宽带无线收发器

- 高速数据采集

- 医学成像

- 测试和测量

特性

- 低相位噪声缓冲器 / 驱动器

- 正弦波信号至逻辑电平的优化转换

- 可提供 3 种逻辑输出类型

- LVPECL

- LVDS

- CMOS

- 附加的抖动:45fs

RMS(LTC6957-1) - 频率范围高达 300MHz

- 3.15V 至 3.45V 电源操作

- 低摆率 3ps (典型值)

- 全面规格在 –40°C 至 125°C

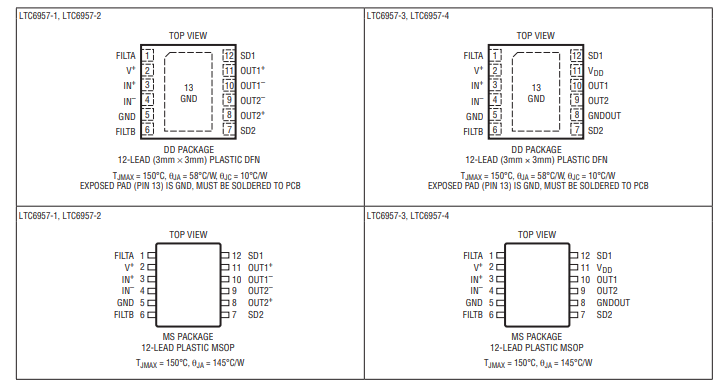

- 12 引脚 MSOP 封装和 3mm x 3mm DFN 封装

典型应用

引脚配置

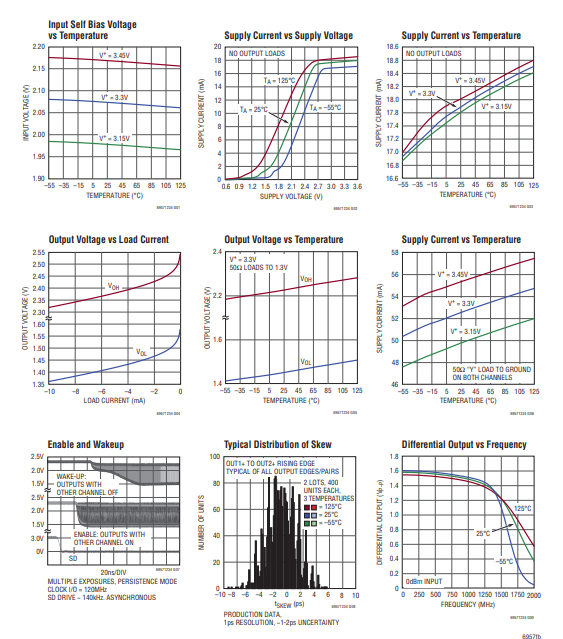

典型性能特征

框图

应用信息

一般注意事项

LTC6957 - 1/LTC6957 - 2/LTC6957 - 3/LTC6957 - 4 是低噪声双输出时钟缓冲器,专为要求严苛的低相位噪声应用而设计。正确使用时,它们可以在其他解决方案会显著降低相位噪声的情况下保持相位噪声性能。它们也可用作逻辑转换器。

然而,没有缓冲器设备能够消除或减少输入信号中存在的相位噪声。与大多数低相位噪声电路一样,LTC6957 - 1/LTC6957 - 2/LTC6957 - 3/LTC6957 - 4 的不当应用可能会由于多种机制导致相位噪声性能下降。以下信息有望帮助设计人员避免出现这种情况。

LTC6957 旨在与用于驱动模数转换器 (ADC) 或混频器输入的高性能时钟信号配合使用。此类时钟信号不应被视为数字信号。理想数字逻辑的优势在于,在出现任何有害影响之前,其电压和定时方面都存在噪声裕量。相比之下,高性能时钟信号没有误差噪声裕量。在系统性能下降之前的定时方面也是如此。建议用户在设计LTC6957之前、期间和之后的整个时钟信号链时牢记这一区别。

输入接口

LTC6957的所有版本的输入级都是相同的,其设计目的是实现低噪声,并便于与正弦波和小幅度信号接口。其他逻辑类型可以轻松接口,因为它们对噪声抑制的挑战较小。

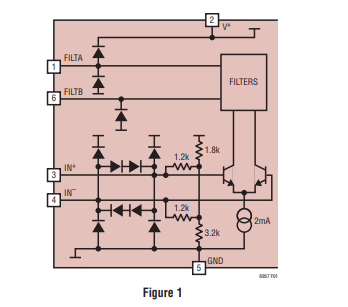

图1显示了LTC6957输入级的简化示意图。这些二极管用于在静电放电(ESD)事件期间提供保护,并防止低噪声NPN器件因输入过压而损坏。

偏置电阻将输入级偏置在最佳直流电平,但如果不增加噪声,它们不能悬空。因此,为实现低噪声,务必在未使用的输入上连接一个交流阻抗的接地回路。

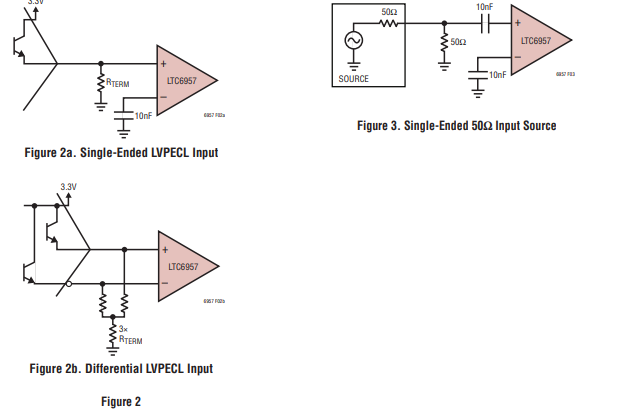

图2a展示了单端LVPECL逻辑与LTC6957的接口方式,而图2b则展示了如何用差分LVPECL信号驱动LTC6957。图中所示的电容为10nF,且价格可能较高,最好采用小型表面贴装(SMT)封装。对于100MHz以上的应用,可能需要使用较低容值的电容,以避免在图2a中出现谐振,因为即使电容仅连接在直流输入上,也可能会增加噪声。此说明适用于整个数据手册中连接到输入端的所有电容。

在图2a中,R_{TERM}的实现方式由用户决定,目的是对传输线进行端接。如果将其连接到V_T电压,并通过大电容旁路接地,那么在反相LTC6957输入端所示的10nF接地电容就是合适的连接方式。然而,如果端接方式是主动产生V_T电压,那么将反相输入端的电容连接到V_T而非接地,可能会实现更低的噪声。

在图2b中,LTC6957的两个输入端都被驱动,这样增大了差分输入信号幅度,并且将来自任何共模源(如V_T)的噪声影响降至最低,从而改善了相位噪声。

可以使用多种端接技术,只要两端采用相同的端接方式,配置就不会有太大差异。在图2b中,电阻端接采用Y形配置,在公共点产生一个无源V_T。大多数3.3V LVPECL器件具有差分输出,可以用三个50Ω电阻进行端接,如图所示。

图3展示了一个50Ω射频信号源与LTC6957的接口。对于纯正弦波输入,图3中的配置可处理高达10dBm(最大值)的输入信号。一个宽带50Ω匹配网络对于大多数应用来说应该就足够了,不过对于小幅度输入信号,窄带电抗匹配网络可能会在性能上带来一些提升。

-

凌力尔特推出DC至300MHz的双输出缓冲器/驱动器/逻辑转换器LTC69572013-04-09 1968

-

采用LTC6954-4低相位噪声三路输出时钟分配器/驱动器的演示电路DC1954A-D2019-02-21 2179

-

采用LTC6957-3低相位噪声的演示板DC1766A-B2019-02-22 3242

-

LTC6957的典型应用是一系列极低相位噪声2019-07-17 3866

-

请问LTC6957可以用作比较器吗?2023-11-14 513

-

LTC6957 低相位噪声、双输出缓冲器 / 驱动器 / 逻辑转换器2019-02-15 930

-

LTC6957-1/LTC6957-2/LTC6957-3/LTC6957-4:低相位噪声、双输出缓冲器/驱动器/逻辑转换器数据表2021-04-16 878

-

LTC6957-低相位噪声参考缓冲器/逻辑转换器2021-04-28 831

-

LTC6954:低相位噪声、三输出时钟分布分频器/驱动器数据表2021-05-19 942

-

LTC6417:1.6 GHz低噪声高线性度差分缓冲器/16位ADC驱动器,带快速钳位数据表2021-05-23 903

-

低相位噪声、双输出AC信号缓冲器/驱动器/逻辑电平转换器系列2022-09-26 1491

-

双缓冲器/线路驱动器;三态-XC7WH1262023-02-20 523

-

具有开漏输出的双缓冲器/驱动器数据表2024-05-22 456

-

CDC3RL02低相位噪声双通道时钟扇出缓冲器数据表2024-08-20 579

-

LTC6957系列:低相位噪声的双输出缓冲器/驱动器/逻辑转换器2026-01-07 357

全部0条评论

快来发表一下你的评论吧 !