AD9508 1.65GHz时钟扇出缓冲器,集成输出分频器和延迟调整技术手册

描述

概述

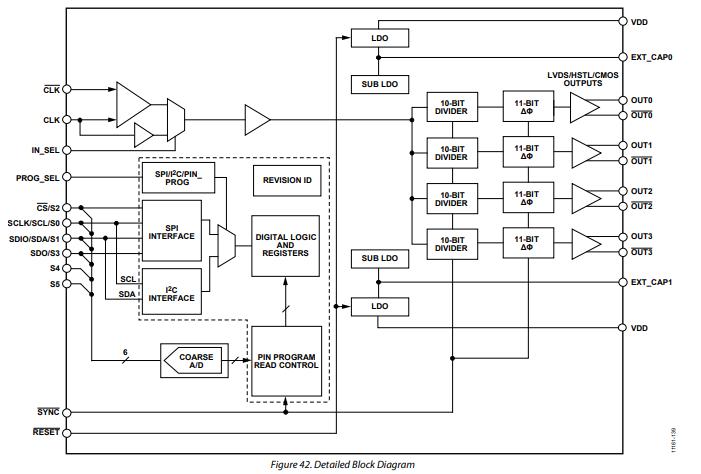

AD9508提供时钟扇出能力,针对能使系统性能达到优质的低抖动进行设计。这款器件能满足时钟数据转换器等应用所需的相位噪声和低抖动要求,可优化这些应用的性能。

数据表:*附件:AD9508 1.65GHz时钟扇出缓冲器,集成输出分频器和延迟调整技.pdf

它集成4个独立的差分时钟输出,每一个输出都支持多种逻辑电平类型。包括LVDS (1.65 GHz)、HSTL (1.65 GHz)和1.8 V CMOS (250 MHz)。在1.8 V CMOS输出模式下,差分输出转换为两个CMOS单端信号。无论工作电源电压如何改变,CMOS输出始终为1.8 V逻辑电平。

每路输出都有一个可编程分频器,可以旁路该分频器或者设置最高1024的整数分频比。此外,AD9508还支持输出相位在输出之间进行粗调。

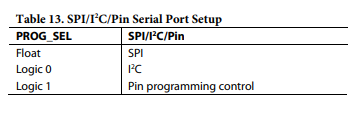

上电时,还可对器件进行各种固定配置的引脚编程,从而无需进行SPI或I^2^C编程。

AD9508提供24引脚LFCSP封装,可以采用2.5 V或3.3 V单电源供电。温度范围为−40°C至+85°C。

应用

- 低抖动、低相位噪声时钟分配

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 高性能仪器仪表

- 宽带基础设施

特性

- 1.65 GHz差分时钟输入/输出

- 10位可编程分频器,1至1024整数分频比

- 高达4个差分输出或8个CMOS输出

- 用于上电时进行硬连线编程的引脚绑定功能

- 宽带随机抖动:<115 fs rms

- 加性输出抖动:41fs rms(12 KHz至20 MHz)

- 出色的输出间隔离

- 所有输出自动同步

- 欲了解更多特性,请参考数据手册

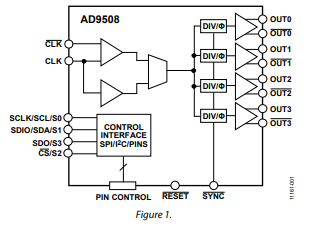

框图

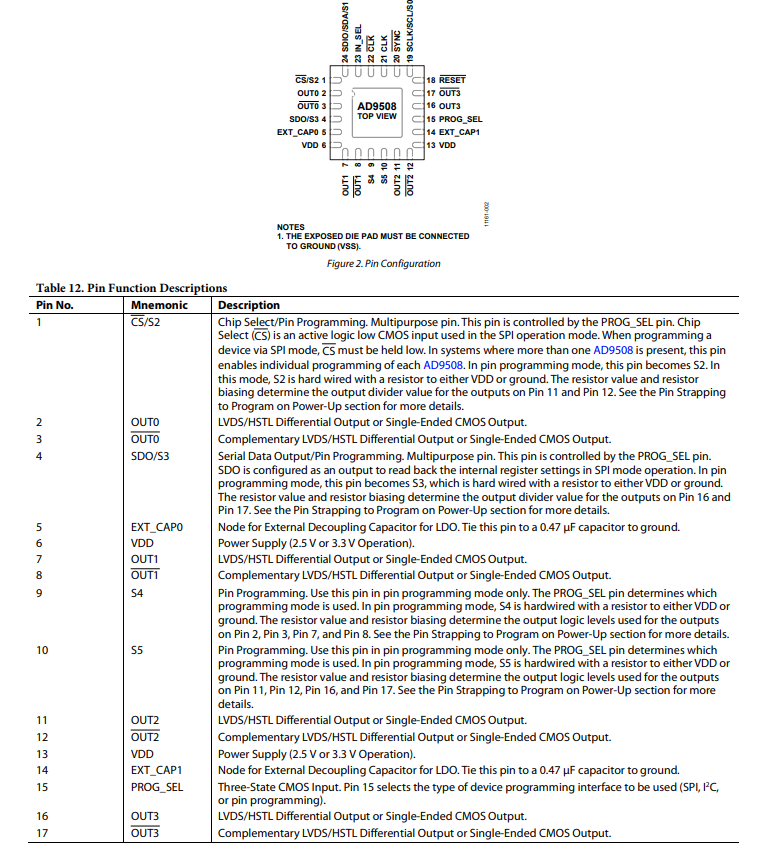

引脚配置描述

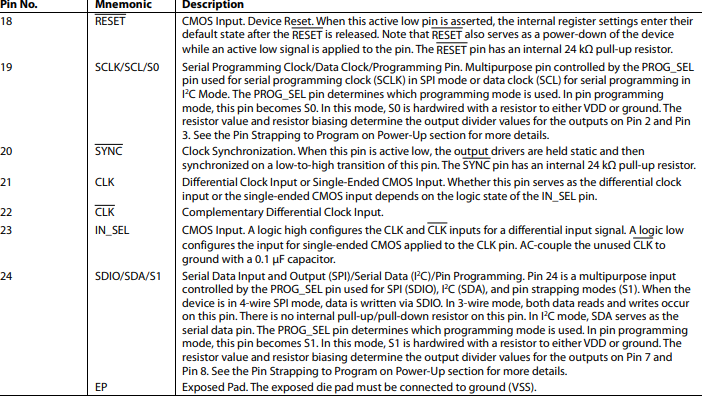

典型性能特征

操作理论

编程模式选择

AD9508 可以接受施加到CLK和**overline{CLK}**引脚的差分输入时钟,或者单端1.8V(交流耦合)、2.5V 或 3.3V CMOS 时钟(施加到CLK引脚)。输入时钟信号是时钟分配部分的输入,该部分具有可编程分频器和相移调整功能。时钟分配部分的工作频率最高可达1650MHz。

在SPI或**I^{2}**C控制模式下,分频器范围为1到1024,相移调整的分辨率为11位。然而,在引脚编程模式下,分频器范围限制为最大16分频,并且无相移调整功能。

输出可配置为多达四个LVDS/HSTL差分输出,或多达八个1.8V CMOS单端输出。此外,不同输出的输出电流可针对输出驱动强度进行调整。

该器件可由3.3V或2.5V外部电源供电;不过,芯片上的内部电源由一个1.8V LDO供电,从而在功耗最低的情况下实现高性能。

AD9508支持SPI和**I^{2}**C协议,并且可以通过引脚连接选择对器件进行编程。活动接口取决于PROG_SEL引脚的逻辑状态。有关编程模式选择的详细信息,请参见“串行控制端口”和“加电时引脚连接编程”部分。

时钟输入

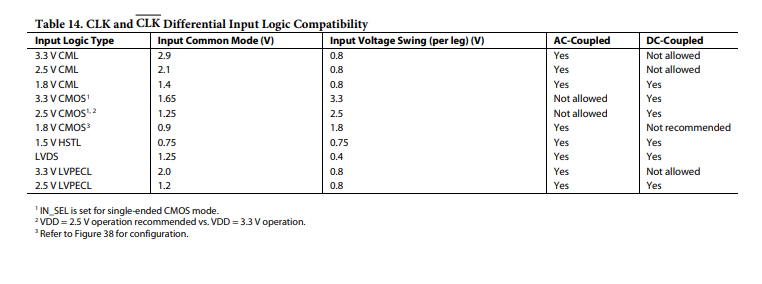

IN_SEL引脚用于控制所需的输入时钟配置。当IN_SEL引脚设置为单端输入模式时,器件期望在CLK引脚上接收到1.8V(交流耦合)、2.5V或3.3V CMOS兼容逻辑电平。将未使用的**overline{CLK}**引脚通过0.1μF电容旁路接地。

请注意,如果使用2.5V逻辑电平作为单端输入时钟模式,建议选择2.5V电源选项,而非3.3V电源,以避免可能出现的占空比失真。当3.3V工作模式下的开关阈值电平(VDD/2或1.65V)升高且输入信号缓慢上升并在阈值处下降时,可能会出现占空比失真。

不建议在单端CMOS逻辑配置中使用1.8V CMOS逻辑电平,这是因为输入阈值电压的变化过大。不过,差分输入时钟模式可用于1.8V CMOS输入,图38展示了1.8V CMOS输入时钟的推荐配置。

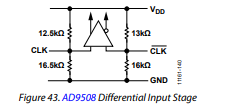

当IN_SEL引脚设置为差分输入时钟模式时,AD9508的输入内部自偏置。内部输入有一个电阻分压器,其共模电平比实际输入信号的共模电平低约30mV,以避免在输入信号停止时输入电路发生振荡。等效差分输入电路见图43。

在差分模式下,输入可以交流耦合或直流耦合。单端输入逻辑兼容性见表14。用户可以通过交流或直流耦合到差分输入的一侧,并通过电容将另一侧旁路接地,来实现差分模式下的单端输入。

-

AD9508:低抖动时钟扇出缓冲器的卓越之选2026-03-22 581

-

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要2025-09-16 910

-

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析2025-09-10 1162

-

德州仪器LMX1214射频缓冲器与分频器技术解析2025-09-06 1056

-

LMK01000高性能时钟缓冲器、分频器和分配器数据表2024-08-21 486

-

AD9515 1.6 GHz时钟分配IC,分频器,延迟调整,双输出数据表2021-06-16 836

-

EVAD9508 AD9508评估板2021-06-08 845

-

HMC7043:高性能、3.2 GHz、14输出扇出缓冲器数据表2021-04-28 1583

-

AD9515:1.6 GHz时钟分配IC、分频器、延迟调整、双输出数据表2021-04-13 824

-

AD9512:1.2 GHz时钟分配IC,1.6 GHz输入,分频器,延迟调整,五输出数据表2021-03-22 910

-

AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出2021-03-21 978

-

AD9508 1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整2019-02-22 1004

-

1.65GHz的时钟输出分频器和延迟Fanout Buffer调整ad9508数据表2017-10-19 1223

-

ADI发布新款时钟缓冲器和分频器IC AD95082013-02-21 5035

全部0条评论

快来发表一下你的评论吧 !